Arieh Nachum

Flip-Flops, Registers &

Counters Sequential

Logic Circuits

EB-3153

Arieh Nachum

Flip-Flops, Registers &

Counters Sequential

Logic Circuits

EB-3153

1_9

© All rights reserved to DEGEM Systems.

The material in this book may not be copied, duplicated, printed,

translated, re-edited or broadcast without prior agreement in writing

from DEGEM Systems.

20a Eliyau Eitan St., Rishon-Lezion P.O.Box 5340, Rishon-Lezion 75151 Israel

Tel: 972-3-9535400 Fax: 972-3-9535423

E-mail: info@degem.com Site: www.degem.com

I

Contents

Preface ............................................................................................................III

Experiment 1 – S-R Flip-Flop ........................................................................ 1

1.1

1.2

1.3

S-R Flip-Flop ........................................................................................ 1

Clock Controlled S-R Flip-Flop............................................................ 5

D-Latch Flip-Flop ................................................................................. 6

Experiment 2 – J-K F-F ................................................................................ 15

2.1

2.2

2.3

2.4

2.5

J-K Flip-Flops ..................................................................................... 15

A Clock Controlled J-K Flip-Flop ...................................................... 17

T Flip-Flop .......................................................................................... 18

D Flip-Flop .......................................................................................... 19

Flip-Flops with edge triggering .......................................................... 20

Experiment 3 – Implementing a Register ................................................... 29

3.1

Shift registers ...................................................................................... 29

Experiment 4 – PISO and SIPO Registers.................................................. 38

4.1

4.2

Serial to parallel converter .................................................................. 41

Parallel to serial conversion ................................................................ 42

Experiment 5 – Serial Processing ................................................................ 48

5.1

Serial operations on binary numbers .................................................. 48

Experiment 6 – Ripple Counter ................................................................... 55

6.1

6.2

6.3

6.4

6.5

Count up binary ripple counter ........................................................... 55

Count down binary ripple counter ...................................................... 57

Modulo n and divide by n ................................................................... 58

BCD count up ripple counter .............................................................. 59

Integrated ripple counters ................................................................... 61

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

II

Experiment 7 – Synchronous Counters ...................................................... 67

7.1

7.2

7.3

7.4

7.5

7.6

A binary synchronous counter counting up ........................................ 68

A binary synchronous counter counting up/down .............................. 69

A BCD synchronous counter .............................................................. 70

A programmable synchronous counter ............................................... 71

Integrated synchronous counters......................................................... 73

Counters applications .......................................................................... 73

Experiment 8 – Troubleshooting ................................................................. 84

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

III

Preface

The experiments in this manual are meant to be run on the experiment board

EB-3515 with the Universal Training System EB-3100.

The EB-3100 includes:

5 voltages power supply (+12V, +5V, –5V, –12V and –12V to +12V

variable voltage).

2 voltmeters.

Ampere-meter.

Frequency counters up to 1MHz.

Logic probe (High, Low, Open, Pulse, Memory).

Logic analyzer with 8 digital inputs and trigger input.

Two channel oscilloscope (with spectrum analysis while connecting to the

PC).

Function generator (sine, triangle and square wave signals) up to 1MHz.

3.2" color graphic display with touch panel for signal and measurement

display.

USB wire communication with the PC.

20 key terminal keyboard.

10 relays for switching the plug-in boards or for planting faults.

48 pin industrial very low resistance connector for plug-in boards

connection.

Transparent sturdy cover covers the upper part of the plug-in boards in

order to protect the board's components that should be protected.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

IV

The EB-3100 boards are:

Electricity and Electronics

EB-3121

Ohm and Kirchoff Laws and DC circuits

EB-3122

Norton, thevenin and superposition

EB-3123

AC circuits, signals and filters

EB-3124

Magnetism, electromagnetism, induction and transformers

Semiconductor Devices

EB-3125

Diodes, Zener, bipolar and FET transistors characteristics and DC circuits

EB-3126

Bipolar and FET transistor amplifiers

EB-3127

Industrial semiconductors – SCR, Triac, Diac and PUT

EB-3128

Optoelectronic semiconductors – LED, phototransistor, LDR, 7-SEG.

Linear Electronics

EB-3131

Inverter, non-inverter, summing, difference operational amplifiers

EB-3132

Comparators, integrator, differentiator, filter operational amplifiers

EB-3135

Power amplifiers

EB-3136

Power supplies and regulators

EB-3137

Oscillators, filters and tuned amplifiers

Motors, Generators and Inverters

EB-3141

Analog, PWM DC motor speed control, step motor control, generators

EB-3142

Motor control – optical, Hall effect, motor closed control

EB-3143

AC-DC and DC-AC conversion circuits

EB-3144

3 Phase motor control

Digital Logic and Programmable Device

EB-3151

AND, OR, NOT, NAND, NOR, XOR logic components & Boolean algebra

EB-3152

Decoders, multiplexers and adders

EB-3153

Flip-flops, registers, and counters sequential logic circuits

EB-3154

555, ADC, DAC circuits

EB-3155

Logic families

Microprocessor/Microcontroller Technology

EB-3191

Introduction to microprocessors and microcontrollers

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

V

The EB-3153 is connected to the EB-3100 via a 48 pin industrial connector.

It has a built-in microcontroller that identifies (for the EB-3100 system) the

experiment board when it is being plugged into the system, and starts a selfdiagnostic automatically.

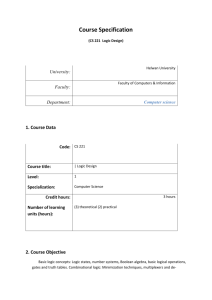

The following figure describes the EB-3153 experiment board.

GATES

0

1

REGISTERS

J

LD

S0

JK – FLIP FLOP

D

Q

JK0

L0

Q'

CP

REG A

0

1

K

CP

S1

J

L1

Q

JK1

LD

0

1

Q'

CP

S2

L2

D

REG B

K

CP

0

1

J

S3

CLR

LD

Q

JK2

Q'

CP

K

Debouncer

CPU

TCU

Counter

CPD

J

TCD

CP

Q

JK3

Q'

K

EB-3153 Panel Layout

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

L3

VI

The experiment method:

The system uses an external switching power supply for safety reasons. The

power supply low voltage output is converted to the 5 voltages by linear

regulators for noise reduction.

Two potentiometers on the panel are used to setup the variable voltage and the

function generator amplitude.

The system cut-off the voltages in overload and displays a massage about that.

The plug-in cards are connected directly to system without any flat cable for

noise and resistance reduction.

The 10 relays are change over relays that can switch active and passive

components.

Every selecting of a relay configuration is saved in a non-volatile memory

located on the connected plug-in card.

The components are located on the board with silk screen print of the

analytical circuit and component symbols. The central part of the

experimenting board includes all the circuit block drawings and all the hands

on components, test points and banana sockets.

The protected components are located on the circuit board upper side, clearly

visible to the student and protected by a sturdy transparent cover.

On plugging the experiment board, it sends a message to the EB-3100 which

includes the board's number and which of its block are faulty. If there is a

faulty module (B1-B8), it will be displayed on the screen.

The experiment board checks itself while it is being plugged. This is why,

during the plug-in, any banana wire should not be connected on the

experiment board.

5 LEDs should turn ON on the top right.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

VII

The system includes 5 power supply outputs. The system checks these

voltages and turns ON the LEDs accordingly.

+12V

+5V

–5V

–12V

–

–

–

–

Red LED

Orange LED

Yellow LED

Green LED

The fifth voltage is a variable voltage (Vvar) controlled by a slider

potentiometer.

The LED of the Vvar is both green and red: when the Vvar voltage is positive

– the color is red and when it is negative – the color is green.

There are no outlets for the power supply voltages on the

The voltages are supplied only to the 48 pin connector.

TSP-3100 panel.

The experiment boards take these voltages from the 48 pin connector.

EB-3100 Screens

The system has 3 operating screens: DVM, Oscilloscope and Faults.

Moving from one screen to another is done by the Options/Graph key.

The keyboard is always at Num Lock position.

The keys can also be used as function keys. In order to do so, we have to press

once on the Num Lock key and then on the required key. The keyboard

returns automatically to Num Lock mode.

On scope screen, pressing the Num Lock key and then the Digital key will

change the screen to Digital signal screen display.

Pressing the Num Lock key and then the Analog key will change the screen to

Analog signal screen display.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

VIII

DVM Screen

DVM

V1 [V]

0.00

V2–V1 [V]

0.00

Fout [KHz]

5.00

V2 [V]

0.00

I [mA]

0.0

Cin [Hz]

5.00

I (+5V) [mA]

I (+12V) [mA]

0

0

I (–5V) [mA]

I (–12V) [mA]

0

0

Num Lock

V1 is the voltage measured between V1 inlet and GND.

V2 is the voltage measured between V2 inlet and GND.

V2–V1 is the voltage measured between V1 and V2. It enables us to measure

floating voltage.

I is the current measured between A+ and A– inlets.

Cin displays the frequency is measured in the Cin inlet.

The EB-3100 includes a function generator.

The frequency of the function generator is displayed in the Fout field and can

be set by the arrow keys or by typing the required values.

The square wave outlet is marked with the sign

.

Near the analog signal outlet there is a sine/triangle switch marked with the

signs

/

.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

IX

Scope Screen

CH1 3.0VCH2

3.0V t 50s

CH1

1.0V

Num Lock Analog Run

The scope and the display parameters (CH1 Volt/div, CH2 Volt/div, time base

Sec/div, Trigger Channel, Trigger rise/fall, Trigger Level) appear on the

bottom of the screen.

The Up and Down arrow keys highlight one of the fields below.

The required field can be selected by touching it and can be changed by the

Up and Down arrows.

The function generator amplitude is changed by the amplitude potentiometer.

The sampling and display can be stopped by pressing the Num Lock key and

then pressing the Stop (8) key.

Performing a single sampling is done by pressing the Num Lock key and then

pressing the Single (9) key.

Running again the sampling is done by pressing the Num Lock key and then

pressing the Run (7) key.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

X

Digital Screen

Pressing the Num Lock key and then the Digital key on scope screen displays

the Digital screen.

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

t 50s

TRIG

Num Lock Digital Run

Check that.

The logic analyzer includes 8 digital inlets and one trigger signal inlet.

The controller waits for trigger and when it encounters a trigger pulse it

samples the 8 digital inputs.

If a trigger pulse is not found the sampling will be according to the time base.

The sampling and display can be stopped by pressing the Num Lock key and

then pressing the Stop (8) key.

Performing a single sampling is done by pressing the Num Lock key and then

pressing the Single (9) key.

Running again the sampling is done by pressing the Num Lock key and then

pressing the Run (7) key.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

XI

Logic Probe

The EB-3100 Logic Probe includes 5 LEDs indicating the Logic Probe (LP)

input state – High, Low, Open (unconnected), Pulses and Memory (registering

single pulse).

The Logic Probe also has a TTL/CMOS switch that determines which logic

level is selected.

When the LP is connected to a point with a voltage blow 0.8V (for TTL) or

1.3V (for CMOS), the L green LED should turn ON.

When the LP is connected to a point with a voltage above 2.0V (for TTL) or

3.7V (for CMOS), the H red LED should turn ON.

The voltage between these levels turns ON the OP orange LED.

Fault Screen

The EB-3100 includes 10 relays for fault insertion or for switching external

components.

The fault screen is selected by the Options/Graph key.

FAULTS

Please choose

Fault No.: 0–9

Activated fault

Number: 0

Num Lock

Typing a fault number and pressing ENTER operates the required relay for the

required fault.

Fault No. 0 means No Fault.

Which relay creates the required fault is registered in the plug-in experiment

board controller.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

XII

On entering a fault number, the system addresses the experiment board

controller and asks for the relay number. After that, it executes the required

fault.

The experiment board controller saves the last registered fault number in its

memory. This memory is non-volatile.

This is why the system does not allow us to enter a fault number when no

experiment board is plugged.

When an experiment board that a certain fault (other than zero) is registered in

its memory is plugged into the system, a warning message appears on the

system's screen.

This feature enables the teacher to supply the students various experiment

boards with planted faults for troubleshooting.

Note:

It is recommended (unless it is otherwise required), to return the

experiment board fault number to zero before unplugging it.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

1

Experiment 1 – S-R Flip-Flop

Objectives:

After completing this experiment explain:

The S-R F-F and its implementations.

Clock control S-R F-F.

D-Latch.

Equipment required:

EB-3100

EB-3153

Banana wires

Discussion:

1.1

S-R Flip-Flop

The flip-flops are the most basic memory units. Their function is to remember

a certain state in the inputs, even if this state has been changed.

The S-R flip-flop is an elementary F-F circuit having 2 inputs and 2 outputs.

This circuit can be materialized using two NOR gates or two NAND gates.

The two outputs function as complementary outputs Q and Q . Each gate

functions simultaneously as a combinatorial system and a feedback source.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

2

First we will examine a S-R F-F with NOR gates:

R (Reset)

Q

S (Set)

Q

Figure 1-1 S-R F-F with NOR gates

Here is the table of states of this circuit:

S

RESET condition

0

S,R=0,0 after S,R=0,1 0

SET condition

1

S,R=0,0 after S,R=1,0 0

Forbidden state

1

R

1

0

0

0

1

Q Q

0 1

0 1

1 0

1 0

0 0

Check that this table is correct.

We may observe a number of nuances:

1.

When R=1, the output Q is 0. This is why this input is called RESET. It

is sometimes also called CLEAR.

2.

When S=1, output Q will be 1 provided that R is not 1.

3.

In the 0,0 state of the inputs, the circuit remembers the previous state. If

the previous state was S,R=0,1, then when the input states revert to

S,R=0,0, the output state Q, Q =1,0 will be maintained.

We can see how the output is dependent on the inputs and on its own

previous state. Lowering an input to '0' does not affect the outputs

(provided that the other input is '0'), due to the feedback from output to

input.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

3

4.

The S,R=1,1 condition is forbidden for two reasons:

a)

One reason is that in this state the outputs do not complement each

other. They will both be '0'.

b)

The second and main reason is that it is impossible to predict how

the circuit will behave in the transition from S,R=1,1 to S,R=0,0.

One input will always sink first to '0' (which will be first is not

predictable) and so the output result will be established randomly,

which is an unacceptable situation in logic circuits.

The S-R F-F materialized with NOR gates and is operated using positive

logic. '1' on "R" clears the output Q, and '1' on "S" sets the output Q to '1'.

The S-R F-F materialized with NAND gates looks like this:

S

Q

R

Q

Figure 1-2 S-R F-F with NAND gates

This circuit operates with negative logic. Here is its truth table:

S

RESET condition

1

S,R=1,1 after S,R=0,1 1

SET condition

0

S,R=1,1 after S,R=1,0 1

Forbidden state

0

R

0

1

1

1

0

Q Q

0 1

0 1

1 0

1 0

1 1

Check that this table is correct.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

4

We can observe the following nuances:

1.

When R=0 then Q=0 provided that S does not equal 0. This is the RESET

(CLEAR) condition.

2.

When S=0 then Q=1 provided that R does not equal 0. This is the SET

condition.

3.

In this case, the circuit remembers the previous output state when

S,R=1,1.

4.

The condition where S,R=0,0 is a forbidden state for the same reasons

described regarding the NOR gate materialization approach.

To get the same behavior as the NOR gates SR-FF, we add inverters to the

inputs.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

5

1.2

Clock Controlled S-R Flip-Flop

A clock controlled S-R F-F can be seen in this diagram:

R

Q

CP

S

Q

Figure 1-3 A clock controlled S-R F-F

When CP=0 the state of the inputs S and R is disregarded. The inputs to the

NOR gate will always be '0' and in this condition the F-F retains the state of its

outputs.

When CP=1, the F-F reacts to the state of the inputs S-R according to the table

of states shown here:

CP

0

1

1

1

1

S

x

0

0

1

1

R

Q

x

Q0

Q1

0

0

1

1 forbidden state

In this way, we can control the F-F, so that it will only react when we allow

this by operating the CP line (raising it to '1'). We can latch the output by

lowering CP to '0'.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

6

1.3

D-Latch Flip-Flop

In the previous paragraph we have seen that even when we add a clock control

line to a S-R F-F, we still have not overcome the problem of the forbidden

S,R=1,1 input state. The following component is one solution to this problem.

D

Q

CP

Q

Figure 1-4 D-Latch

To overcome the S,R=1,1 state we use an input, called D, which is split up by

an inverter into the S and R inputs. The following table of states now applies:

CP

0

0

1

1

D

0

1

0

1

S

0

0

0

1

R Q+

0 Q0 Q1 0

0 1

We can observe that Q=D when CP=1. When CP=0 then S,R=0,0 regardless

of D and so the output state prevailing when CP is lowered to 0 will be

retained. There is no forbidden state in this table.

The D input behaves as a kind of data input. The incoming data will be

transferred to the output when CP=1 and will be latched there when CP sinks

to 0. For this reason we call this component a D-Latch. When CP=1 the

changes on the input will appear at the output.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

7

Preparation questions:

1.

What is the forbidden state of the following circuit?

(a)

(b)

(c)

(d)

2.

R (Reset)

Q

S (Set)

Q

00

01

10

11

What is the forbidden state of the following circuit?

(a)

(b)

(c)

(d)

S

Q

R

Q

00

01

10

11

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

8

3.

What is the state of the outputs Q and Q at the inputs state

CP,R,S = 1,1,0 of the following circuit?

R

Q

CP

S

(a)

(b)

(c)

(d)

4.

Q

00

01

10

11

What is the state of the outputs Q and Q at the inputs state CP,D = 1,1 of

the following circuit?

D

Q

CP

Q

(a)

(b)

(c)

(d)

00

01

10

11

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

9

Procedure:

Step 1:

Connect the EB-3100 to the power supply.

Step 2:

Connect the power supply to the Mains.

Step 3:

Turn ON the trainer. The DVM screen should appear on the display.

Step 4:

Plug the EB-3153 into the EB-3100.

Step 5:

Observe the display and check that the experiment board name

appear and no fault is detected.

Step 6:

Implement the following S-R F-F:

R (Reset)

Q

S (Set)

Q

Step 7:

Connect the inputs S,R to the switches S1,S0 accordingly.

Step 8:

Connect the outputs Q, Q to the LEDs L1,L0 accordingly.

Step 9:

Change the switches according to the following table and fill it up.

S

0

0

1

0

R Q Q

1

0

0

0

Draw your conclusion about the outputs' status when the inputs'

status is 0,0.

Step 10: Raise the two input switches. The status of Q1,Q0 should go to 0,0.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

10

Step 11: Drop the two switches together to 0,0 (the memory state of the

F-F).

Do it a number of times.

You will find that the output will act differently. Explain that.

Step 12: Connect the two inputs together to the S0 switch.

Step 13: Raise this switch and lower it to '0'.

Do it several times.

Draw your conclusions.

Step 14: Materialize the following S-R F-F.

S

Q

R

Q

Step 15: Connect the inputs S,R to the switches S1,S0 accordingly.

Step 16: Connect the outputs Q, Q to the LEDs L1,L0 accordingly.

Step 17: Change the switches according to the following table and fill it in.

S

1

1

0

1

R Q Q

0

1

1

1

Draw your conclusions about the outputs' status when the inputs'

status is 1,1.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

11

Step 18: Add two inverters to the inputs of the NAND SR-FF.

Step 19: Change the switches according to the following table and fill it in.

S

0

0

1

0

R Q Q

1

0

0

0

Draw your conclusions regarding the circuit behavior.

Step 20: Materialize the following circuit (described in figure 1-3).

R

Q

CP

S

Q

Step 21: Connect the inputs CP and S,R to the switches S2,S1,S0

accordingly.

Step 22: Connect the outputs Q, Q to the LEDs L1,L0.

Step 23: Change the switches according to the following table and fill it in.

CP

1

0

0

0

0

1

0

0

0

0

S

0

0

0

1

1

1

1

0

0

1

R Q Q

1

1

0

0

1

0

0

0

1

1

Write your conclusions on the results.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

12

Step 24: Materialize the circuit described below.

D

Q

CP

Q

Step 25: Connect the inputs CP and D to the switches S1,S0 accordingly.

Step 26: Connect the outputs Q, Q to the LEDs L1,L0.

Step 27: Change the switches according to the following table and fill it in.

CP

0

1

0

0

1

0

D Q Q

0

0

0

1

1

1

Write your conclusions on the results.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

13

Summary questions:

1.

What is the forbidden state of the following circuit?

(a)

(b)

(c)

(d)

2.

R (Reset)

Q

S (Set)

Q

00

01

10

11

What is the forbidden state of the following circuit?

(a)

(b)

(c)

(d)

S

Q

R

Q

00

01

10

11

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

14

3.

What is the state of the outputs Q and Q at the inputs state CP,R,S =

1,1,0 of the following circuit?

R

Q

CP

S

(a)

(b)

(c)

(d)

4.

Q

00

01

10

11

What is the state of the outputs Q and Q at the inputs state CP,D = 1,1 of

the following circuit?

D

Q

CP

Q

(a)

(b)

(c)

(d)

00

01

10

11

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

15

Experiment 2 – J-K F-F

Objectives:

After completing this experiment explain:

The J-K F-F and its implementations.

Clock controlled J-K F-F.

T F-F implementation.

D F-F implementation.

Equipment Required:

EB-3100

EB-3153

Banana wires

Discussion:

2.1

J-K Flip-Flops

A J-K F-F is an improved version of the S-R F-F. In this case, the forbidden

undefined state has been eliminated and now becomes a defined state.

The J-K F-F behaves similarly to the S-R F-F (J functions as S and K

functions as R) with the exception of the forbidden state. This state now

becomes the condition in which the J-K F-F outputs change from their

previous state to a new state. The improvement is made with an additional

feedback.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

16

The J-K F-F described here uses NOR gates:

K

R

Q

J

S

Q

Figure 2-1 J-K Flip-Flop using NOR gates

Here is the table of states for this circuit:

After J,K=0,1

After J,K=1,0

After Q, Q =1,0

After Q, Q =0,1

J

0

0

1

0

1

1

K

1

0

0

0

1

1

Q Q

0 1

0 1

1 0

1 0

0 1

1 0

If we define Q+ as the state of Q after a change takes place on the inputs, and

Q- as the state of Q before the change on the inputs, we can now write down

the following table:

J

0

0

1

0

K Q+

0 Q1 0

0 1

1 Q-

Note what happens on the inputs S and R when the inputs J and K change. For

example, when J-K changes from J,K=0,0 to J,K=0,1.

When J,K=0,1 there are two possibilities. The one is when Q- = 1. In this case,

R will be '1' and Q will be forced to 0. S will be 0 and so along with Q (which

has gone low) will cause Q to rise to '1'.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

17

The second case is when Q- = 0. In this case, R will be '0' and S will be '0' i.e.

no change will take place on the outputs - Q will remain at '0' according to the

table of states.

The interesting situation is when J,K=1,1. Let us assume that Q- is also '1'.

When this state is transferred to the inputs J,K, the feedback will result in

S,R=0,1 (considering that Q=1 and Q =0). This condition on the S-R inputs

will lower Q to 0 and raise Q to '1'.

If the inputs J,K remain at 1,1 with Q now being '0', we will see the condition

S,R=1,0 on the S,R inputs (this time Q, Q =0,1). This condition will cause an

additional state change on Q from '0' to '1' and on Q from '1' to '0'.

Hence we see that as long as J,K are 1,1, the outputs will oscillate, constantly

changing their state. The time delay between state changes depends on the

propagation delay of the components. How to solve this oscillation problem is

described in the following sections.

2.2

A Clock Controlled J-K Flip-Flop

A clock controlled J-K F-F is materialized in the following way:

K

Q

CP

J

Q

Figure 2-2 A clock controlled J-K F-F

This component functions as a J-K F-F when CP=1. While CP=0 the circuit

switches into its memory condition having no dependence on the inputs and

outputs (S,R=0,0).

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

18

We must bear in mind that the problems of asynchronousness and oscillations,

when J,K=1,1 and CP=1 still appear here (see section 8.2.1). If we require Q

to change its state, we can place 1,1 on J-K and provide a very short pulse on

the clock input CP. i.e. we raise it to '1' for a briefer period than the

propagation time of the components, and than lower it back to '0'. This pulse

will cause one change in the output state.

This is a tall order. The component propagation time tends to vary from one

family of components to the next and correct design procedures dictate that we

avoid this sort of marginal design technique. As we go on, we will meet some

preferable solutions.

2.3

T Flip-Flop

This is a J-K type F-F, which its inputs shorted together.

T

Q

CP

Q

Figure 2-3 T type F-F

When T=0 the output is stable and does not change even if CP changes.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

19

When T=1 and a narrow pulse is supplied to the clock input, the output

changes its state. If a series of pulses is supplied, the following timing diagram

will result (provided that T=1).

CP

Q

Figure 2-4 Timing diagram while T=1

We can see that Q indicates the time which lapses between two clock pulses.

The T F-F is in fact used in counters and timing devices, as we will discover

in later sections of this book. For this reason this F-F is called a T (Time) F-F.

2.4

D Flip-Flop

This is a J-K type F-F, which its inputs are always inverted.

D

Q

CP

Q

Figure 2-5

When CP=0, the outputs keep their previous condition.

When CP=1, the outputs change according to the input D condition.

If D=0, then Q=0.

If D=1, then Q=1.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

20

2.5

Flip-Flops with edge triggering

There is a problem, in all the flip-flops we described, if the clock pulse is too

long. Analyze what is the problem in every flip-flop we described.

In order to overcome these problems, we improve the feed back circuit. There

are several methods. In EB-3153, we use the 74107 component, which is

described in the following figure.

1

1

12

4

2

Q

J

3

CP

K CD Q

2

Q

5

K CD Q

6

8

J

9

CP

11

13

10

VCC = 14

GND = 7

Figure 2-6

This component behaves according to the state table of the JK-FF only in a

transition time of the clock signal (CP) from High to Low. In the High or Low

time of the clock, the component's outputs do not change. In order for them to

change, the clock signal should rise to High and drop to Low. This kind of

clock triggering is called "Edge Triggering".

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

21

Preparation questions:

1.

What is the memory state of the following circuit?

(a)

(b)

(c)

(d)

2.

K

R

Q

J

S

Q

00

01

11

10

What happens to Q when CP,J,K = 1,1,1 in the following circuit?

K

Q

CP

J

(a)

(b)

(c)

(d)

Q

Q=0

Q=1

Q = Q–

Q= Q

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

22

3.

What happens to Q when CP,T = 1,0 in the following circuit?

T

Q

CP

Q

(a)

(b)

(c)

(d)

Q=0

Q=1

Q = Q–

Q= Q

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

23

Procedure:

Step 1:

Connect the EB-3100 to the power supply.

Step 2:

Connect the power supply to the Mains.

Step 3:

Turn ON the trainer. The DVM screen should appear on the display.

Step 4:

Plug the EB-3153 into the EB-3100.

Step 5:

Observe the display and check that the experiment board name

appear and no fault is detected.

Step 6:

Implement the following J-K F-F.

K

R

Q

J

S

Q

Step 7:

Connect the inputs J,K to the switches S1,S0 accordingly.

Step 8:

Connect the outputs Q, Q to the LEDs L1,L0 accordingly.

Step 9:

Change the switches according to the following table and fill it in.

J

0

0

1

0

K Q Q

1

0

0

0

Draw your conclusion about the outputs' status when the inputs'

status is 0,0.

Step 10: Raise the two input switches. What is the status of the outputs.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

24

Step 11: Drop the two switches together to 0,0 (the memory state of the F-F).

Do it a number of times.

You will find that the output will act differently. Explain that.

Step 12: Connect the two inputs together to the S0 switch.

Step 13: Raise this switch and lower it to '0'.

Do it several times.

Draw your conclusions.

Step 14: Materialize the following clock controlled J-K F-F.

Use two AND gates with 2 inputs to implement a 3 inputs AND

gate.

K

Q

CP

J

Q

Step 15: Connect the inputs CP and J,K to the switches S2,S1,S0

accordingly.

Step 16: Connect the outputs Q, Q to the LEDs L1,L0.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

25

Step 17: Change the switches according to the following table and fill it in.

CP

1

0

0

0

0

1

0

0

0

0

J

0

0

0

1

1

1

1

0

0

1

K Q Q

1

1

0

0

1

0

0

0

1

1

Write your conclusions on the results.

Step 18: Materialize the circuit described below.

T

Q

CP

Q

Step 19: Connect the inputs CP and T to the switches S1,S0 accordingly.

Step 20: Connect the outputs Q, Q to the LEDs L1,L0.

Step 21: Change the switches according to the following table and fill it in.

CP

0

1

0

0

1

0

T Q Q

0

0

0

1

1

1

Write your conclusions on the results.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

26

Step 22: EB-3153 includes 4 IC’s JK-FF based on two 74107. These flipflops have clear input, which are all connected to the C banana

socket below.

Connect J, K, CP, C inputs to S0, S1, S2, S3 switches accordingly.

Step 23: Raise C to '1'.

Step 24: Lower C to '0' and raise it to '1'.

Step 25: Change the switches according to the following table and fill it in.

CP

1

0

0

0

0

1

0

0

0

0

J

0

0

0

1

1

1

1

0

0

1

K Q Q

1

1

0

0

1

0

0

0

1

1

Write your conclusions on the results.

Step 26: Raise the J,K inputs to '1'

Step 27: Change CP input to '1' and to '0' several times. Observe the outputs.

Step 28: EB-3153 has a clock generator. Its frequency is controlled by a

potentiometer.

Disconnect the J-K F-F CP input from S2 and connect it to the

output of the clock generator.

Step 29: Raise the J,K inputs to 1,1 and observe the J-K F-F outputs.

What is the frequency of the Q outputs of the J-K F-F?

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

27

Summary questions:

1.

What is the memory state of the following circuit?

(a)

(b)

(c)

(d)

2.

K

R

Q

J

S

Q

00

01

11

10

What happens to Q when CP,J,K = 1,1,1 in the following circuit?

K

Q

CP

J

(a)

(b)

(c)

(d)

Q

Q=0

Q=1

Q = Q–

Q= Q

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

28

3.

What happens to Q when CP,T = 1,0 in the following circuit?

T

Q

CP

Q

(a)

(b)

(c)

(d)

Q=0

Q=1

Q = Q–

Q= Q

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

29

Experiment 3 – Implementing a Register

Objectives:

After completing this experiment explain:

How to accomplish a shift register with JK-FF.

How to accomplish a ring counter.

How to accomplish a switched tail ring counter.

How to accomplish a pseudo random binary sequence generator.

Equipment Required:

EB-3100

EB-3153

Banana wires

Discussion:

3.1

Shift registers

In addition to parallel loading registers, there are registers in which the binary

data can be shifted to the left or to the right. These are called Shift Registers.

A shift register is made up of a chain of Flip-Flops connected to each other in

series, so that the output from each F-F is connected to the input of the next FF in the series. All the Flip-Flops are connected to a common clock input so

that a single clock pulse causes data to be shifted all the way down the line

simultaneously.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

30

A simple shift register looks like this:

SI

Serial In

D

CLK

Q

D

CLK

Q

D

CLK

Q

D

Q

SO

Serial Out

CLK

CP

Figure 3-1 A simple 4-bit shift register

The input to the leftmost cell serves as an input for the entire register.

The output from the rightmost cell is the output from the entire register.

Four clock pulses are required to shift data from the input to the output.

Each clock pulse causes a shift of one place to the right. The terms left and

right are a bit misleading. If we turned the component the other way around or

looked at it in a mirror, we would be shifting from right to left.

The number of components in a package depends on the required number of

pins. It is easy to compress a large number of simple shift registers into one

package, as each register requires very few pins.

Data is transferred from one shift register to another serially. Very few lines

are required. In fact, only two lines, DATA IN and CLOCK, are required.

However, it is necessary to create a clock generator, which will supply the

correct number of pulses required to shift the data through the component (for

example 8 clock pulses in an 8-bit shift register).

On the other hand, far more time is required to transfer data serially than is

required for parallel transfer.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

31

For example, shifting data from one register to another (without changing the

source register) is described in the following figure:

SI

SO

SI

SO

B

A

CLK

CLK

CP

Figure 3-2 Serial transfer of data from one register to another

The number of clock cycles required equals the number of register bits.

This system is called SISO (Serial In Serial Out) system.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

32

Preparation questions:

1.

In the following circuit S0 is raised ('1').

S0

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

Q

CP

C

Q

K

Q

J

Q

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

2.

0000

1000

0001

1111

In the following circuit the outputs' state is 0001.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

CP

C

Q

K

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

0000

1000

0001

1111

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

33

3.

In the following circuit the outputs' state is 0001.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

CP

C

Q

K

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

Q

0000

1000

0001

1111

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

34

Procedure:

Step 1:

Connect the EB-3100 to the power supply.

Step 2:

Connect the power supply to the Mains.

Step 3:

Turn ON the trainer. The DVM screen should appear on the display.

Step 4:

Plug the EB-3153 into the EB-3100.

Step 5:

Observe the display and check that the experiment board name

appear and no fault is detected.

Step 6:

Implement the following circuit:

S0

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

Q

CP

C

Q

K

S7

P0

Step 7:

Raise S7 and lower it to '0' once.

Step 8:

Raise S0 to '1'.

Step 9:

Press P0 four times and observe the J-K F-F behavior.

Step 10: Drop down S0 to '0'.

Step 11: Press P0 four times and observe the J-K F-F behavior.

Step 12: Raise S0 to '1' and press P0 once.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

35

Step 13: Take the wire off from S0 and connect it to the Q output of the

rightmost JK-FF.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

Q

CP

C

Q

K

Q

S7

P0

Step 14: Press P0 several times and observe the JK-FF behavior.

Record 5 states of the outputs.

Step 15: Take the wire from P0 and connect it to the clock generator output.

You accomplished a ring counter.

Step 16: Take off the wire from the rightmost Q output and connect it to its

Q output. Observe the output signals.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

Q

CP

C

Q

K

S7

P0

You have accomplished a switched tail ring counter.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

36

Summary questions:

1.

In the following circuit S) is raised ('1').

S0

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

Q

CP

C

Q

K

Q

J

Q

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

2.

0000

1000

0001

1111

In the following circuit the outputs' state is 0001.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

CP

C

Q

K

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

0000

1000

0001

1111

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

37

3.

In the following circuit the outputs' state is 0001.

Q

J

CP

K

Q

J

CP

C

Q

K

Q

J

CP

C

Q

K

J

CP

C

Q

K

S7

P0

What will be the outputs' state after pressing P0 four times?

(a)

(b)

(c)

(d)

Q

0000

1000

0001

1111

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q

38

Experiment 4 – PISO and SIPO Registers

Objectives:

After completing this experiment explain:

The register's functions parallel in and out, serial in and out.

How to transfer data from one register to another.

How to connect a PISO register to a SIPO one.

Equipment Required:

EB-3100

EB-3153

Banana wires

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

39

Discussion:

In this experiment, we will use the register 74194.

In this sort of register, data can be shifted serially (in some it is also possible

to govern the direction - left or right). Data can be loaded into the register in

parallel format and can also be read from the register in parallel.

We will describe the 74194 shift register which is called a universal 4-bit

register. This register provides all the possible options: Parallel In, Parallel

Out, Serial In, Serial Out, Chip Reset, Shift Right and Shift Left, and even a

Disable Function which allows the outputs to remain unchanged even while

clock pulses appear.

1

MR'

Vcc

16

2

DSR

Q0

15

3

P0

Q1

4

P1

Q2

14

13

5

P2

Q3

12

Operating

Mode

Reset

Hold

Shift Left

6

P3

CP

11

Shift Right

7

DSL

GND

S1

10

S2

9

8

Parallel Load

Mode Select – Truth Table

Inputs

MR' S1 S0 DSR DSL Pn

L

x

x

x

x

x

H

l

l

x

x

x

H

h

l

x

l

x

H

h

l

x

h

x

H

l

h

l

x

x

H

l

h

h

x

x

H

h

h

x

x

Pn

Q0

L

Q0

Q1

Q1

L

H

P0

Outputs

Q1 Q2

L

L

Q1 Q2

Q2 Q3

Q2 Q3

Q0 Q1

Q0 Q1

P1 P2

Figure 4-1 Pinout and truth table of the 74194

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

Q3

L

Q3

L

H

Q2

Q2

P3

40

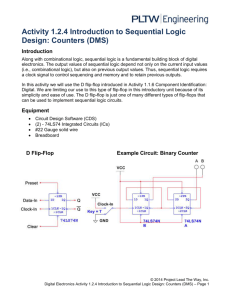

The following figure will help us to understand how this component works:

Logic Diagram

P0

P1

P2

4

3

10

P3

6

5

S1

9

S0

7

2

DSR

DSL

VCC = Pin 16

GND = Pin 8

= Pin No.

S

Q0

S

S

Q2

S

CP

CP

CP

CP

R

R

R

R

CLEAR

CP

Q1

CLEAR

CLEAR

Q3

CLEAR

11

1

MR'

15

Q0

12

13

14

Q1

Q2

Q3

Figure 4-2 Description of a universal shift register circuit

The inputs S1,S0 set the component's operation mode, and the data flow mode, according to

the following table:

S1 S0 Function

0 0 No change on outputs (clock disable mode)

0 1 Shift right

1 0 Shift left

1 1 Parallel loading

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

41

4.1

Serial to parallel converter

A shift register which has a serial input and parallel F-F outputs is called SIPO

(Serial In Parallel Out). This is a device, which converts serial data to parallel

format.

We often transfer data between systems in serial form, to save on transmission

lines, but the actual data processing is in parallel, so the data must be

converted to parallel form.

An 8 bit shift register with serial input and parallel outputs is the 74164.

1

A

VCC

14

2

B

Q7

13

3

Q0

Q6

4

Q1

Q5

12

11

5

Q2

6

7

Mode Select – Truth Table

Operating Mode

Inputs

MR' A B Q0

L

x x

L

Reset (Clear)

H

l

l

L

Shift

H

l h

L

H

h l

L

H

h h H

10

Q4

Q3

MR'

P

GND CP

9

8

Outputs

Q1-Q7

L-L

Q0-Q6

Q0-Q6

Q0-Q6

Q0-Q6

Logic Diagram

1

A

B

Q

D

2

D

CD

Q

D

CD

Q

D

CD

Q

D

CD

Q

D

CD

Q

D

CD

Q

D

CD

Q

CD

8

CP

MR'

9

3

VCC = Pin 14

GND = Pin 7

= Pin No.

Q0

4

Q1

5

Q2

6

Q3

10

Q4

11

Q5

12

Q6

13

Q7

Figure 4-3 Pinout and truth table of the 74164

This register contains 8 D F-F's. The outputs of these registers are connected

to the component pins. The register also has a CLEAR pin, which clears all of

the Flip-Flops simultaneously, and a CLK line common to all the Flip-Flops.

The chip has two serial inputs, which are connected via AND gate to the serial

input of the first F-F. Both of these inputs (A and B) must be '1' when a clock

pulse appears, for the first F-F to register '1'.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

42

4.2

Parallel to serial conversion

This kind of register, which is loaded in parallel and outputs its data in serial

form (PISO - Parallel In Serial Out), can be materialized using a universal

register. Initially the data to be transferred is loaded in parallel. Then the

register is switched to serial mode and a series of clock pulses is supplied to

advance the data.

We will materialize a circuit, which receives parallel data from 8 switches,

and transmits this data in serial form. The serial data will be received by a

shift register, which will then output it in parallel to 8 LEDs.

The following figure is a block diagram of this system:

SO

Load

PISO A

Clock

Generator

SI

SIPO B

Save

Figure 4-4 Serial transmission of parallel data

The pulse generator first creates a "LOAD" pulse, and the state of the switches

is loaded into register A. Then a series of 8 clock pulses causes the data to be

transferred in serial form from register A to register B. A final "SAVE" pulse

latches the data in the serial register B outputs.

Although the two systems are connected by only 3 wires, we have created a

completely transparent system. Any change on the switches will immediately

be displayed on the LEDs. The SAVE line could be eliminated if the clock

generator were to send 9 pulses, and the receiver would have a counter circuit

which would create a SAVE pulse on the 9th clock pulse.

A system of this kind is invaluable when there is a large distance between the

receiver and the transmitter, and we need to avoid expensive wiring between

these units.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

43

Preparation questions:

1.

The state of the switches in the following circuit is 0011.

L0

L1

L2

L3

VCC

15 14

13 12

1 2 10 16

QH QB QC QD

7

11

D

REGA

74194

CP

3

4

5

6

8

P0

S0

S1

S2

S3

9

LD

What will be the state of the outputs after we press LD and click on P0?

(a)

(b)

(c)

(d)

2.

What will be the outputs' state after clicking P0 twice?

(a)

(b)

(c)

(d)

3.

1100

0011

0000

1111

1100

0011

0000

1111

What is the meaning of PISO register?

(a)

(b)

(c)

(d)

Parallel In Parallel Out

Serial In Serial Out

Parallel In Serial Out

Serial In Parallel Out

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

44

4.

What is the meaning of SIPO register?

(a)

(b)

(c)

(d)

Parallel In Parallel Out

Serial In Serial Out

Parallel In Serial Out

Serial In Parallel Out

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

45

Procedure:

Step 1:

Connect the EB-3100 to the power supply.

Step 2:

Connect the power supply to the Mains.

Step 3:

Turn ON the trainer. The DVM screen should appear on the display.

Step 4:

Plug the EB-3153 into the EB-3100.

Step 5:

Observe the display and check that the experiment board name

appear and no fault is detected.

On the circuit, there are two registers – REGA and REGB. They are

bi-directional parallel load shift register. We can use them here only

as shift right registers.

Step 6:

Implement the following circuit:

L0

L1

L2

L3

VCC

15 14

13 12

1 2 10 16

QH QB QC QD

7

11

D

REGA

74194

CP

3

4

5

6

8

P0

Step 7:

S0

S1

S2

S3

9

LD

Change the switches of REGA to show the number 0011.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

46

Step 8:

Press LD and keep it pressed while pressing and releasing the P0

pushbutton.

This creates a clock pulse and the parallel switch input status will

appear on the LED outputs of REGA.

Step 9:

Repeat steps 4 and 5 with different numbers.

Step 10: Do steps 4 and 5 with the number 1000.

Step 11: Press only the P0 pushbutton several times to create clock pulses

and observe the LED outputs.

Record 5 states of the outputs.

You implemented a ring counter.

Step 12: Also connect the input of REGB to P0.

Step 13: Take off the wire from the D input of REGA and connect it to the D

input of REGB. That way REG A output will be serial connected to

REG B input.

Step 14: Connect the Y0 output of REGB to the D input of REGA.

Step 15: Change the switches of REGB to display the number 0000.

Step 16: Press the LD pushbutton of REGA and while it is pressed, press P0

once.

Step 17: Change the switches of REGA to display the number 1000.

Step 18: Press the LD pushbutton of REGB and while it is pressed, press P0

once.

Step 19: Press the pushbutton P0 several times and observe the LEDs. We

have now an 8-bit ring counter.

Step 20: Repeat steps 15-19 with different numbers.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

47

Summary questions:

1.

The state of the switches in the following circuit is 0011.

L0

L1

L2

L3

VCC

15 14

13 12

1 2 10 16

QH QB QC QD

7

11

D

REGA

74194

CP

3

4

5

6

8

P0

S0

S1

S2

S3

9

LD

What will be the state of the outputs after we press LD and click on P0?

(a)

(b)

(c)

(d)

2.

What will be the outputs' state after clicking P0 twice?

(a)

(b)

(c)

(d)

3.

1100

0011

0000

1111

1100

0011

0000

1111

How many clock pulses are needed to transfer the full data from REGA

to REGB?

(a)

(b)

(c)

(d)

1

2

4

5

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

48

Experiment 5 – Serial Processing

Objectives:

After completing this experiment explain:

How to implement serial processing between two digital numbers.

Other application of shift registers.

Equipment Required:

EB-3100

EB-3153

Banana wires

Discussion:

5.1

Serial operations on binary numbers

Sometimes we need to perform arithmetic or logic operations on binary

numbers. These operations are performed separately on corresponding pairs of

bits.

For example, let us assume that we have two 8-bit binary numbers, A and B.

A=01011011

B=11001010

A logical AND function performed on these two numbers will also result in an

8-bit number, in the following way:

A = 01011011

B = 11001010

Y = 01001010 Y = A B

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

49

To materialize this function we would require 8 AND gates in the following

configuration:

B7 A7 B6 A6 B5 A5 B4 A4 B3 A3 B2 A2 B1 A1 B0 A0

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

Figure 5-1 Performing an AND operation in parallel

Remember that A and B are stored in parallel registers.

Using shift registers, it is possible to save gates by using only 1 AND gate in

this way:

SI

Shift Register A

SO

CLK

SI

Shift Register B

CP

SO

CLK

Figure 5-2 Performing a serial AND operation

The clock generator must provide 8 clock pulses (assuming that we are

dealing with 8-bit registers). The result of the operation will be fed back into

register A. The previous data in A and B disappears. If we wished to retain the

data in B, we would simply connect the serial input of B to its serial output.

In this fashion, we could construct an entire ALU (Arithmetic Logic Unit) in a

most economical way. The difficulty here would be to construct an 8 pulse

clock generator, and processing time is the duration of 8 clock pulses.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

50

An additional example, which requires a memory element to assist in

performing a calculation, is binary addition described in the following figure:

SI

Shift Register A

SO

Y

X

Y

SI

Shift Register B

SO

FA

Z

C

Q

D

C

CP

Figure 5-3 Serial addition of binary numbers

Here we use one FA and a D F-F to store the carry, which results from the last

two bits added.

Before performing this addition, the D F-F must be cleared.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

51

Preparation questions:

1.

In the following circuit the data of REGA is 1010 and the data in REGB

is 0000.

D

Shift Register A

Y0

Shift Register B

Y0

CP

D

P0

CP

What will be the data in REGA after 4 clock pulses?

(a)

(b)

(c)

(d)

2.

0001

1111

0111

1011

In the above circuit the data of REGA is 1010 and the data in REGB is

0000.

What will be the data in REGA after 3 clock pulses?

(a)

(b)

(c)

(d)

3.

0001

1111

0111

1011

If we replace the NAND gate with a NOR gate in the above circuit, what

will be the data in REGA after 4 clock pulses?

(a)

(b)

(c)

(d)

0001

1111

0111

1011

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

52

Procedure:

Step 1:

Connect the EB-3100 to the power supply.

Step 2:

Connect the power supply to the Mains.

Step 3:

Turn ON the trainer. The DVM screen should appear on the display.

Step 4:

Plug the EB-3153 into the EB-3100.

Step 5:

Observe the display and check that the experiment board name

appear and no fault is detected.

Step 6:

Implement the following circuit:

D

Shift Register A

Y0

Shift Register B

Y0

CP

D

P0

CP

Step 7:

Change REGA parallel input switches to show the number 1010.

Step 8:

Press LD and keep it pressed while pressing and releasing the P0

pushbutton.

This creates a clock pulse and the parallel switch input status will

appear on the LED outputs of REGA.

Step 9:

Change REGB parallel input switches to show the number 1100.

Step 10: Press LD and keep it pressed while pressing and releasing the P0

pushbutton.

Step 11: Lower the L switch to '0' in both registers.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

53

Step 12: Press P0 four times while observing the lights on each register.

What is the result after the fourth time?

Does it suit the state table of the NAND gate?

Step 13: Replace the NAND gate with NOR gate.

Step 14: Change REGA parallel input switches to show the number 1010.

Step 15: Press LD and keep it pressed while pressing and releasing the P0

pushbutton.

This creates a clock pulse and the parallel switch input status will

appear on the LED outputs of REGA.

Step 16: Change REGB parallel input switches to show the number 1100.

Step 17: Press LD and keep it pressed while pressing and releasing the P0

pushbutton.

Step 18: Lower the L switch to '0' in both registers.

Step 19: Press P0 four times while observing the lights on each register.

What is the result after the fourth time?

Does it suit the state table of the NOR gate?

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

54

Summary questions:

1.

In the following circuit the data of REGA is 1010 and the data in REGB

is 0000.

D

Shift Register A

Y0

Shift Register B

Y0

CP

D

P0

CP

What will be the data in REGA after 4 clock pulses?

(a)

(b)

(c)

(d)

2.

0001

1111

0111

1011

In the above circuit the data of REGA is 1010 and the data in REGB is

0000.

What will be the data in REGA after 3 clock pulses?

(a)

(b)

(c)

(d)

3.

0001

1111

0111

1011

If we replace the NAND gate with a NOR gate in the above circuit, what

will be the data in REGA after 4 clock pulses?

(a)

(b)

(c)

(d)

0001

1111

0111

1011

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

55

Experiment 6 – Ripple Counter

Objectives:

After completing this experiment explain:

How to implement an up count binary ripple counter with JK flip flops.

How to implement a down count binary ripple counter with JK flip flops.

How to implement a BCD count ripple counter with JK flip flops.

Equipment Required:

EB-3100

EB-3153

Banana wires

Discussion:

6.1

Count up binary ripple counter

Counters are materialized with T-Flip-Flops, which are J-K Flip-Flops with

two inputs connected to VCC (constantly '1') in the following fashion:

QA

VCC

VCC

J

CLOCK

QB

Q

CLK

K

J

Q

K

J

Q

CLK

Q

QD

VCC

VCC

CLK

Q

QC

K

J

Q

CLK

Q

K

Q

Figure 6-1 4-bit count up binary ripple counter

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

56

The clock input to each F-F is marked with a circle. This means that the F-F

is triggered when the signal at its clock input sinks from '1' to '0'. The timing

diagram in relation to the clock signal will look like this:

0

CLK

1

2

3

4

5

6

7

8

9

10

1

1

7

12

13 14 15

QA

QB

QC

QD

Figure 6-2 Timing diagram of a binary ripple counter

We can see that each time the clock input goes low, the state of QA changes.

Each time QA sinks to '0', QB changes and so on to QD. If we observe the binary notation

of the outputs QA-QD (while QA is the LSB and QD the MSB) we see that the result is

incremental binary counting. We can see the ripple effect of the changes on the output. For

example, on clock pulse no. 15, QD will only change its state after the three preceding FlipFlops have changed their state. Each F-F has its own propagation delay, so that some time

elapses after the clock at the input has sunk to '0', before QD reacts. The delay depends on

the total propagation delay of all the components.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

57

6.2

Count down binary ripple counter

There are two possible ways of materializing this counter. One way is to use

T-Flip-Flops with a non-inverted clock i.e. the state of the F-F changes when

the clock rises from '0' to '1'. The second way is to connect the Q' output of

each T-Flip-Flop to the clock input of the next T-Flip-Flop We will describe

the second option in the next figure:

QA

VCC

VCC

Q

J

CLOCK

QB

Q

J

CLK

K

Q

J

CLK

K

Q

QD

VCC

VCC

J

CLK

QC

K

Q

Q

CLK

K

Q

Q

Figure 6-3 Count down binary ripple counter

The next figure describes the timing diagram of this counter.

0

1

2

3

4

5

6

7

8

9

10 11 12

13 14 15

CLK

QA

QB

QC

QD

Figure 6-4 Timing diagram of a count down binary ripple counter

In the timing diagram, we can see that when the clock goes low, it causes the

output QA to change its state. When QA goes high, QA goes low

consequently causing QB to go high and QB to go low, and similarly through

QC and QD. The ripple effect is clear in this case too.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

58

Here also QA is the LSB (always the F-F closest to the clock pulse input has

the least significance). QD is the MSB.

Once again, QA will change on each clock pulse, QB on every second pulse,

QC on every fourth pulse and QD on every eighth pulse (2n).

6.3

Modulo n and divide by n

This term indicates the number of possible different stable states, which the

counter has. A 4-bit binary counter is a modulo 16 counter. A decimal counter

is a modulo 10 counter.

If two counters are cascaded (connected in series), so that the output of the

first counter is the input of the second counter, the resulting modulo is the

product of the two participating counters.

For example, if two 4-bit binary counters, i.e. modulo 16, are cascaded then a

modulo 256 (16x16) counter is created.

In this way, it is possible to build counters, which count in different ways.

Counters are also called dividers (frequency dividers). If we observe the

output QA we will note that its frequency is half that of the clock input signal.

The frequency of QB is a quarter of the input clock frequency and so on. We

see that a counter can also be used as a frequency divider.

If we treat the counter as a block, which has one output only from its final

stage, then the division factor is its modulo number.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

59

6.4

BCD count up ripple counter

A BCD counter is a 4-bit binary counter with 10 states, from 0 to 9. It is not

designed to enter the realm between 10 and 15.

The following circuit is one way to materialize this counter.

QA

QB

VCC

Q

CLK

K

J

Q

CLK

Q

K

J

Q

CLK

Q

QD

VCC

VCC

J

CLOCK

QC

K

J

Q

CLK

Q

K

Q

Figure 6-5 BCD count up ripple counter

QA changes its state on every clock pulse.

QB changes its state every time QA sinks to '0' if QD=1.

QD changes its state every time QB sinks to '0'.

QD is actually operated from QA, and this too only while QB and QC are both

'1'.

QD has a state when its inputs J-K are '0' instead of '1'. In this case, when the

output combination is the number 9 (1001) the next clock pulse will clear the

entire counter.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

60

Here is the timing diagram for this circuit:

0

1

2

3

4

6

5

7

8

9

10 11

CLK

QA

QB

QC

QD

Figure 6-6 Timing diagram of a BCD count up ripple counter

A further method of materializing modulo n counters with greater ease, is

shown in figure 6-7. The principle behind this method is to incorporate a

decoder, which will identify the first forbidden state of the counter, and create

a pulse to clear all the counter's Flip-Flops.

QA

VCC

VCC

J

CLOCK

QB

Q

QC

VCC

VCC

J

Q

QD

Q

J

CLK

CLK

CLK

K CLR Q

K CLR Q

K

CLR

Q

J

CLK

Q

K

CLR

Q

Figure 6-7 BCD ripple counter with a clear line

When the binary combination 1010 (10) appears on the outputs QA-QD, then

QB and QD are both '1' hereby creating a clear pulse which clears the counter.

This is not a stable state and so is not included in the counter's modulo.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

61

A counter like this can conveniently be materialized for any number of states.

However, you must keep in mind that this structure does have a stable state

with a number, which is out of the required range.

6.5

Integrated ripple counters

A well known series of integrated ripple counters includes the following

devices:

7490 - Decimal counter (divide by 10).

7492 - Divide by 12 counter.

7493 - 4 bit binary counter.

All of these counters are made up of J-K type Flip-Flops, which have their

inputs shorted to VCC (permanently '1'). In other words, these are T-Flip-Flops.

A is an independent F-F. B,C and D are interconnected. The output from A

can be connected to the input to B thereby creating a four F-F counter.

All the Flip-Flops have a common reset (clear) line, which is the result of two

RESET inputs, which are ANDed together. This facilitates easy

materialization of almost any modulo n.

Important Reminder:

These devices have their VCC and GND inputs at extraordinary pin locations.

VCC is at pin 5 and GND is at pin 10. Special care must be taken when

connecting these components.

EB-3153 – Flip-Flops, Registers and Counters Sequential Logic Circuits

62

Preparation questions:

1.

In the following circuit, J and K of each F-F are pulled up to VCC ('1').

The Q outputs' state is 0000.

Q

J

P0

CP

K

Q

J

CP

C

K

Q

Q

J

CP

C

K

Q

Q

J

CP

C

K

Q

C

Q

S7

What will be the Q output state after 4 pulses of P0?

(a)

(b)

(c)

(d)

2.

0000

1100

0100

0010

In the following circuit, J and K of each F-F are pulled up to VCC ('1').

The Q outputs' state is 0000.

J

Clock

Gen.

Q

CP

K

J

Q

CP

Q

K

J

Q

CP

Q