Exam 1 solution

advertisement

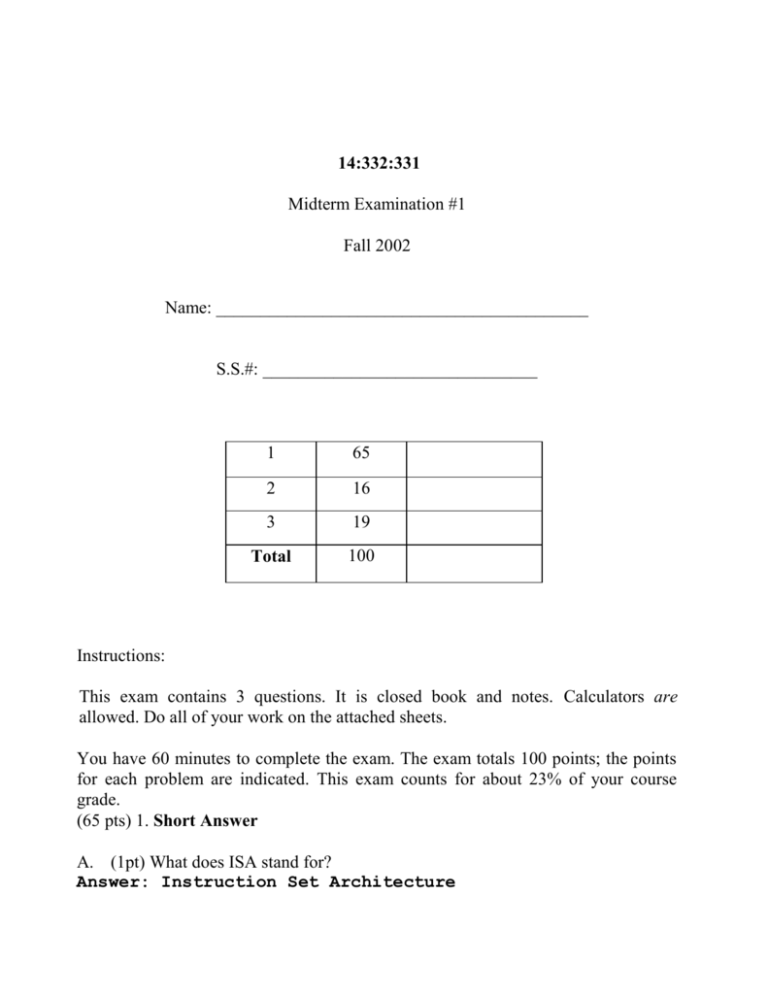

14:332:331 Midterm Examination #1 Fall 2002 Name: __________________________________________ S.S.#: _______________________________ 1 65 2 16 3 19 Total 100 Instructions: This exam contains 3 questions. It is closed book and notes. Calculators are allowed. Do all of your work on the attached sheets. You have 60 minutes to complete the exam. The exam totals 100 points; the points for each problem are indicated. This exam counts for about 23% of your course grade. (65 pts) 1. Short Answer A. (1pt) What does ISA stand for? Answer: Instruction Set Architecture B. (3 pts) What three steps occur to execute MIPS instructions? Answer: 1 - fetch 2 - decode 3 - execute C. (8 pts) MIPS (32-bit architecture) register file contains 32 registers. It has 3 address lines and three data lines. Please specify the width (number of bits) of each line. Register File src1 addr src2 addr dst addr write data 5 32 src1 data 32 src2 data 5 32 32 locations 32 32 bits D. (8pts) Give the minimal sequence of actual MIPS instructions to perform the pseudo instruction ble answer: slt beq $t5, $t3, L $at, $t3, $t5 $at, $zero, L E. (8 pts) Explain why an assembler might have problems directly implementing the branch instruction in the following code sequence. here: . . there: beq $t1, $t2, there add $t1, $t1, $t1 . Answer: the number of instructions between here and there could be more than 216. F. (8 pts) Show how the assembler might rewrite the code sequence in question E. to fix the problem(s). Answer: here: bne j $t1, $t2, close there close: G. (8 pts) Conditional branch destination addresses are determined in the MIPS by adding a 16-bit offset (contained in the lower half of the branch instruction) that has been expanded to a 32-bit value to the updated Program Counter. Complete the diagram shown below to show how this expansion to 32 bits is done. from the low order 16 bits of the instruction 16 offset sign-extended 00 32 Add PC 32 4 Add branch dst address 32 32 32 from the low order 16 bits of the instruction 16 H. (12 pts) The diagram below illustrates base addressing in the MIPS. Base addressing op rs offset rt offset Memory word or byte operand base register The IBM/Motorola PowerPC support two additional types of addressing modes. One mode, called update addressing, is similar to MIPS base branch addressing except the base register value is automatically updated with dst the 32 Add address memory address 32 PC 32 4 32 Add 32 Update addressing op rs rt offset Memory word or byte operand base register How would the MIPS register file have to be altered to accommodate such an addressing mode? Answer: The MIPS register file would have to have two write ports The other mode, called indexed addressing, allows the values stored in two registers whose register file addresses are contained in the instruction to be added together to form the memory address of the operand. If this were an addressing mode supported in the MIPS, what instruction format (R, I, or J) would have to be used? Answer: R format Complete the diagram below to illustrate indexed addressing. Indexed addressing op rs rt Memory rd word or byte operand index register 1 index register 2 I. (4pts) Give an example of a MIPS instruction that contains an absolute address. Any of j jal la 2500 2500 $a0, str J. (5pts) Fill in the blanks in the translation hierarchy diagram shown below. Also indicate, by drawing line(s) from word machine code to the appropriate boxes where the entry is represented in machine code. C program compiler assembly code assembler object code library routines linker machine code executable loader memory (16 pts) 2. Compiling MIPS Code Give the shortest sequence of MIPS assembler instructions to implement the C code for (i=0; i<=10; i=i+1) for (j=0; j<=10; j=j+1) a[i][j] = b[j][i] + c; Assume that a and b are 11 x 11 arrays of word values (integers), and that the base address of a is in $a0 and the base address of b is in $a1. Register $t0 holds the variable i (that has been initialized to zero prior to entering your code). Register $t1 holds the variable j (that has been initialized to zero) and register $s0 holds the byte variable c. The constant 11 has been loaded into register $s1. (The only pseudoinstruction you can use is mul dest src1 src2). Outer: inner: end_inner: slt beq slt beq $t2, $t2, $t2, $t2, $t0, $s1 $zero, exit $t1, $s1 $zero, end_inner add add mul add add add $t2, $t2, $t3, $t3, $t3, $t3, $t0, $t2, $t1, $t3, $t3, $t3, lw add $t4, 0($t3) $t4, $t4, $s0 # load b[j][i] # b[j][i]+c add add mul add add add $t2, $t2, $t3, $t3, $t3, $t3, # # # # # # sw $t4, 0($t3) addi j $t1, $t1, 1 inner # j ++ addi j $t0, $t0, 1 outer # i ++ $t1, $t2, $t0, $t3, $t3, $t3, $t0 $t2 $s1 $t3 $t3 $a1 # 0<=i<=10 # 0 <= j <= 10 # # # # # # $t1 $t2 $s1 $t3 $t3 $a0 2*i 4*i 11*j 22*j 44*j b[j][i] 2*j 4*j 11*i 22*i 44*i a[i][j] # a[i][j] = b[j][i] + c Note: In the solution, I mainly look at three points: the implementation of nested loop how to calculate the offset of a two-dimensional array the matching load/store how to calculate the # of instructions How many instructions are executed during the running of your code? Answer: Suppose n is the # of instructions loop, m is the # of instructions which will in the outer loop, and l is the # of outside of the nested loop. Then the instructions executed during the run is in the inner only execute instructions total # of (m + n * 11) * 11 + l How many memory data references will be made during execution? Answer: 2 * 11 * 11 (19 pts) 3. Assembling MIPS Code Give the machine code for the MIPS assembler code assembled at the starting address 0x0040 0020. (You may use a combination of decimal, hexidecimal and/or binary encodings.) Note that $a0 can be assembled as 4, $a1 as 5, $t0 as 8, $zero as 0. Address 0x0040 0020 MIPS assembler main: exit: slt $t0, $a0, $a1 beq $t0, $zero, exit addi $a1, $a1, 4 j main . . . Machine Code: slt 0 4 5 8 0 beq 4 8 0 2 addi 8 5 5 4 j 2 0000 0100 0000 0000 0000 0010 002 42 Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s1, $s2, $s3 $s1 = $s2 + $s3 (R & I format) subtract 0 and 34 sub $s1, $s2, $s3 $s1 = $s2 - $s3 add immediate 8 addi $s1, $s2, 6 $s1 = $s2 + 6 or immediate 13 ori $s1, $s2, 6 $s1 = $s2 v 6 Data Transfer load word 35 lw $s1, 24($s2) $s1 = Memory($s2+24) store word 43 sw $s1, 24($s2) Memory($s2+24) = $s1 (I format) load byte 32 lb $s1, 25($s2) $s1 = Memory($s2+25) store byte 40 sb $s1, 25($s2) Memory($s2+25) = $s1 load upper imm 15 lui $s1, 6 $s1 = 6 * 216 br on equal 4 beq $s1, $s2, L if ($s1==$s2) go to L br on not equal 5 bne $s1, $s2, L if ($s1 !=$s2) go to L Cond. Branch (I & R format) Uncond. Jump (J & R format) set on less than 0 and 42 slt $s1, $s2, $s3 if ($s2<$s3) $s1=1 else $s1=0 if ($s2<6) $s1=1 else $s1=0 set on less than immediate 10 slti $s1, $s2, 6 jump 2 j 2500 go to 10000 jump register 0 and 8 jr $t1 go to $t1 jump and link 3 jal 2500 go to 10000; $ra=PC+4 0 $zero constant 0 (Hdware) 16 $s0 callee saves 1 $at reserved for assembler ... 2 $v0 expression evaluation & 23 $s7 3 $v1 function results 24 $t8 temporary (cont’d) 4 $a0 arguments 25 $t9 5 $a1 26 $k0 reserved for OS kernel 6 $a2 27 $k1 7 $a3 28 $gp pointer to global area 8 $t0 temporary: caller saves 29 $sp stack pointer (callee can clobber) 30 $fp frame pointer ... 15 $t7 (caller can clobber) 31 $ra return address (Hdware)