MDonadio-LNA

advertisement

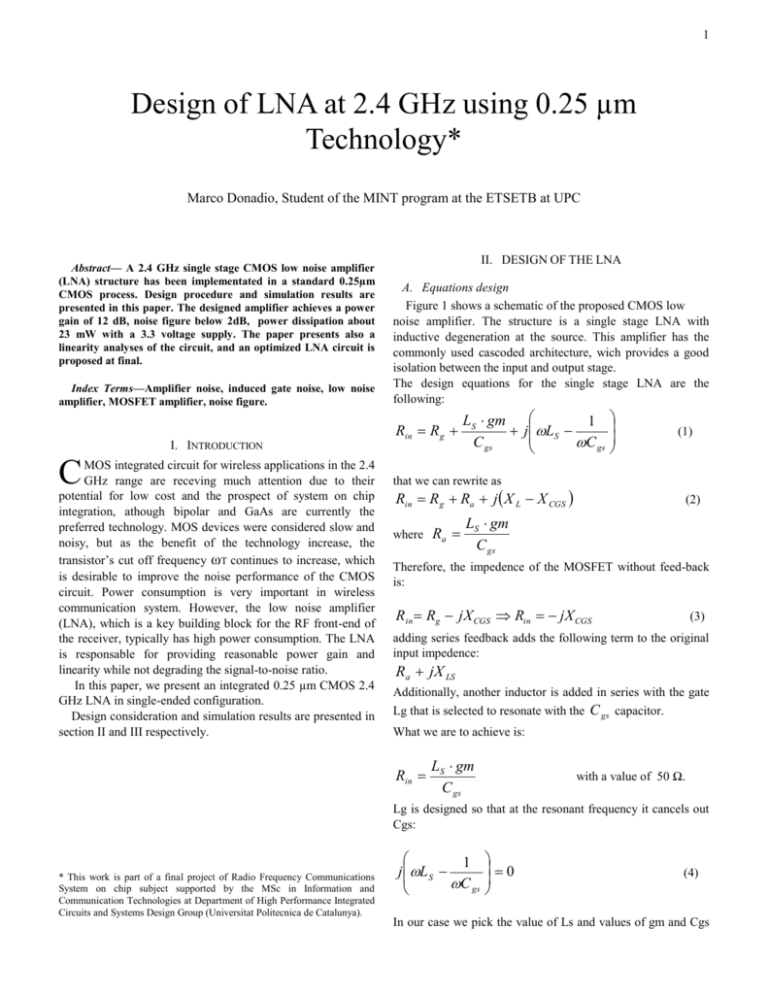

1 Design of LNA at 2.4 GHz using 0.25 µm Technology* Marco Donadio, Student of the MINT program at the ETSETB at UPC Abstract— A 2.4 GHz single stage CMOS low noise amplifier (LNA) structure has been implementated in a standard 0.25µm CMOS process. Design procedure and simulation results are presented in this paper. The designed amplifier achieves a power gain of 12 dB, noise figure below 2dB, power dissipation about 23 mW with a 3.3 voltage supply. The paper presents also a linearity analyses of the circuit, and an optimized LNA circuit is proposed at final. Index Terms—Amplifier noise, induced gate noise, low noise amplifier, MOSFET amplifier, noise figure. I. INTRODUCTION C MOS integrated circuit for wireless applications in the 2.4 GHz range are receving much attention due to their potential for low cost and the prospect of system on chip integration, athough bipolar and GaAs are currently the preferred technology. MOS devices were considered slow and noisy, but as the benefit of the technology increase, the transistor’s cut off frequency ωT continues to increase, which is desirable to improve the noise performance of the CMOS circuit. Power consumption is very important in wireless communication system. However, the low noise amplifier (LNA), which is a key building block for the RF front-end of the receiver, typically has high power consumption. The LNA is responsable for providing reasonable power gain and linearity while not degrading the signal-to-noise ratio. In this paper, we present an integrated 0.25 µm CMOS 2.4 GHz LNA in single-ended configuration. Design consideration and simulation results are presented in section II and III respectively. II. DESIGN OF THE LNA A. Equations design Figure 1 shows a schematic of the proposed CMOS low noise amplifier. The structure is a single stage LNA with inductive degeneration at the source. This amplifier has the commonly used cascoded architecture, wich provides a good isolation between the input and output stage. The design equations for the single stage LNA are the following: Rin R g LS gm C gs 1 j LS C gs (1) that we can rewrite as Rin Rg Ra j X L X CGS where Ra (2) LS gm C gs Therefore, the impedence of the MOSFET without feed-back is: R in Rg jX CGS Rin jX CGS (3) adding series feedback adds the following term to the original input impedence: Ra jX LS Additionally, another inductor is added in series with the gate Lg that is selected to resonate with the C gs capacitor. What we are to achieve is: Rin LS gm C gs with a value of 50 Ω. Lg is designed so that at the resonant frequency it cancels out Cgs: * This work is part of a final project of Radio Frequency Communications System on chip subject supported by the MSc in Information and Communication Technologies at Department of High Performance Integrated Circuits and Systems Design Group (Universitat Politecnica de Catalunya). 1 j L S C gs 0 (4) In our case we pick the value of Ls and values of gm and Cgs 2 are calculated to give the required Rin. but we use it because we will have a good noise figure. Once we have all the value for inductors the bias voltage Vg is set to enable the operation point of the amplifier. The use of inductive degeneration topology has the benefit of simultaneously achieving both input and noise matching. To achieve a good output matching an additional buffer stage is design at the output (figure 2). Fig.2 LNA with output buffer stage Fig.1 A single ended 2.4 GHZ LNA B. LNA single stage Design The first step in the design procedure is to determine MOS transistor size in the input stage. I used values from CTH technology (see Table 1) and I obtained an optimal value of 840µm to minimize the noise figure. TABLE I PROCESS PARAMETERS Wopt Cox 8.4 fF/um^2 L 0.25 Kn’ 3.75e-04 A/V^2 Vth 0.45 LD 1e-02 um Cgdo 2.4e-16F/um Gamma 0.9 Delta 6 C 0.395 Alpha 1.3 3 1 840m 2 0 LCOX RS QSP III. SIMULATIONS AND RESULT To test the LNA I used a testbench to probe functionality and the properties of the LNA with the values calculated. The simulation of gain (S21) and reverse gain (S12) appears in Fig 3. The gain has a peak value of 21.5 dB at 2.46 GHz and reverse gain about -42.5 dB at the same frequency. The input reflection coefficient (S11) and output matching coefficient (S22) are plotted in Fig.4. The value of S22 without output buffer stage was about -3 dB; in the new configuration now is almost -14 dB at 2.4 GHz. Figure 5 shows the noise figure (NF) versus frequency for the LNA. Fmin 1 2.4 (5) The value of W appear too big for low power application, 0 T (6) At 3.3 V supply, the LNA achieves a NF of 1 dB at 2.4 GHz; this value is very good but influences the power consumption feature. The power consumption is about 23 mW (Fig. 6). The high power consumption is due because we have a large width of transistor (840 µm). In a future work it’s possible to improve the value of power consumption using capacitors element in parallel to single transistor instead a chain of transistor for cascade stage. This technique should be improve a lot the consumption of the circuit but it’s more complex to implement in a system on chip because high area is required. 3 The 1 dB compression point is the point where the gain of the circuit has dropped 1 dB from it small-signal asymptotic value. In my case I have a value about -24 dBm. Fig. 3 S21, S12 parameters Fig.6 Power consumption Vs bias voltage Fig.4 S11, S22 parameters A two-tone IP3 simulations was performed on the LNA, and result are shown in Fig.7. The two tones were applied with equal power at 2.4 GHz and 2.9 GHz. The magnitude of the fundamentals and the third-order intermodulation products at the output are shown. The linearity is primarily limited by the output-stage transistor. An other measure of linearity is made plotting the 1dB compression point line (Fig. 8). To measure the compression point of the circuit, I applied a sinusoid to its input and I plotted the output power of the fundamental as a function of the power of the input. Fig.5 Noise Figure Vs frequency Fig7 Result of two-tone IP3 simulation Fig.8 1dB compression Point simulation IV. CONCLUSION In this paper, we have proposed a 2.4 GHz single-stage 4 LNA in a standard 0.25 µm CMOS technology. Good noise and gain performance were obtained but with bad power consumption. A noise figure of 1 dB and a power gain of 21.5 dB. All the parameters for LNA such as Voltage Gain, S11, Power consumption and Noise Figure, Input- referred IP3 are simulated in cadence on the schematic design. REFERENCES X. Yang, T. Wu and J. McMacken, “Design of LNA at 2.4 GHz Using 0.25 µm Technology”, School of Electrical Engeneering and Computer Science, Orlando 2001. [2] Wen-Shen Wuen and Kuei-Ann Wen, Dual-Band switchable Low Noise Amplifier for 5-GHz Wireless LAN Radio Receivers. 2002 IEEE. [3] José Luis González Jiménez, Design Example of a Low Noise Amplifier. RFCS, MINT course at the ETSETB-UPC 2007 [4] Behzad Razavi, RF Microelectronics. [5] Derek K. Shaeffer, and Thomas H. Lee, “A 1.5 V, 1.5 GHz CMOS low loise amplifier”, IEEE Journal of Solid-State Circuits, Vol. 32, No. 5, May 1997. [1]