Lab 3: 8-Bit Look-Ahead Carry Adder

advertisement

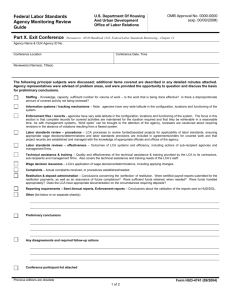

University of Florida Electrical & Computer Engineering Page 1/4 EEL 4712 - Fall 2007 Dr. Eric. M. Schwartz 7-Mar-16 Revision 0 Lab 3: 8-Bit Look-Ahead Carry Adder PURPOSE This lab introduces the VHDL structural description and hierarchical design using Quartus. You will prepare an 8-bit adder for use in later assignments. MATERIALS UF-4712 Board, Power supply, ByteBlaster Cable Printout of the Lab 3 Addendum file (on website) Oscilloscope (in lab), Logic Analyzer (in chip or lab) PRE-LAB REQUIREMENTS 1. Review the Look-Ahead Carry Adder (LCA) information in section 5.4 in the Brown textbook and in section 6.3 in the Lam textbook. 2. In this lab you will ultimately design an 8-bit LCA after first designing primary components, then building the design up through a 2-bit LCA and then a 4-bit LCA. This 8-bit LCA will be based on a 2-bit block size. The two components of our adders is a 1-bit adder and a Look-Ahead Carry Generator (as shown in Figure 1). The first component that I would like you to design is the 1-bit adder block of a 1-bit full adder (FA) that generates the 1-bit G and P outputs as well as the sum output (but no carry output) using the two single-bit data inputs and a carry input. (See Figure 1.) The second component is a Look-Ahead Carry Generator (LCG) for a 2-bit block size. The Look-Ahead Carry Generator has two G inputs and two P inputs (one set from each of two adder blocks), and a carry input. The LCG has the following outputs: two carry outs, Cx+1 and Cx+2, one from each set of G and P inputs, a Block P and a Block G. When designing larger adders with the Add_1 and LCG_2 components, be sure to label each of the signals in your block diagrams. The Cx+2 outputs will not be used except for the last carry, e.g., C8 in the 8-bit LCA. All carries are generated as functions of G’s, P’s and Cx’s. The Cx inputs come from C0 or Cx+1 outputs only. No other carry signals should be used in generating new carries. 3. When drawing your block diagrams, take advantage of the “copy and paste” capability. Prepare a small text box with the appropriate font and type in the text. From that point on, the box can be copied and edited to contain new text as needed. Drawing elements (boxes with labels) may also be grouped, copied and pasted to rapidly create a drawing. The 1-bit adder drawing symbol can be copied seven more times to build the remaining bits of an 8-bit LCA. I suggest that on your way to designing an 8-bit LCA, after you’ve designed your 2-bit LCA, design a 4-bit LCA and only then design the 8-bit LCA. 4. Each box should support single-bit signals. Do not bus the Carry Outputs of the Look-Ahead Carry generators. Buses may be used to bring data into and out of the drawing. Place the most significant bit of the adder on the left in your diagram and the least significant bit on the right. Place the look-ahead carry generators in rows below the 1-bit adders. I am trying to get you to create a hierarchical design similar to Figure 6.7 in the Lam textbook (as shown in our Lecture 7: Adders). 5. Prepare a behavioral VHDL design file that describes the 1-bit adder block. The inputs are cin, a, and b. The outputs are s, g, and p. Notice that this adder component is not responsible for generating the carry outputs. Create the entity statement for a component called “add1.” Place a complete canonical truth table for all of the outputs as a comment in the VHDL file. Place your name, date and section number as a comment in the VHDL file. It would also be helpful to include the “component” and “port map” statements as comments so that they can be copied into later VHDL structural files. Write the standard sum-of-products output equations as VHDL assignment statements in the architecture. 6. Name the project, and assign the device as the Cyclone EP1C3T144C8. Compile and remove any errors. Since there are no internal signals, the results should be the same for any synthesis option. Prepare suitable test vectors and use the simulator to verify the design. Capture the test vectors in a “.tbl” file for use in the report. a) If you would like the simulation results to appear in the same window as the vector waveform file, go to “Assignment | Settings | University of Florida Electrical & Computer Engineering Page 2/4 EEL 4712 - Fall 2007 Dr. Eric. M. Schwartz 7-Mar-16 Revision 0 Lab 3: 8-Bit Look-Ahead Carry Adder Simulator Settings” (or “Processing | Simulator Tool”) and select “Overwrite simulation input file with simulation results.” The simulation will appear in both the vector waveform file (.vwf) and in the “Simulation Results” windows. b) To make a .tbl file, just save the simulation output (either in the Simulation Results” window or in the .vwf file, if you did part a above) by selecting “File | Save As”, then selecting “Vector Table Output File (*.tbl)”. c) To view what is really in this file, open it in Quartus by selecting “File | Open...”, then select the file name, the option “Text” under “Open as”. You can also open this file with notepad or another text editor program. This file should contain a table of data. If you open it in Quartus with “Open as” set to “Auto”, the results will appear graphically, like a .vwf file. 7. Prepare a behavioral VHDL design file that describes a 2-bit look-ahead carry generator called “lca_gen.” Place the truth table for lca_gen as a comment in its VHDL file. The inputs to lca_gen are cin, g0, g1, p0, and p1. The outputs are blk_g, blk_p, cout0, and cout1. Declare internal signals that are of type std_logic_vector that allow vector assignment statements to be used for the g and p signals. Write the architecture body of the lca_gen using only assignment statements. Prepare test vectors and use the simulator to verify the design. It would also be helpful to include the “component” and “port map” statements as comments. 8. Prepare a VHDL structural description of the 8bit Look-Ahead Carry Adder based on the two components described above. (You might want to first creat a 4-bit LCA.) The drawing produced previously will be useful in preparing the structural VHDL description. The inputs to the adder are cin, and 8-bit signals a and b. The outputs are cout, blk_g, blk_p, and the 8-bit sum s. We need to prevent the synthesizer from removing the internal signals, shown in your diagram, from the solution. One way to accomplish this is to use structural VHDL to place an LCELL in series with each of the internal signals we wish to preserve. Refer to the Lab 3 Addendum file by and the Quartus documentation for more information on the use of LCELLs. a) Try to exploit the hierarchical structure of the LCA by first building a 2-bit LCA, composed of two FA’s and one LCG. Thoroughly test this adder via simulation. b) Use two 2-bit LCA’s and another LCG to create a 4-bit LCA. Thoroughly test this adder via simulation. c) Use two 4-bit LCA’s and another LCG to create an 8-bit LCA. Thoroughly test this adder via simulation. 9. Place the component statements for the two components in the design file. Name the new project, compile the project, eliminate errors and simulate the design. Look in the equations in the report to verify that an 8-bit look-ahead carry adder was actually produced. It should be noted that if the internal signals in the design had been removed from the port statement, they would have been minimized out of the design and the adder would look significantly different. 10. Write a set of test vectors that will verify that each of the internal signals changes when expected. A complete set of test vectors will not be used in this assignment. Short simulations over a region of interest would be most effective. Be sure to compare the results with the expected lines in the truth table for the adder. Some suggested points to test would include (cin + b + a): 0+0+0, 1+0+0, 0+0xFF+0xFF, 1+0xFF+0xFF. There are internal carries that are generated in several of the lca_gen components. Develop test vectors that set each of these carries to a 1. 11. Use the Timing Analyzer to get estimates of the propagation times for the following paths: cincout, cins7, a0cout, and a0s7. Use the Waveform Editor to verify that the timings are consistent with the intended design. IN-LAB PROCERDURE 1. Synthesize the 8-bit LCA for the Cyclone EP1C3T144C8 on the BT-U board. Use the Floorplan Editor to create pin assignments. Select the pins so that you can use the switches for inputs and 7-segment display(s) as outputs by University of Florida Electrical & Computer Engineering Page 3/4 EEL 4712 - Fall 2007 Dr. Eric. M. Schwartz 7-Mar-16 Revision 0 Lab 3: 8-Bit Look-Ahead Carry Adder using jumpers on the appropriate pins. This will require that you use your 7-segment display decoders from lab 2. You may use the Graphic Editor (a .bdf file) to connect two 7-segment decoders from Lab 2 and visually display the sum. Develop a demonstration to convince your TA that the adder is working properly. 2. For your lab report, use the LSA to gather data to prove that the hardware works. 3. Design and sketch a test fixture that will allow you to measure the propagation time across the signal path from the Carry-In to the Carry-Out of the 8-bit LCA. Hint: The best tests are usually created by finding a way to change a single input to cause a change in a single output. For example, if two fixed numbers are used to drive the a and b inputs of the adder, a change on Carry-In will be seen as a change on the CarryOut pin. Choose the values driving a and b such that a ‘0’ on Carry-In produces a ‘0’ on CarryOut and a ‘1’ on Carry-In produces a ‘1’ on Carry-Out. Drive the Carry-In using the Clock. Connect the two channels of the oscilloscope, set the timebase for an appropriate value, trigger the trace from an appropriate transition on Carry-In, and make the measurement of the propagation time. Make a drawing of the signals seen on the oscilloscope. 4. Using same test fixture, measure the propagation time from the Carry-In to the sum bit s7. Determine the values when s7 changes from 01 (tPLH) and from 10 (tPHL). Make drawings for each measurement. QUESTIONS 1. Modify the two 4-bit adders from Lab #2 (IEEE Addition & Ripple-Carry) to produce 8-bit versions. Compile the two adders with the appropriate synthesis options that preserve their structure). Use the Timing Analyzer to prepare a table to compare the three 8-bit adders for their speed (worst-case propagation delay), as synthesized for the Cyclone EP1C3T144C8 on the BT-U board. 2. Verify, for the above 3designs, that the three different adder structures were preserved in synthesis. You can do this by examining the equations produced by the synthesizer as presented in the “.fit.eqn.” report files. This means that the LCA structure can be seen as a structure in which macrocells contain the equations produced in each component of the LCA Adder structure. Similarly, for the RippleCarry Adder, each sum or carry bit is implemented as a single macrocell containing an equation for the appropriate term of a 1-bit adder. a. To create an equation file for the design without regard to the chosen chip, i.e., prefitting), do the following. After compiling the design (either with a full compilation or a functional compilation) select “Processing | Start | Start Equation Writer (PostSynthesis).” A file ending in “.map.eqn” is created. b. To create an equation file for the design after fitting it the chosen chip (i.e., post-fitting), do the following. After a full compilation (not a functional compilation) select “Processing | Start | Start Equation Writer (Post-Fitting).” A file ending in “.fit.eqn” is created. 3. Based on the Timing Analyzer data, identify the worst-case signal path in each adder. Hint: A signal path is the path that a signal travels from a given input to a given output. 4. Consider the Carry-In to s7 delay measurements made in the lab. Was there any difference between tPLH and tPHL? How do the limits of the test equipment affect the measurements of propagation times? EEL 4712 - Fall 2007 University of Florida Electrical & Computer Engineering Page 4/4 Dr. Eric. M. Schwartz 7-Mar-16 Revision 0 Lab 3: 8-Bit Look-Ahead Carry Adder Ci+2 Bi B Ai Adder (Add_1) G P Gi Pi Gi+1 Pi+1 G1 Cx+2 A Cin Ci Ci Ci+1 Gi P1 Cx+1 G0 Pi P0 Cx Look-Ahead Carry Generator (LCG_2) Block G S Si Blk_Gy Block P Blk_Py Figure 1: Adder and Look-Ahead Carry Generator components.