KAILASH KUMAR AGRAWAL

advertisement

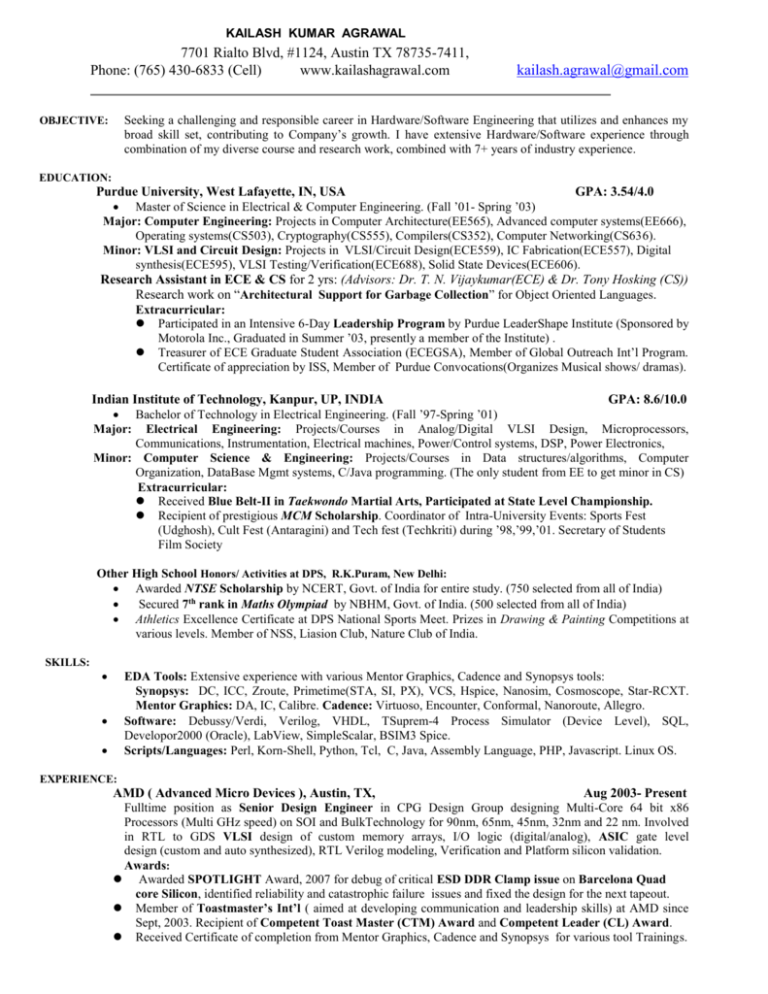

KAILASH KUMAR AGRAWAL 7701 Rialto Blvd, #1124, Austin TX 78735-7411, Phone: (765) 430-6833 (Cell) www.kailashagrawal.com kailash.agrawal@gmail.com Seeking a challenging and responsible career in Hardware/Software Engineering that utilizes and enhances my broad skill set, contributing to Company’s growth. I have extensive Hardware/Software experience through combination of my diverse course and research work, combined with 7+ years of industry experience. OBJECTIVE: EDUCATION: Purdue University, West Lafayette, IN, USA GPA: 3.54/4.0 Master of Science in Electrical & Computer Engineering. (Fall ’01- Spring ’03) Major: Computer Engineering: Projects in Computer Architecture(EE565), Advanced computer systems(EE666), Operating systems(CS503), Cryptography(CS555), Compilers(CS352), Computer Networking(CS636). Minor: VLSI and Circuit Design: Projects in VLSI/Circuit Design(ECE559), IC Fabrication(ECE557), Digital synthesis(ECE595), VLSI Testing/Verification(ECE688), Solid State Devices(ECE606). Research Assistant in ECE & CS for 2 yrs: (Advisors: Dr. T. N. Vijaykumar(ECE) & Dr. Tony Hosking (CS)) Research work on “Architectural Support for Garbage Collection” for Object Oriented Languages. Extracurricular: Participated in an Intensive 6-Day Leadership Program by Purdue LeaderShape Institute (Sponsored by Motorola Inc., Graduated in Summer ’03, presently a member of the Institute) . Treasurer of ECE Graduate Student Association (ECEGSA), Member of Global Outreach Int’l Program. Certificate of appreciation by ISS, Member of Purdue Convocations(Organizes Musical shows/ dramas). Indian Institute of Technology, Kanpur, UP, INDIA GPA: 8.6/10.0 Bachelor of Technology in Electrical Engineering. (Fall ’97-Spring ’01) Major: Electrical Engineering: Projects/Courses in Analog/Digital VLSI Design, Microprocessors, Communications, Instrumentation, Electrical machines, Power/Control systems, DSP, Power Electronics, Minor: Computer Science & Engineering: Projects/Courses in Data structures/algorithms, Computer Organization, DataBase Mgmt systems, C/Java programming. (The only student from EE to get minor in CS) Extracurricular: Received Blue Belt-II in Taekwondo Martial Arts, Participated at State Level Championship. Recipient of prestigious MCM Scholarship. Coordinator of Intra-University Events: Sports Fest (Udghosh), Cult Fest (Antaragini) and Tech fest (Techkriti) during ’98,’99,’01. Secretary of Students Film Society Other High School Honors/ Activities at DPS, R.K.Puram, New Delhi: Awarded NTSE Scholarship by NCERT, Govt. of India for entire study. (750 selected from all of India) Secured 7th rank in Maths Olympiad by NBHM, Govt. of India. (500 selected from all of India) Athletics Excellence Certificate at DPS National Sports Meet. Prizes in Drawing & Painting Competitions at various levels. Member of NSS, Liasion Club, Nature Club of India. SKILLS: EDA Tools: Extensive experience with various Mentor Graphics, Cadence and Synopsys tools: Synopsys: DC, ICC, Zroute, Primetime(STA, SI, PX), VCS, Hspice, Nanosim, Cosmoscope, Star-RCXT. Mentor Graphics: DA, IC, Calibre. Cadence: Virtuoso, Encounter, Conformal, Nanoroute, Allegro. Software: Debussy/Verdi, Verilog, VHDL, TSuprem-4 Process Simulator (Device Level), SQL, Developor2000 (Oracle), LabView, SimpleScalar, BSIM3 Spice. Scripts/Languages: Perl, Korn-Shell, Python, Tcl, C, Java, Assembly Language, PHP, Javascript. Linux OS. EXPERIENCE: AMD ( Advanced Micro Devices ), Austin, TX, Aug 2003- Present Fulltime position as Senior Design Engineer in CPG Design Group designing Multi-Core 64 bit x86 Processors (Multi GHz speed) on SOI and BulkTechnology for 90nm, 65nm, 45nm, 32nm and 22 nm. Involved in RTL to GDS VLSI design of custom memory arrays, I/O logic (digital/analog), ASIC gate level design (custom and auto synthesized), RTL Verilog modeling, Verification and Platform silicon validation. Awards: Awarded SPOTLIGHT Award, 2007 for debug of critical ESD DDR Clamp issue on Barcelona Quad core Silicon, identified reliability and catastrophic failure issues and fixed the design for the next tapeout. Member of Toastmaster’s Int’l ( aimed at developing communication and leadership skills) at AMD since Sept, 2003. Recipient of Competent Toast Master (CTM) Award and Competent Leader (CL) Award. Received Certificate of completion from Mentor Graphics, Cadence and Synopsys for various tool Trainings. PROJECTS AT AMD: Responsible for designing and developing various custom & manual/auto synthesized circuits with speeds over 3 Ghz. Involved working closely with Macro, Implementation, DFT, Modeling, RTL, Verification, PDE & Layout teams. Entailed running static/dynamic circuit checks using various design guidelines, noise analysis, power analysis, EMIR analysis, writability, DFT support (Logic/Memory BIST, Scan), leakage analysis and hspice based timing simulations (including internal timing, races and setup/hold time analysis using STA tools as well as writing macrocell char arcs), RTL/verilog modeling and formal/functional verification (LEC). Most of these designs achieved more than 30% power and speed improvements within the given area budget. Custom designed Transistor level Circuits (No synthesis, Full custom): 6T and 8T SRAM cells for L1/L2/L3 caches, Multi Read and Write port Register files, ROM cells for floating point and microcode, Various domino logic as dynamic mux, dynamic comparator and dynamic array structures. Innovative Ring Oscillators mimicking critical paths on chip as well as other performance/technology ring oscillators. Custom designed ASIC circuits working at gate level using the standard library cells: included circuits on the Instruction/Data Cache, Floating point, Execution, Scan/Decode, Clock/Power unit, Memory controllor, DRAM controller, APIC, North Bridge, HyperTransport Logic, Misc IO Unit, FuseBox. Involved logic design from RTL, and manual placement. Standard routing tools (nanoroute) used for final routing. Involved working at architectural and RTL level. Gate Simulations performed to ensure correctness with RTL. Full/Partial Synthesized ASIC circuits: Worked with design synthesis, auto placement and routing tools (synopsys DC, ICC) to design 100% synthesized blocks, as well as hybrid blocks consisting of mixture of custom designed logic and synthesized logic portions for different blocks in core and NB. Electrical cleanup as well as ECO edits done manually. Verilog Simulator (Verdi, VCS) used for debugging. Analog Circuits and IO interface. This involved working on the DDR, HT, PCI circuits, PLL, ESD Clamps, Thermal Sensors and Misc IO interface involving various analog/digital pins for JTAG Ports. Also worked on clock architecture designing clock trees and gaters. Library cells (flops, latches, various logic gates) design for use in auto-synthesized and custom built circuits. Wrote scripts to verify writability, alpha particle hit, low voltage, glitch analysis tests and fixing them. Product Development Team and DFT team on SCAN/BIST to resolve issues on Silicon. This involved debugging Timing Critical paths and Functional issues on Silicon using internal AMD tools and working on the Test Floor with ATE and HST. Worked with Device Analysis Team on yield issues and on Focused Ion Beam Technology to facilitate debugging of critical faulty logic on the chip. Worked with Dresden Fab Team on device issues. Platform silicon validation: Worked at platform level (system motherboard) to validate silicon. Used Tektronix Oscilloscope to probe signals, Motherboard Layout tool (Allegro) to view design and occasional soldering to debug. Worked on Power/Thermal functionality of Processor at BIOS/OS level, various Misc IO pins, signal buses (I2C, SMBus, DDR, HT, PCI, AMDSI), signal integrity for various pad pins and motherboard routing. Involved interaction with all motherboard components, Power delivery, clock distribution, LPC BIOS, SB, DDR and other peripherals connected. Required extensive x86 system level understanding. PROJECTS AT UNIVERSITY: Research Assistant Projects: Architectural Support for Garbage Collection for Object Oriented Languages on Uniprocessor , SMT (Simultaneous MultiThreading) and Parallel Systems. Added support for Garbage Collection on the Uniprocessor out-of-order Superscalar Simulator (in C) and Multiprocessor Wisconsin Wind Tunnel Simulator (in C), involved assembly level debugging/coding ( added 5000+ lines), new instruction set support for Alpha binaries,. Involved intricate hardware/software integration of hardware simulator, compiler and OS. GCC compiler, Simplescalar simulator suitably hacked to generate and run binaries on alpha machine. Benchmarks evaluated. Course Projects: . Internetworking: Designed and implemented an Internet router along with various applications using Xinu OS on a Pentium computer ensuring interoperability with commercial products. Provided support for TCP/IP, UDP, ICMP, ARP, IGMP, RIP, BOOTP, DHCP, CIDR, NAT, DNS, SNMP, HTTP, etc. along with applications as Chat, Ping, Finger, Firewall. Operating System : Implemented support for Virtual Memory ( Page fault handler ), File systems, Read/Write Lock, Process Scheduler for Xinu OS on a Pentium III computer. Involved modification of kernel, drivers, libraries and shell commands on Xinu OS. Cryptography & Data Security: Designed a dynamic Password scheme for a Client/Server Model to enhance network security against replay attacks. Wrote CGI scripts in C for web based interface and ran it on client/server. Compilers: Designing various Compilation Phases ( both Front end and Back end ) for MiniJava ( a subset of Java ) using JavaCC. Database: Developed a hotel Database application using SQL and Developer2000 involving various automated Bookkeeping features. IC Fabrication : Fabricated 3-mask Diode Chip, 4-mask MOSFET Transistor Chip, Solar cell and different Resistors. Detailed experiments using Keithley 4200 Test Equipment involved extraction of various parameters (R, C, Vt, tox, s) and generating final I-V, C-V plots. Detailed 2D simulations performed using TSuprem-4 Process Simulator for Diode and Transistor to study the varying effects of Temp, Implant dose/energy, time, etc. on the doping profile. Digital Logic Synthesis: Theoretical concepts in Two level / Multilevel Logic synthesis, FSM Synthesis, State encoding, Retiming, Binary Decision diagrams, Technology Mapping, I/O Experiments. VLSI Testing and Verification: Theoretical concepts in BIST, DFT, Scan circuits, Fault models ( stuck at faults ), Critical path tracing, Fault simulation, PODEM, Decision Tree, LFSR, Test generation & compaction. STATUS: VLSI / Circuit Design: Designed Optimized Adder, Multiplier and ring oscillators with completed layout in 0.25 m Technology using Cadence Virtuoso. PCB Design: Fabricated a tunable frequency, Square wave Generator on a PCB ( MicroSim Pspice Simulator ) Microprocessor Project: Developed an elementary 4 bit Microprocessor (using Xilinx) starting from coding at RTL level using VHDL, to the final physical layout using Magic software. Instrumentation Project: Simulated Function Generator, Temperature Sensor. Interfaced these with a hardware circuit with a PC control/display panel employing GPIB driver, RS 232 interfaces, using Labview Software. Permanent Resident (Green Card holder). Authorized to work for any employer in USA.