Paper Title (use style: paper title)

advertisement

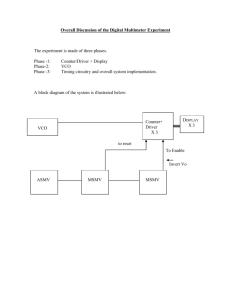

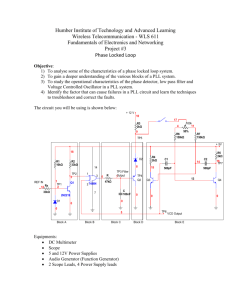

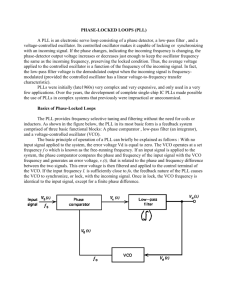

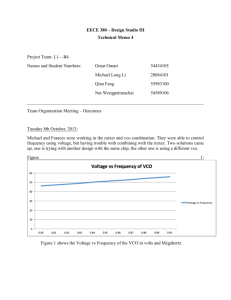

JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION ENGINEERING DESIGN AND IMPLEMENTATION OF 200MHZ CURRENT STARVED VOLTAGE CONTROLLED OSCILLATOR (VCO) FOR DPLL USING 45NM DEEP SUBMICRON CMOS TECHNOLOGY 1 HARIKRUSHNA I. DELVADIYA, 2 PROF. JAI KARAN SINGH 1 Dept. 2 of Electronics & Communication Engineering, Sri Satya Sai Institute of Science and Technology, Sehore, Bhopal, Madya pradesh, India. Head, Dept. of Electronics & Communication Engineering , Sri Satya Sai Institute of Science and Technology ,Sehore, Bhopal Madyapradesh, India hkpatel13@gmail.com ,ec.sssist@gmail.com ABSTRACT: In wireless communication system the digital phase locked loop plays important role specially Voltage controlled oscillator. An oscillator is an electronic device used for the purpose of generating a signal. Applications range from clock generation in microprocessors to carrier synthesis in cellular telephones, requiring vastly different oscillators’ topologies and performance parameters. VCO can be built using many circuit techniques. This paper deals with the design and implementation of CMOS voltage controlled oscillators (VCO). A VCO is an oscillator, where the control voltage controls the oscillator output frequency. Key words: CMOS VCO, Current-Starved VCO. 1. INTRODUCTION: In a wireless system the quality of the communication link is determined in large part by the characteristics of the VCO and in today’s wireless communication systems greater frequency range is required by the VCOs. Traditionally, VCOs using CMOS technology have been used for low frequency applications, but submicron processes have allowed CMOS oscillators to achieve frequencies in the gigahertz range [2]. This range is made possible with the use of automatic swing control. VCO can be built using many circuit techniques [5]. In this paper designing of CMOS VCO using LT spice here current starved VCO is design. Though there are so many design requirements of a VCO, which are phase stability, large electrical tuning range, linearity of frequency verses control voltage, large gain factor, capability of accepting wideband modulation and low cost but the most important factor in designing the VCO is the linearity, on the basis of which the comparison between CMOS VCOs is described [6]. With respect to digital phones that use these circuits, low power consumption, small size and low fabrication costs are important design factors. In order to achieve a higher quality factor, CMOS oscillators have been designed in the form of ring oscillators [3, 7]. 2. CURRENT STARVED VCO This current starved VCO is designed using ring oscillator and its operation is also similar to that. From the schematic circuit shown in the Figure 1, it is observed that MOSFETs M2 and M3 operate as an inverter, while MOSFETs M1 and M4 operate as current sources. The current sources, M1 and M4, limit the current available to the inverter, M2 and M3; in other words, the inverter is starved for the current. The MOSFETs M5 and M6 drain currents are the same and are set by input control voltage. The currents in M5 and M6 are mirrored in each inverter/current source stage. The upper PMOS transistors are connected to the gate of M6 and source voltage is applied to the gates of all lower NMOS transistors [4]. Figure 1 Current-Starved VCO 3. DESIGN OF VCO To determine the design equations for use with the current-starved VCO, the total capacitance on the drains of M2 and M3 is given by ISSN: 0975 – 6779| NOV 10 TO OCT 11 | VOLUME – 01, ISSUE - 02 Page 143 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION ENGINEERING Ctot Cout Cin 3 Ctot C 'ox (W p Lp Wn Ln ) C 'ox (W p L p Wn Ln ) 2 … (1) This is simply the output and input capacitances of the inverter. The equation can be written in more useful form as 5 C 'ox (W p L p Wn Ln ) 2 ……….……(2) Ctot VSP Ctot The time it takes to charge the constant current t1 Ctot from zero to with I D 4 is given by VSP I D 4 ………………………… (3) Ctot While the time it takes to discharge t2 VinVCO from VDD = VDD/2), then the sum of The average current drawn by the VCO is I avg N VDD Ctot N VDD Ctot f osc T …. (7) Or I avg I D ……………………………………….. (8) The average power dissipated by the VCO is Pavg I avg VDD VDD I D ………………(9) If the power dissipated by the mirror MOSFETs, M5 and M6, is also included then the power is doubled from that given by the equation (9), assuming V to SP is given by VDD VSP t2 Ctot I D1 ……………………… (4) I I I I If D 4 = D1 = D (which is labelled as Dcenter when frequency or lower the gain of the oscillator enough to kill oscillations altogether. t1 and I I I I D5 D 6 . For low power dissipation D that D should be kept low, or in other words oscillation frequency should be low [4]. C We begin by calculating the total capacitance tot . Using equation (2) and assuming the inverters, M2 and M3, are sized for equal drive, that is, Ln Lp 1 , Wn = 10 and Wp =20, the capacitance is is simply t1 t2 Ctot VDD I D …………………………(5) Let’s use a centre drain current of I D VGS The oscillation frequency of the current starved VCO for N (an odd number >= 5) of stages is f osc 1 1 N (t1 t2 ) N Ctot VDD ……….. (6) 10 A based on characteristics of the MOSFETs. The selection of the current is important because when VinVCO is VDD/2, the oscillation frequency to be 200MHz. The number of stages, using equation (6), is given by Equation 3.6 gives the centre frequency (f centre) of I I Dcenter VTHN . Therefore, the VCO when D = oscillating, neglecting when f min VinVCO < . The VCO stops sub-threshold currents, Vmin = VTHN and Total 17 stages are required to generate 200MHz oscillating frequency at the control voltage of approximately VDD/2 [4]. , is 4. SIMULATION RESULT OF CURRENT STARVED VCO The actual clock generated by a PLL comes from the voltage-controlled oscillator (VCO), which generates a periodic oscillation. The frequency of this oscillation can be controlled by modulating some control voltage. In a PLL, the control voltage corresponds to some filtered form of the phase error. In response to this, the VCO adjusts its frequency. As the VCO frequency is slewed by the control voltage, the phase error is driven towards zero. = 0. The maximum VCO oscillation frequency, f max V I determined by finding D when inVCO = VDD. At V the maximum frequency, max = VDD. The output of the current starved VCO normally has its output buffered through one or two inverters. Attaching a large load capacitance on the output of the VCO can significantly affect the oscillation ISSN: 0975 – 6779| NOV 10 TO OCT 11 | VOLUME – 01, ISSUE - 02 Page 144 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION ENGINEERING The simulation of current starved VCO in spice tool as shown in figure 2 here control voltage referred as VinVCO set at 400mV. For the required condition of oscillation feedback is taken before the inverter stage. The results are shown in figure 1.3 the square wave start with a glitch which can be reduced which is explained later in this template for current starved VCO. For an output frequency of 200MHz, the input voltage, VinVCO , was set to 400mV. Figure 2 Current-Starved VCO Figure 3 Output Waveform of Current Starved VCO at VinVCO = 400mV ISSN: 0975 – 6779| NOV 10 TO OCT 11 | VOLUME – 01, ISSUE - 02 Page 145 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION ENGINEERING The input voltage is varied from 0 to 0.8V, in steps of 0.1V, and then time period is calculated at different values of voltages from the waveform. After that frequency is calculated by taking inverse of the time period. The Table 1 shows values of time periods and frequencies at different values of voltages. Similarly transfer characteristic of current starved VCO is shown in figure 4 which is almost linear as we predict at the time of designing. The big problem with this design is that the output oscillation frequency is not linearly related to the control voltage (easy to verify using the simulation that generated in figure 3).Having a nonlinear VCO gain can greatly reduce the quality of the performance of the DPLL (Digital Phase Locked Loop).The output of the PLL can jitter (move around) or may not lock at all when the VCO gain is nonlinear [4]. S r. N o. 1 2 3 4 5 6 7 8 Input Voltage(Vinv co) Time Period(ns) Frequency(M Hz) 0.2 V 0.3 V 0.35 V 0.4 V 0.5 V 0.6 V 0.7 V 0.8 V 67.0289 13.0901 7.40343 4.98927 3.478386 2.9721 2.811116 2.72532 14.9196 MHz 76.393 MHz 135.072 MHz 200.43 MHz 287.864 MHz 336.462 MHz 355.725 MHz 366.929 MHz of 400mV. Since Phase locked loop (PLL) is widely used in wireless communication systems, hence we can generate any desire frequency based on application requirements. 6. REFERENCES [1] B. Razavi, “Monolithic phase-locked loops and clock recovery circuits- theory and design”, IEEE Press,pp. 283-377 and 381-483, 1996. [2] M. Banu, “MOS oscillators with multi-decade tuning range and gigahertz maximum speed”, IEEE Journal of Solid-State Circuits, vol. 23, pp. 1386– 1393, December 1988. [3] D. A. Hodges and H.G. Jackson, “Analysis and design of Digital Integrated Circuits”,2nd edition, McGraw-Hill, 1988. [4] R. Jacob Baker, Harry W. Li and David E. Boyce, “CMOS Circuit Design, Layout and Simulation,” IEEE Press Series on Microelectronics Systems, pp. 355-361 and383-387, 2000. [5] M. Jamal Deen, “Ultra Low-Voltage Low-Power Voltage Controlled Oscillator”, Electrical and Computer Engineering Department, CRL 226 McMaster University, Hamilton, ON, Canada L8S 4K1. [6] M. J. Underhill, “Fundamentals of oscillator performance”, Electronics and Communication Engineering Journal, vol. 4, no. 4, pp. 185-193, 1992. [7] Paul R. Gray and Robert G. Meyer, “Analysis and Design of Analog Integrated Circuits”, 3rd edition, John Wiley, January 1993. Table 1 Variation of Frequency with Input Control Voltage (Vin VCO) Relationship between Control voltage (Volt) & Oscillating frequency (MHz) 400 300 200 100 0 0.2 0.3 0.35 0.4 0.5 0.6 0.7 0.8 V V V V V V V V Figure 4 Transfer characteristic of current starved VCO. 5. CONCLUSION In this paper we observed that in current starved voltage controlled oscillator (VCO) generates 200MHz frequency at input control voltage (VinVCO) ISSN: 0975 – 6779| NOV 10 TO OCT 11 | VOLUME – 01, ISSUE - 02 Page 146