LC082

advertisement

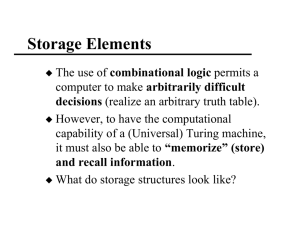

8. The Basic Bistable Memory Devices Circuit Delay Model The delay model of the basic S-R latch or basic NOR latch is shown in the picture. The input signal Q to the box labeled t (delay) is called as the next state output signal of the latch. The delayed output signal q is called as the present state output signal of the latch. Delay of output signal in the delay box t represents the worst-case delay from S X 1 the inputs of the latch till its output: t 2tpg , where tpg is signal propagation delay time in one gate. q Q values are called as next state values of output signal Q 1 t since these are the values that will shortly be present on the R delayed outputs. q values are called as present state values since they becomes equal to the next state output signal Q after the delay time t has elapsed: q Q after t. Delay model was necessary for establishing the terms: present state output signal, next state output signal. These terms are very important in sequential logic analysis and design. Example 8.4 Make up a delay model for the S-R NAND latch. Characteristic Equation Present state output signal q is feedback signal in input of a latch. It is referred as internal input signal of a latch, it records the history of the latch. The characteristic equation writes the next state output signal Q in terms of external inputs signals S and R, and internal input signal or present state output signal q in the same manner as one writes a combinational logic function: Q S + q + R (S + q) R SR + qR . Outlined equation is the characteristic equation of the S-R NOR latch. It illustrates why the present state output signal q is equal to Q after the delay time t. The equation is a sequential logic function since the variable Q (remember – q Q after t) appears on both sides of the equation, illustrating the feedback nature of the S-R NOR latch circuit. The next state value Q is a function of the external input signals S, R, and the present state value q. Example 8.5 Obtain the characteristic equation for the S-R NAND latch. Karnaugh Map A Karnaugh map with the internal input signal (present state output signal) q listed vertically and the external input signals S and R listed horizontally is useful in representing the information, contained in a characteristic equation. It is useful in two ways: as a reduction tool, and also as a tool to describe sequential logic circuit operation. 81 8. The Basic Bistable Memory Devices q SR 00 01 11 10 a 0 0 0 0 1 b 1 1 0 0 1 Q SR 11 – not norm ally allowed p1 p2 Next state output signal Q of basic S-R NOR latch is filled in Karnaugh map according the characteristic equation of the latch. We can check the accuracy of filling in a map writing down the characteristic equation of basic S-R NOR latch according the Karnaugh map in a usual way: Q p1 + p2 SR + qR . The 0s and 1s shown in the squares of map represent the next state output signal Q. When the next state output signal Q has the same value as the present state output signal q, the state of latch is stable (underlined 0s and 1s in Karnaugh map); otherwise, the state of latch is unstable. The present state output signal q 0 is referred to as a state of the circuit. State b represents the state of latch when present state output signal q 1. The S-R NOR latch can only exist in a stable state after the external input signals change and the present state output q is allowed time to settle (q Q after t). When the latch is in state a, the latch is stable for the input conditions SR 00, 01, or 11, since the next state output signal Q 0. When the latch is in state b, the latch is stable for the input conditions SR 00, or 10, since the next state output signal Q 1. Example 8.6 According the characteristic equation, obtained solving the problem in example 8.5, fill in a Karnaugh map for the basic S-R NAND latch. Underline the stable states of the latch. Flow Map Flow map is usually obtained from the Karnaugh map by replacing state values 0s and 1s with state symbols a, and b. The stable states in a flow map are underlined as in a Karnaugh map. The sequence of events in the latch is shown by arrows in the flow map. Consider that the latch is in a stable state and the external inputs change such that q q SR 2 remains in the same state a or in the same state b after t. In 00 01 11 10 this case, during the time interval t, a horizontal movement occurs in the flow map to the new stable state specified by the a 0 a a a b external input conditions. When the external inputs cause q to Q b 1 b a a b change in a different state (from a to b or from b to a) a horizontal movement in the flow map is required from the 1 stable state to unstable state, followed by a vertical movement SR 11 – not normally allowed to reach a stable state during the time interval t. Notice, that every flow starts and stops in the stable (underlined) state. Consider the following sequence beginning in stable state qSR 110. When the external inputs change to SR 00, during the time interval t the latch responds by moving from stable state b to stable state b at qSR 100 (a horizontal movement in the flow map shown by arrow 1 82 8. The Basic Bistable Memory Devices in the picture). If the external inputs are changed to SR 11, the latch responds during the time interval t by moving to unstable state a (a horizontal movement, shown by arrow 2) and then on to stable state a (a vertical movement , shown by arrow 2). The flow map visually demonstrates that transition of 1 q SR SR 11 to SR 00 is not allowed. If this happens, the next 00 01 11 10 stable state is dependent on the delays in the circuit: arrow 1 a 0 a a a b illustrates the case when delay time of signal in input S is less than delay time of signal in input R; arrow 2 illustrates the Q b 1 b a a b opposite case. The next stable state of the latch is different and unknown because a 'critical race condition' exists between the 2 two signals S and R. A 'critical race' occurs between two SR 11 – not normally allowed signals that are required to change at the same time and the next stable state is dependent on the delay paths in the circuit. This situation is undesirable and should never be allowed to happen, since the action of the circuit is unpredictable. One basic rule for asynchronous circuit operation is to allow only one external input signal to change at the same moment. When a race occurs between two signals that are required to change at the same time, and the next stable state is the same regardless of the delay paths in the circuit, then the race is 'no critical'. Fortunately all other race conditions for the S-R NOR latch are no critical. No critical race conditions are not a problem since the action of the circuit is predictable. Example 8.7 Draw a flow map illustrating no critical race conditions in the S-R NOR latch, when initial stable state is at qSR 001 and internal input signals SR change from 01 to 10. State Diagram A state diagram is a very popular tool of design and analysis of sequential circuits because it visually illustrates an operation of the sequential circuit. The state diagram is drawn up according the Karnaugh map or according the characteristic equation of the circuit. The circles in a state diagram represent the present state of output signal of the circuit: a in the circle represents q 0, a – q 0 SR b in the circle represents q 1. Arrows in the state b – q 1 01 11 diagram indicate state transitions when input signals change. SR The state diagram of S-R NOR latch is indi- SR 00 a 00 b cated on the picture. It shows that combination of 01 10 11 input signals SR 00 is a passive combination, it does not change the state of latch; combinations SR SR 10 10 and SR 01 are active combinations, they set SR 11 – not normally allowed and reset the latch. 83 8. The Basic Bistable Memory Devices Notice that besides the circle a are written down all combinations of input signals that refer to stable (underlined) states in the row q 0 in Karnaugh map. In similar way besides the circle b are written down all combinations of input signals that refer to stable (underlined) states in the row q 1 in Karnaugh map. The transition from a to b is a transition from an unstable state in row q 0 to the stable state that is in row q 1 below unstable state in row q 0. The transition from b to a is going on in the similar way. Algorithm of Operation Another name for a sequential logic circuit is a 'state machine'. Operation of this state machine can be described in a program way. There are a (q 0) and b (q 1) state boxes, and decision boxes in the algorithm of S-R NOR latch. When the latch is in the state a, only one combination of input signals SR 10 switches the latch to another b state, all other SR combinations send back the latch to the same a state. When the latch is in the state b, all combinations of input signals with R 1 switch latch to another b state, all combinations SR with R 0 send back the latch to the same b state. Example 8.8 Draw an algorithm of operation of S-R NAND latch. a 0 S R 1 b 0 R 1 Timing Diagram The operation of the S-R NOR latch can also be analyzed by observing its properties in the switching waveforms shown in the timing diagram. S This diagram is drawn up according the circuit delay model of the S-R NOR latch. Timing events in the circuit – changes of input signals – are enumerated R from 1 to 11. Propagation delays in the gates are estimated in the diagrams of output signals. Directed q line segments pointing from input transition to an output transition or from an output transition to another X output transition indicate the cause of events. Only timing events – changes of input signals – t 1 2 3 4 5 6 7 8 9 10 11 can cause the transition in output, on the other hand, there are timing events that do not switch the latch. 84 8. The Basic Bistable Memory Devices CONTROL QUESTIONS AND PROBLEMS 8.0.1. Formulate a definition of combinational logic. 8.0.2. Formulate a definition of sequential logic. 8.1. Elementary Memory Cell 8.1.1. Explain, how does a circuit of elementary memory cell made. Draw this circuit. 8.1.2. Explain an operation of bistable memory device, when: a) one of transistors is ON and another is OFF; b) both of transistors are OFF; c) both transistors are slightly ON. 8.1.3. Draw a logic diagram of the bistable memory device. 8.1.2. The Basic S-R Latches 8.2.1. Formulate a definition of a trigger. 8.2.2. Draw an electric diagram of basic S-R latch and explain its operation for all possible combinations of input signals. Draw a logic diagram and graphic symbol of basic S-R latch. 8.2.3. Which sets of input signals of NOR latch are referred as active, which – as passive, and which – as not normally allowed? 8.2.4. Draw a logic diagram and graphic symbol of basic SR latch. Which sets of input signals of NAND latch are active, passive and not normally allowed for this latch? 8.2.5. Which basic latches are used in TTL integrated devices, and which – in MOS and CMOS integrated devices? 8.2.6. Name all signals of delay model of basic latch. 8.2.7. Name logic function and logic variables in characteristic equation of basic latch. 8.2.8. According characteristic equation of basic NOR latch Q SR + qR fill in Karnaugh map of this latch. Which states of the latch are stable, and which – unstable? 8.2.9. According the Karnaugh map from problem 8.2.9 draw a state diagram of NOR latch. 8.2.10. Draw a timing diagram of NOR latch for S = 1001000110110, R = 0110010011100. 8.2.11. Analize an operation of sequential logic circuit shown in the Q S 1 picture: a) Draw the timing diagram waveforms of the signals S, R, Q, and Q, + 5V showing their logic values before the push-button switch is pressed, while the switch is being pressed, and after the switch is released. Q 1 A mechanical switch has a contact bounce when the contact comes to a R new position. In timing diagrams you can show only one bounce of the contact like broken 0-to-1 transition or broken 1-to-0 transition. b) Solve the same problem for the NAND latch. c) Discuss a suitability of S-R NOR and SR NAND latches for computer keyboard. 85