The State University of New York (SUNY) at Buffalo

Department of Electrical Engineering

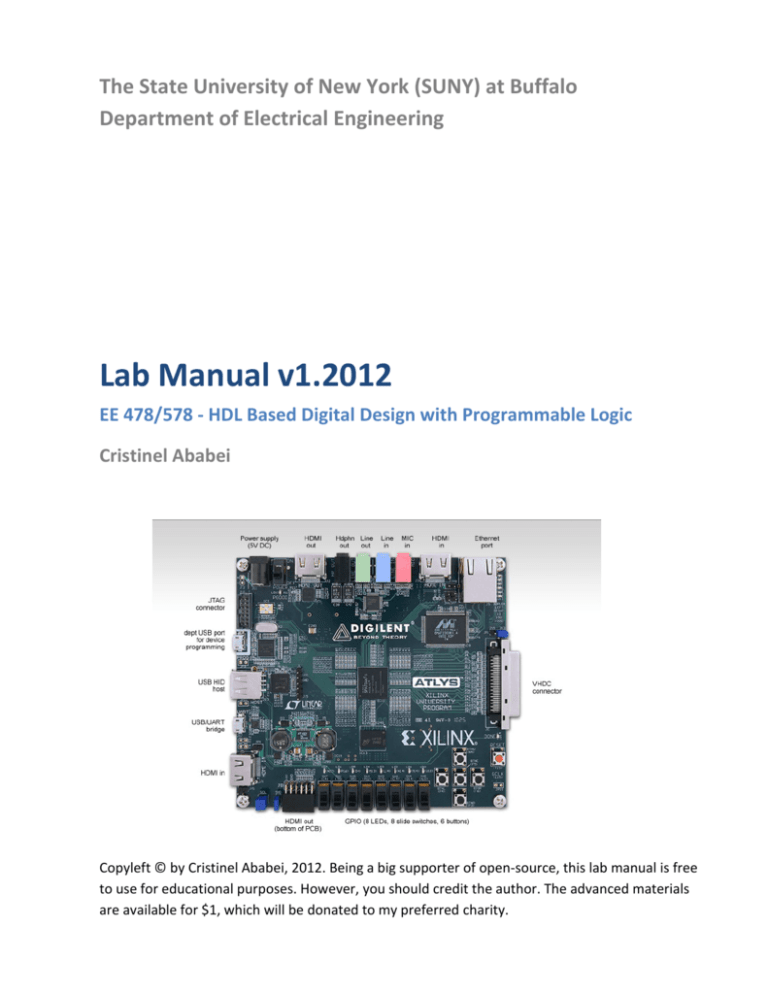

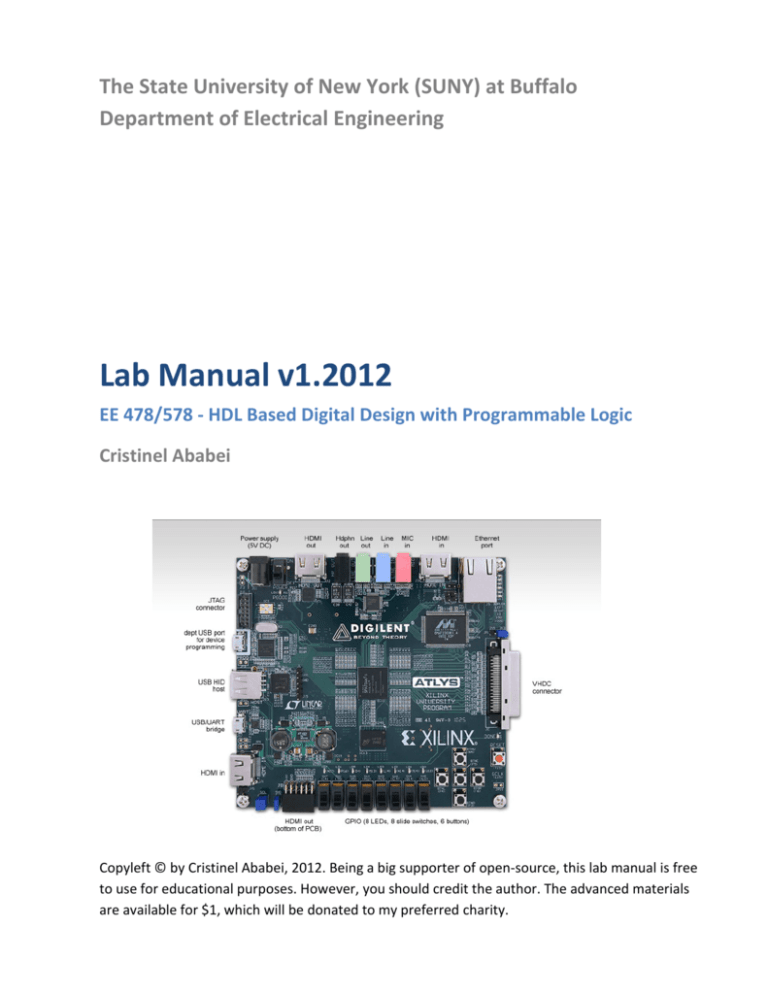

Lab Manual v1.2012

EE 478/578 - HDL Based Digital Design with Programmable Logic

Cristinel Ababei

Copyleft © by Cristinel Ababei, 2012. Being a big supporter of open-source, this lab manual is free

to use for educational purposes. However, you should credit the author. The advanced materials

are available for $1, which will be donated to my preferred charity.

Table of Contents

Lab 1: Aldec Active-HDL Tutorial...................................................................................................................... 3

Lab 1: Supplemental Material - A First Look at VHDL ................................................................................... 12

Lab 2: Xilinx ISE WebPack Tutorial ................................................................................................................. 16

Lab 2: Supplemental Material - Subprograms and Packages......................................................................... 25

Lab 3: Four-Bit Binary Counter....................................................................................................................... 30

Lab 3: Supplemental Material - Testbenches ................................................................................................ 35

Lab 4: Finite State Machines .......................................................................................................................... 41

Lab 4: Supplemental Material – Writing VHDL code for synthesis ................................................................ 50

Lab 5: Memories: ROMs and BRAMs Internal to the FPGA ........................................................................... 57

Lab 6: Memories: External SPI Flash and DDR2 ............................................................................................. 63

Lab 7: Interfacing FPGA Spartan-6 with AC’97 Codec .................................................................................... 68

Lab 7 Supplemental: PS2 Keyboard and UART .............................................................................................. 71

Lab 8: Interfacing FPGA Spartan-6 with Host Computer via USB .................................................................. 72

Lab 9: Video Interfaces: HDMI and DVI.......................................................................................................... 80

Lab 10: PicoBlaze – an embedded microcontroller ....................................................................................... 86

Lab 11: Single Cycle Computer (SCC) ............................................................................................................. 90

2

Lab 1: Aldec Active-HDL Tutorial

1. Objective

The objective of this tutorial is to introduce you to Aldec’s Active-HDL 9.1 Student Edition simulator by

performing the following tasks on a 4-bit adder design example:

Create a new design or add .vhd files to your design

Compile and debug your design

Run Simulation

Note: Active-HDL is an alternative simulator to Xilinx’s ISim (ISE Simulator) simulator. It is one of the

most popular commercial HDL simulators today. It is developed by Aldec. In this course, we use the free

student version of Active-HDL, which has some limitations (file sizes and computational runtime). You can

download and install it on your own computer:

http://www.aldec.com/en/products/fpga_simulation/active_hdl_student

2. Introduction

Active-HDL is a Windows based integrated FPGA Design Creation and Simulation solution. Active-HDL

includes a full HDL graphical design tool suite and RTL/gate-level mixed-language simulator. It supports

industry leading FPGA devices, from Altera, Atmel, Lattice, Microsemi (Actel), Quicklogic, Xilinx and

more.

The core of the system is an HDL simulator. Along with debugging and design entry tools, it makes up a

complete system that allows you to write, debug and simulate VHDL code. Based on the concept of a

workspace (think of it as of design), Active-HDL allows us to organize your VHDL resources into a

convenient and clear structure.

3. Procedure

Creating the 1-bit full adder

1. Start Aldec Active-HDL: Start->All Programs->Aldec->Active-HDL Student Edition

2. Select “Create New Workspace” and click OK

3. Enter fall2012_aldec as the name of the workspace and change the directory to where you want to save

it (for example M:\UB\labs) and click OK

4. Select “Create an Empty Design” and click NEXT

5. Choose the block diagram configuration as “Default HDL Language” and default HDL language as

“VHDL”. Select the target technology as Xilinx for vendor and SPARTAN6 for technology. Click

NEXT

6. Enter fourbit_adder as the name of the design as well as the name of the default working library. Click

NEXT

7. Click FINISH

You should have now the Design Browser as a window showing current workspace and design contents.

8. Double-click on “Add New File” in the Design Browser window

9. Select “VHDL Source Code” and type in full_adder in the name field, click OK

3

The following is the VHDL code for the 1-bit full adder. Enter the code as seen below into the empty file.

------

1-bit full adder

Declare the 1-bit full adder with the inputs and outputs

shown inside the port(). This adds two bits together (x,y)

with a carry in (cin) and outputs the sum (sum) and a

carry out (cout).

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity full_adder is

port(x, y, cin: in std_logic;

sum, cout: out std_logic);

end full_adder;

architecture my_dataflow of full_adder is

begin

sum <= (x xor y) xor cin;

cout <= (x and y) or (x and cin) or (y and cin);

end my_dataflow;

10. Select the File menu and choose Save.

11. To check sintax of the newly created adder, right click on “full_adder.vhd” in the Design Browser

window and select the Compile option. The code should compile without any problems and you should

see a green check mark next to the full_adder.vhd file. If you get any errors, check the code that you

have typed against the above code provided.

Once you have the source file (or all the source files of the entire design) compiled, the design can be

simulated for functional correctness.

Manual Simulation

Note: This type of simulation should be done only for small designs with few inputs and outputs. As design

size increases you should use testbenches – described later.

1. Select menu Simulation->Initialize Simulation

After the simulation has been initialized, you have to open a new Waveform window.

2. Click the New Waveform toolbar button to invoke the Waveform window.

Now you need assign the stimulators to all the input signals.

3. In the Design Browser window select all signals (one by one by holding Control key pressed), then

right click and choose Add to Wavefom

Note: To add signals to the simulator we could also use the drag and drop feature. In the Structure

pane/tab of the Design Browser window, select the design and while holding down the left button, drag it to

the right-section of the Waveform window and then release the mouse button. This is a standard drag-anddrop operation.

4

4. Go to the left pane/tab of the Waveform Editor window and select the “x” signal. Press the right button

to invoke a context menu, choose the “x” item from Stimulators… dialog; choose Clock for Type.

Leave the Frequency at the default value of 10 MHz. Click APPLY and then CLOSE

5. Repeat step 4 for input “y”. Choose Clock for Type but this time place the mouse pointer in the

Frequency box and set the value of 5 MHz. Click the APPLY button to assign the stimulator then

CLOSE.

6. Repeat step 4 for input “cin”. Choose Formula for Type and when the dialog appears, type formula

expression as follows: 0 0, 1 100000. Click APPLY and then CLOSE

7. Simulation->Run Until and enter 300ns

8. Finish simulation by selecting the Simulation->End Simulation option in the Simulation menu

At this time your Waveform viewer should look like this:

Investigate the waveforms to verify that your full_adder works correctly.

Testbench Based Simulation

The VHDL testbench is a VHDL program that describes simulation inputs in standard VHDL language.

There is a wide variety of VHDL specific functions and language constructs designed to create simulation

inputs. You can read the simulation data from a text file, create separate processes driving input ports, and

more. The typical way to create a testbench is to create an additional VHDL file for the design that treats

your actual VHDL design as a component (Design Under Test, DUT) and assigns specific values to this

component input ports. It also monitors the output response of the DUT to verify correct operation.

The diagram below illustrates the relationship between the entity, architecture, and testbench:

5

1. Create a new file full_adder_testbench.vhd and save it under the current design’s “src” directory (for

example M:\UB\labs\fall2012_aldec\fourbit_adder\src). The content of this file is in the Appendix A at

the end of this tutorial. You can create it using Aldec’s editor or any other editor (e.g., even Notepad).

2. Select the Design menu and choose “Add Files to Design” and add the newly created

full_adder_testbench.vhd to the design.

3. Right click on full_adder_testbench.vhd in the Design Browser window and select the Compile option.

4. Left click on the plus (+) next to full_adder_testbench.vhd. This will bring us the

TEST_FULL_ADDER entity

5. Right click on the TEST_FULL_ADDER and choose Set as Top-Level

6. Select the File menu and choose the New option and pick New Waveform

7. In the Design Browser window select the Structure pane/tab at the bottom of the window

8. Select the Simulation menu and choose Initialize Simulation

9. Click on “+” next to TEST_FULL_ADDER (MY_TEST)

10. Click on U1:FULL_ADDER and drag all signals to the waveform window

11. Change the time for simulation to 400 ns by clicking on the up arrow

12. Select the Simulation menu and choose Run For

13. Inspect the simulation to verify that the 1-bit full adder functionality is indeed correct

At this time your Waveform viewer should look like this:

Creating and testing the 4-bit adder

1. Add the following two files to the design: fourbit_adder.vhd and fourbit_adder_testbench.vhd.

Their source code is in Apendices B and C at the end of this tutorial.

2. Compile both files and use the testbench (fourbit_adder_testbench.vhd) to simulate the design for say

200 ns

3. View the simulation to verify that the 4-bit adder functionality is correct.

At this time your Waveform viewer should look like this:

6

4. Taking it further

While intuitive to use, Active-HDL has a lot of features. It is outside the scope of this tutorial to discuss all

of them. You should spend some time searching and reading additional documentation on how to use

Active-HDL. A few first examples:

http://www.aldec.com/en/downloads/tutorials

Once you launched Active-HDL tool select the Help menu and read stuff

Google for “Active-HDL tutorial”. You will find a lot of detailed tutorials (some written for older

versions of the tool but a lot of concepts still apply), which have been kindly made public by the online

community.

Note: As it is the case with most of the electronic design automation (EDA) tools, there are multiple ways of

achieving or performing something. If by reading the documentation or other tutorials you learn how to

accomplish any of the steps described in this tutorial in a different way - that is OK. You should learn and

use the methods you like the most and are more comfortable with.

Finally, while Active-HDL (of Aldec) and ModelSim (of Mentor Graphics) are arguably some of the most

popular HDL simulators in industry, Xilinx has been improving their own simulator, ISim, which is part of

the free ISE WebPack used in this course. You can read more about iSim here:

http://www.xilinx.com/support/documentation/sw_manuals/xilinx13_4/plugin_ism.pdf

7

Appendix A: VHDL source code of full_adder_testbench.vhd

------

1-bit full adder testbench

A testbench is used to rigorously tests a design that you have made.

The output of the testbench should allow the designer to see if

the design worked. The testbench should also report where the testbench

failed.

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Declare a testbench. Notice that the testbench does not have any input

-- or output ports.

entity TEST_FULL_ADDER is

end TEST_FULL_ADDER;

-- Describes the functionality of the tesbench.

architecture MY_TEST of TEST_FULL_ADDER is

-- The object that we wish to test is declared as a component of

-- the test bench. Its functionality has already been described elsewhere.

-- This simply describes what the object's inputs and outputs are, it

-- does not actually create the object.

component FULL_ADDER

port( x, y, cin : in STD_LOGIC;

sum, cout : out STD_LOGIC );

end component;

-- Specifies which description of the adder you will use.

for U1: FULL_ADDER use entity WORK.FULL_ADDER(MY_DATAFLOW);

-- Create a set of signals which will be associated with both the inputs

-- and outputs of the component that we wish to test.

signal X_s, Y_s

: STD_LOGIC;

signal CIN_s

: STD_LOGIC;

signal SUM_s

: STD_LOGIC;

signal COUT_s

: STD_LOGIC;

-- This is where the testbench for the FULL_ADDER actually begins.

begin

-- Create a 1-bit full adder in the testbench.

-- The signals specified above are mapped to their appropriate

-- roles in the 1-bit full adder which we have created.

U1: FULL_ADDER port map (X_s, Y_s, CIN_s, SUM_s, COUT_s);

-- The process is where the actual testing is done.

process

begin

-- We are now going to set the inputs of the adder and test

-- the outputs to verify the functionality of our 1-bit full adder.

-- Case 0 : 0+0 with carry in of 0.

-- Set the signals for the inputs.

X_s <= '0';

Y_s <= '0';

CIN_s <= '0';

-- Wait a short amount of time and then check to see if the

-- outputs are what they should be. If not, then report an error

-- so that we will know there is a problem.

wait for 10 ns;

8

assert ( SUM_s = '0' ) report "Failed Case 0 - SUM" severity error;

assert ( COUT_s = '0' ) report "Failed Case 0 - COUT" severity error;

wait for 40 ns;

-- Carry out the same process outlined above for the other 7 cases.

-- Case 1 : 0+0 with carry in of 1.

X_s <= '0';

Y_s <= '0';

CIN_s <= '1';

wait for 10 ns;

assert ( SUM_s = '1' ) report "Failed Case 1 - SUM" severity error;

assert ( COUT_s = '0' ) report "Failed Case 1 - COUT" severity error;

wait for 40 ns;

-- Case 2 : 0+1 with carry in of 0.

X_s <= '0';

Y_s <= '1';

CIN_s <= '0';

wait for 10 ns;

assert ( SUM_s = '1' ) report "Failed Case 2 - SUM" severity error;

assert ( COUT_s = '0' ) report "Failed Case 2 - COUT" severity error;

wait for 40 ns;

-- Case 3 : 0+1 with carry in of 1.

X_s <= '0';

Y_s <= '1';

CIN_s <= '1';

wait for 10 ns;

assert ( SUM_s = '0' ) report "Failed Case 3 - SUM" severity error;

assert ( COUT_s = '1' ) report "Failed Case 3 - COUT" severity error;

wait for 40 ns;

-- Case 4 : 1+0 with carry in of 0.

X_s <= '1';

Y_s <= '0';

CIN_s <= '0';

wait for 10 ns;

assert ( SUM_s = '1' ) report "Failed Case 4 - SUM" severity error;

assert ( COUT_s = '0' ) report "Failed Case 4 - COUT" severity error;

wait for 40 ns;

-- Case 5 : 1+0 with carry in of 1.

X_s <= '1';

Y_s <= '0';

CIN_s <= '1';

wait for 10 ns;

assert ( SUM_s = '0' ) report "Failed Case 5 - SUM" severity error;

assert ( COUT_s = '1' ) report "Failed Case 5 - COUT" severity error;

wait for 40 ns;

-- Case 6 : 1+1 with carry in of 0.

X_s <= '1';

Y_s <= '1';

CIN_s <= '0';

wait for 10 ns;

assert ( SUM_s = '0' ) report "Failed Case 6 - SUM" severity error;

assert ( COUT_s = '1' ) report "Failed Case 6 - COUT" severity error;

wait for 40 ns;

-- Case 7 : 1+1 with carry in of 1.

X_s <= '1';

Y_s <= '1';

CIN_s <= '1';

9

wait for

assert (

assert (

wait for

10 ns;

SUM_s = '1' ) report "Failed Case 7 - SUM" severity error;

COUT_s = '1' ) report "Failed Case 7 - COUT" severity error;

40 ns;

end process;

END MY_TEST;

Appendix B: VHDL source code of fourbit_adder.vhd

-----

4-bit adder

Structural description of a 4-bit adder. This device

adds two 4-bit numbers together using four 1-bit full adders

described above.

-- This is just to make a reference to some common things needed.

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-----

This describes

designing. The

inside port().

and produces a

the black-box view

inputs and outputs

It takes two 4-bit

4-bit output (ANS)

of the component we are

are again described

values as input (x and y)

and a carry out bit (Cout).

entity fourbit_adder is

port( a, b

: in

STD_LOGIC_VECTOR(3 downto 0);

z : out STD_LOGIC_VECTOR(3 downto 0);

cout

: out STD_LOGIC );

end fourbit_adder;

-- Although we have already described the inputs and outputs,

-- we must now describe the functionality of the adder (ie:

-- how we produced the desired outputs from the given inputs).

architecture MY_STRUCTURE of fourbit_adder is

-- We are going to need four 1-bit adders, so include the

-- design that we have already studied in full_adder.vhd.

component FULL_ADDER

port( x, y, cin

sum, cout

end component;

: in STD_LOGIC;

: out STD_LOGIC );

-- Now create the signals which are going to be necessary

-- to pass the outputs of one adder to the inputs of the next

-- in the sequence.

signal c0, c1, c2, c3 : STD_LOGIC;

begin

c0 <= '0';

b_adder0: FULL_ADDER

b_adder1: FULL_ADDER

b_adder2: FULL_ADDER

b_adder3: FULL_ADDER

port

port

port

port

map

map

map

map

(a(0),

(a(1),

(a(2),

(a(3),

b(0),

b(1),

b(2),

b(3),

c0,

c1,

c2,

c3,

z(0),

z(1),

z(2),

z(3),

c1);

c2);

c3);

cout);

END MY_STRUCTURE;

Appendix C: VHDL source code of fourbit_adder_testbench.vhd

-- 4-bit Adder Testbench

-- A testbench is used to rigorously tests a design that you have made.

10

-- The output of the testbench should allow the designer to see if

-- the design worked. The testbench should also report where the testbench

-- failed.

-- This is just to make a reference to some common things needed.

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Declare a testbench. Notice that the testbench does not have any

-- input or output ports.

entity TEST_FOURBIT_ADDER is

end TEST_FOURBIT_ADDER;

-- Describes the functionality of the tesbench.

architecture MY_TEST of TEST_FOURBIT_ADDER is

component fourbit_adder

port( a, b

: in

z

: out

cout

: out

end component;

STD_LOGIC_VECTOR(3 downto 0);

STD_LOGIC_VECTOR(3 downto 0);

STD_LOGIC);

for U1: fourbit_adder use entity WORK.FOURBIT_ADDER(MY_STRUCTURE);

signal a, b

: STD_LOGIC_VECTOR(3 downto 0);

signal z

: STD_LOGIC_VECTOR(3 downto 0);

signal cout

: STD_LOGIC;

begin

U1: fourbit_adder port map (a,b,z,cout);

process

begin

-- Case 1 that we are testing.

a <= "0000";

b <= "0000";

wait for 10 ns;

assert ( z = "0000" ) report "Failed Case 1 - z" severity error;

assert ( Cout = '0' ) report "Failed Case 1 - Cout" severity error;

wait for 40 ns;

-- Case 2 that we are testing.

a <= "1111";

b <= "1111";

wait for 10 ns;

assert ( z = "1110" ) report "Failed Case 2 - z" severity error;

assert ( Cout = '1' )

report "Failed Case 2 - Cout" severity error;

wait for 40 ns;

end process;

END MY_TEST;

11

Lab 1: Supplemental Material - A First Look at VHDL

The objective of this supplemental material is to give you an early presentation of some of the most

important concepts in VHDL. You should keep this document as a reference for future work on your course

assignments.

------------------------------------------------------------------ entity & architecture template

----------------------------------------------------------------library lib_name;

use lib_name.package_name.all;

entity entity_name is

generic (

generic_name : type_name := default;

generic_name : type_name := default

);

port (

port_name : in|out|inout|buffer|linkage type_name;

ort_name : in|out|inout|buffer|linkage type_name

);

end entity_name;

architecture arch_name of entity_name is

signal signal_name : type_name := default;

begin

concurrent assignments and processes;

end arch_name;

------------------------------------------------------------------ component declaration

----------------------------------------------------------------component component_name

generic (

generic_name : type_name := default;

generic_name : type_name := default

);

port (

port_name : in|out|inout|buffer|linkage type_name;

port_name : in|out|inout|buffer|linkage type_name

);

end component_name;

------------------------------------------------------------------ component instantiation

----------------------------------------------------------------instance_name : component_name

generic map (

generic_name => value,

generic_name => value

);

port map (

port_name => value,

12

port_name => value

);

------------------------------------------------------------------ process template

----------------------------------------------------------------process_name : process( signal_port_name, signal_port_name )

variable var_name : type_name := default;

begin

...

end process process_name;

------------------------------------------------------------------ concurrent signal assignments

----------------------------------------------------------------signal_name <= value;

signal_name <= transport value after time_value,

transport value after time_value;

access_name <= new type_name ( initial_value );

signal_name <= value1 when ( condition1 ) else

value2 when ( condition2 ) else

value3;

with expression select

signal_name <= value1 when choice1,

value2 when choice2,

value3 when others;

------------------------------------------------------------------ type declarations

----------------------------------------------------------------type type_name is ( ENUM1, ENUM2, ENUM3 );

type type_name is range low_integer to high_integer

units

base_unit;

unit1 = integer base_unit;

unit2 = integer unit1;

end units;

type type_name is array ( low_index to high_index ) of element_type;

type type_name is array ( high_index downto low_index ) of element_type;

type type_name is array ( scalar_type1 range <> ) of element_type;

type type_name is array ( index1, index2 ) of element_type;

type type_name is

record

element_name : type_name;

element_name : type_name;

end record;

type record_type_name;

type pointer_type_name is access record_type_name;

type record_type_name is

record

next_record : pointer_type_name;

end record;

type file_type_name is file of type_name;

subtype subtype_name is scalar_type range low to high;

subtype subtype_name is array_type( left downto/to right );

subtype subtype_name is resolution_fn type_name;

13

------------------------------------------------------------------ signal/constant/variable declarations

----------------------------------------------------------------signal signal_name : type_name := default;

constant const_name : type_name := value;

variable var_name : type_name := default;

file file_id : file_type is in/out file_name;

------------------------------------------------------------------ procedure & function declaration

----------------------------------------------------------------procedure proc_name ( constant/variable/signal param : in/out/inout type_name

);

procedure proc_name ( param1 : type_name; param2 : type_name );

function fn_name ( constant/variable/signal param : in/out/inout type_name )

return type_name;

function fn_name ( param1 : type_name; param2 : type_name ) return type_name;

------------------------------------------------------------------ procedure & function body

----------------------------------------------------------------procedure proc_name ( constant/variable/signal param : in/out/inout type_name )

is

variable var_name : type_name := default;

begin

statements;

end proc_name;

function fn_name ( constant/variable/signal param : in/out/inout type_name )

return type_name is

variable var_name : type_name := default;

begin

statements;

return value;

end proc_name;

------------------------------------------------------------------ if statement

----------------------------------------------------------------if ( condition1 ) then

statements;

elsif ( condition2 ) then

statements;

else

statements;

end if;

------------------------------------------------------------------ case statement

----------------------------------------------------------------case signal/variable is

when value1 => statements;

when value2 => statements;

when others => statements;

14

end case;

------------------------------------------------------------------ while loop

----------------------------------------------------------------label : while ( condition ) loop

statements;

end loop label;

------------------------------------------------------------------ for loop

----------------------------------------------------------------label : for var_name in left to/downto right loop

statements;

end loop label;

------------------------------------------------------------------ assert statement

----------------------------------------------------------------assert ( condition )

report string_value

severity severity_value;

------------------------------------------------------------------ package declaration and body

----------------------------------------------------------------package pkg_name is

declarations;

end pkg_name;

package body pkg_name is

definitions;

end pkg_name;

------------------------------------------------------------------ configurations

----------------------------------------------------------------configuration cfg_name of entity_name is

for arch_name

end for;

end cfg_name;

configuration cfg_name of entity_name is

for arch_name

for instance_name : comp_name use entity entity_name ( architecture );

for instance_name : comp_name

for arch_name

end for;

for instance_name : comp_name use configuration cfg_name2;

for others : comp_name use configuration cfg_name2;

for all : comp_name use configuration cfg_name2;

end for;

end cfg_name;

15

Lab 2: Xilinx ISE WebPack Tutorial

1. Objective

To introduce you to Xilinx’s ISE WebPack by performing the following tasks on a 4-bit adder design

example:

Use Xilinx ISE WebPack software to:

o Specify the type of FPGA to be programmed

o Assign input and output signals to FPGA pins

o Implement the design (producing a bit file)

o Generate reports

Use Digilent Adept software to:

o Select the board to be programmed: Digilent ATLYS FPGA board

o Select the bit file to be used

o Program the FPGA board

Test the design on the ATLYS board

2. Introduction

In this course, we use Xilinx ISE WebPack 14.1 to synthesize our designs. The target FPGA is Xilinx

Spartan-6. This FPGA is mounted on a board called Atlys by Digilent. The Atlys circuit board is a

complete, ready-to-use digital circuit development platform based on a Xilinx Spartan-6 LX45 FPGA. It

offers a large on-board collection of high-end peripherals including Gbit Ethernet, HDMI Video, 128MByte

16-bit DDR2 memory, and USB and audio ports.

A typical design flow is illustrated in the next figure:

Aldec Active-HDL or Xilinx ISim

Specify design functionality

Define inputs and outputs

Write VHDL files; create testbenches

Compile, simulate, and debug

Previous tutorial (lab 1)

VHDL file (e.g., MyFile.vhd)

This tutorial (lab 2)

Xilinx ISE WebPack

Specify FPGA (Spartan-6, etc.)

Assigns signals to pins

Implement design (synthesis, place, route)

Generate reports

Generate bitstream file (to program FPGA)

bit file (e.g., MyFile.bit)

Digilent Adept or Xilinx iMPACT

Program to download bit file to the FPGA on

the Atlys board

USB

3. Procedure: Design Implementation with Xilinx ISE WebPack

16

3.1 Start Xilinx ISE

Launch Xilinx ISE using the shortcut on the desktop (or Start->All Programs->Xilinx Design Tools->ISE

Design Suite 14.1->ISE Design Tools->Project Navigator)

3.2 Create a Project

--Click “New Project” button or Select File->New Project

--Enter the project name fourbit_adder and select the location where you want it to be saved. For example,

M:\UB\labs\fall2012_ise.

--Select HDL for Top-Level source type and click Next. You should get the Project Settings window.

3.3 Specify the FPGA to be Used

--In the Project Settings window, select Spartan6 for Family, select XC6SLX45 for Device, select CSG324

for Package, and VHDL for Preferred Language. Leave the rest of the options unchanged (see figure

below). Then, click Next.

--You should get a Project Summary window. Click Finish to create the project.

17

3.4 Add Existing Source Files to Project

--Select Project->Add Source and locate the vhd files for our design. In this example, we will use the

full_ader.vhd and fourbit_adder.vhd files that we have already created in lab1. So, go ahead and locate

them and add them to the project, then click Open.

--At this time, you should see the Design Overview - Summary being displayed.

3.5 Implement the Design

Design implementation is the process of translating, mapping, placing, routing, and generating a bitstream

file for your design. The design implementation tools are embedded in the Xilinx ISE software for easy

access and project management. The figure below illustrates the design implementation step within a typical

FPGA design flow.

Design

Implementation

Mapping

Placement

Routing

Bitstrean

generation

To perform the design implementation of our fourbit_adder follow these steps:

--In the Hierarchy window, select “fourbit_adder – MY_STRUCTURE (fourbit_adder.vhd)”

--In the Processes tab double-click Implement Design (or right-click on Implement Design and select

Run). During and after the run, you should see:

Lots of information should scroll by in the Console window. If any errors occur, scroll back up to

read the messages and figure out how to fix the errors.

Green check marks appear next to the processes that have been run

Information filled out in the Design Overview – Summary window. For example:

o Note that this simple example only uses 4 out of 27,288 available LUTs

o This example has 2 inputs (“a” and “b”, each has four bits) and 2 outputs (“z” has four bits and

“cout” is a single bit), so only 13 of 218 input-output blocks (IOB) are used.

The next figure shows how the Project Navigator window looks like after Implementation run finished:

18

3.6 ATLYS Pinout

The Atlys board includes six pushbuttons, eight slide switches, and eight LEDs for basic digital input and

output. One pushbutton has a red plunger and is labeled “reset” on the PCB - this button is no different than

the other five, but it can be used as a reset input to processor systems. The buttons and slide switches are

connected to the FPGA via series resistors to prevent damage from inadvertent short circuits. The high

efficiency LED anodes are connected to the FPGA via 390-ohm resistors, and they will illuminate when a

logic high voltage is applied to their respective I/O pin. The next figure shows the connection of the

pushbuttons, slide switches, and LEDs to the FPGA’s pins:

Note: Now it’s a good time to take a while and read through the reference manual of Atlys board to get

familiar with the rest of pinouts. You can download it directly from Digilent:

http://www.digilentinc.com/Data/Products/ATLYS/Atlys_rm.pdf

19

Also, take some time to read through some of the documentation of Spartan-6 FPGA:

http://www.xilinx.com/support/documentation/spartan-6.htm

Because our fourbit_adder design is pretty small, we can actually conveniently assign the eight slide

switches to control the two inputs and use five LEDs to be driven by the outputs. We will use the first four

slide switches (SW0-SW3) as input “a” and the last four slide switches (SW4-SW7) as input “b” of the

fourbit_adder. The output “z” of the fourbit_adder will drive the first four LEDs (LD0-LD3) and the output

“cout” will drive the last LED (LD7).

3.7 Assigning Pins

--Expand (+) User Constraints under the Processes tab

--Double-click on I/O Pin Planning (PlanAhead) - Post-Synthesis

--Select Yes to create a User Constraint File (UCF)

--The PlanAhead 14.1 window should now appear; it may take a few seconds though.

If a Welcome window appears, you can simply close it.

If a window appears asking if you would like to load software updates, select No.

--Expand (+) a(4), b(4), z(4), and Scalar ports under the I/O Ports tab to reveal all the inputs and outputs.

--Double-click on signal a(0) to open the I/O Port Properties window.

--Enter the desired pin number A10 for signal a[0] in the box labeled Site.

--Click Apply.

--Repeat for the rest of the signals a, b, z, and cout using the pin numbers determined earlier and shown in

the previous figure.

--Check the pin numbers now listed in the I/O Ports tab to be sure that they are correct.

The PlanAhead window should look like in the next figure:

20

3.8 Printing the Package View

Note: This step is optional. It is described here for the sake of completeness. To save a tree, do not actually

print.

Before printing the package view, change the background from black to white as follows:

--Bring the mouse pointer within the Package window, then Right-click and select View – Options

--When the Options window opens, change the PlanAhead Default Theme to PlanAhead Light Theme under

Colors option. Click Apply. Notice that the package now has a light color background.

--At this time you could select File->Print and the Package View will print. However, do not do it. Instead,

in the Package window zoom-in to pin A10 and verify that it is assigned to a[0]: you should see a[0] written

inside the cell at location row A column 10. Verify the correct assignment of the other pins as well.

--Select File->Save Project

--Select File->Exit

--Select OK

3.9 Re-Implementing the Design after Pins Assignment

--The Xilinx ISE screen should now again appear and a question mark (?) should appear next to

Implement Design indicating that the design is no longer current (since we assigned pins).

--Double-click on Implement Design to implement the design again using the assigned pins.

--The (?) next to Implement Design should now have been replaced by a green check again.

3.10 Generating the Programming File

--Double-click on Generate Programming File in the Process tab. This step will generate the bit file

(fourbit_adder.bit in this example) that will be downloaded to the FPGA in a later step. A green check

mark should appear after it has successfully run.

3.11 Viewing and Printing Reports

Note: Again, this step is described for completeness; do not actually do the printing.

--The Design Summary tab shows that several types of reports are available. Click on Summary, IOB

Properties, Pinout Report, etc. reports and take some time to read through and understand them. For

example, notice in the Static Timing report that the longest path delay of 14.427 ns is between input bit

a<0> and output cout.

--You could print any of these reports by selecting File->Print.

--An alternative to printing the Pinout Report is to print the User Configuration File (UCF). Look in the

project folder for a file with a ucf extension (fourbit_adder.ucf in this case). Open the file with any text

editor. Notice that this file only contains information on pins that were assigned.

--A schematic can be printed as follows:

Select Tools->Schematic Viewer->RTL. When you do this first time, we are asked to select the

Viewer Startup Mode; leave it as “Start with the Explorer Wizard”. At this time you should get a

new dialog window, “Create RTL Schematic”.

Expand the (+) sign of the Signals area, select all of the signals, and click the “Add ->” button.

21

Click Create Schematic button. The schematic now appears as shown in the figure below. Double

click on the full_adder box to go lower into the hierarchy of the design.

You could print it by selecting File->Print to print the schematic (the background changes to white).

3.12 Save and Close the Project

--Select File->Save

--Select File->Close Project

--Select File->Exit to shut down Xilinx ISE

3.13 Opening an existing project

--If you need to open an existing project, look in the project folder for a file with an .xise extension

(full_adder.xise in this example).

--If you modify the VHDL source code you must run again Implement Design and Generate Programming

File. There is no need to run PlanAhead and assign signals to pins since the UCF file still exits - unless you

added/changed inputs or outputs.

4. Procedure: FPGA Programming with Digilent Adept

Digilent Adept is a free program available from Digilent to download synthesized designs (bit files) onto

Digilent FPGA boards.

4.1 Method 1: Direct programming via USB cable

To program the Atlys board using Adept software, first set up the board and initialize the software:

--Plug in and attach the power supply

--Plug in the USB cable to the PC and to the USB port on the board – the one marked “PROG” on the

board’s PCB (this is the so called Adept USB port).

--Turn ON Atlys’ power switch

--Start the Adept software

--Wait for the FPGA to be recognized.

If everything is properly connected and powered-up, the software should recognize the board as indicated in

the figure below.

22

--Select the Browse… button next to the FPGA box and locate the bit file generated by the Xilinx ISE

WebPack software. In this example, the file is fourbit_adder.bit, located in the project folder created in the

previous section of this tutorial.

--If everything is ok, then the Adept software should print the message “Programming Successful” once the

programming is finished.

--Congratulations! You just programmed the Spartan-6 FPGA to implement the fourbit_adder

design!

Use the slide switches to set inputs “a” and “b” and watch the LEDs to verify that the adder works correctly.

Try different combinations of input values. For example, if we wanted to test a + b = 2 + 5 = 7 we would set

input a = 0010 and b = 0101 via the slide switches and the output should turn the LEDs on as shown in the

figure below.

b[0-3]

a[0-3]

4.2 Method 2: Programming from Flash memory

--Turn the Atlys FPGA board OFF and then ON again. Note that the design has been lost!

23

Recall that the LUTs in an FPGA are essentially RAM and their contents are lost when power is turned off.

The Atlys board also contains 16Mbyte x4 SPI Flash, which can be used to permanently store the

configuration file of our design.

--To program the SPI Flash ROM, select the “Flash” tab in the Adept’s software window.

--In the “FPGA Programming File” section click Browse… and locate the fourbit_adder.bit file and then

click Program. If everything went ok, you should get the message “Flash configuration successful”.

--Turn the FPGA board OFF and then ON again. The SPI Flash ROM is automatically transferred to the

FPGA at power-on.

--Disconnect the USB cable and turn the power switch OFF and ON again. Note that the design should still

work!

4.3 Other programming methods

As mentioned in the Reference Manual of the Atlys board (link to it provided earlier), the FPGA can be

programmed also via the JTAG interface. In addition, the programming file can be transferred from a USB

memory stick attached to the USB HID port (the one marked J13 on the board’s PCB).

It is left as an assignment for you to search and read through the documentation to figure out how exactly

programming from an USB memory stick can be done.

5. Taking it further

As you already realized, Xilinx ISE WebPack is a sophisticated software with lots of features. It is outside

the scope of this tutorial to discuss all of them. You should spend time on your own to search and read

additional documentation and tutorials. A few first examples:

Xilinx’s ISE In-Depth Tutorial:

http://www.xilinx.com/support/documentation/sw_manuals/xilinx14_1/ise_tutorial_ug695.pdf

Digilent’s ISE WebPack VHDL Tutorial:

http://www.digilentinc.com/Data/Documents/Tutorials/Xilinx%20ISE%20WebPACK%20VHDL%20T

utorial.pdf

Digilent’s Adept Software Advanced Tutorial:

http://digilentinc.com/Data/Documents/Tutorials/Adept%20Software%20Advanced%20Tutorial.pdf

Once you launched the ISE tool select the Help menu and read stuff

Google for “ISE WebPack tutorial”. You will find a lot of detailed tutorials (some written for older

versions of the tool but a lot of concepts still apply), which have been kindly made public by the online

community.

Note: As it is the case with most of the electronic design automation (EDA) tools, there are multiple ways of

achieving or performing something. If by reading the documentation or other tutorials you learn how to

accomplish any of the steps described in this tutorial in a different way - that is OK. You should learn and

use the methods you like the most and are more comfortable with.

24

Lab 2: Supplemental Material - Subprograms and Packages

The objective of this supplemental material is to introduce you to the concepts of subprograms (functions

and procedures) and packages in VHDL.

1. VHDL Functions

A function executes a sequential algorithm and returns a single value to the calling program. We

can think of a function as a generalization of expressions. The syntax rule for a function

declaration is:

[pure | impure] function identifier [(parameter_interface_list)]

return type_mark is

{subprogram declarations}

begin

{sequential statements}

end [function] [identifier];

By default (i.e., if no keyword is given), functions are declared as pure. A pure function does not

have access to a shared variable, because shared variables are declared in the declarative part of the

architecture and pure functions do not have access to objects outside of their scope. Only

parameters of mode 'in' are allowed in function calls and are treated as 'constant' by default.

Functions may be used wherever an expression is necessary within a VHDL statement.

Subprograms themselves, however, are executed sequentially like processes. Similar to a process,

it is also possible to declare local variables. These variables are initialized with each function call

with the leftmost element of the type declaration (boolean: false, bit: '0'). The leftmost value of

integers is guaranteed to be at least -(2^31)-1 (i.e. zeros must be initialized to 0 at the beginning of

the function body). It’s recommended to initialize all variables in order to enhance the clarity of

the code.

Example 1: The following VHDL code describes a simple function that adds two 4-bit vectors and

a carry in and returns a 5-bit sum:

function add4_func(a, b : std_logic_vector(3 downto 0); carry: std_logic)

return std_logic_vector is

variable cout : std_logic;

variable cin : std_logic;

variable sum : std_logic_vector(4 downto 0);

begin

cin := carry;

sum := "00000";

loop1 : for i in 0 to 3 loop

cout := (a(i) and b(i)) or (a(i) and cin) or (b(i) and cin);

sum(i) := a(i) xor b(i) xor cin;

cin := cout;

end loop loop1;

sum(4) := cout;

return sum;

25

end add4_func;

Question: what is the role of the statement: cin := cout; inside loop1?

2. VHDL Procedures

Procedures, in contrast to functions, are used like any other statement in VHDL. Consequently,

they do not have a return value, although the keyword 'return' may be used to indicate the

termination of the subprogram. Depending on their position within the VHDL code, either in an

architecture or in a process, the procedure as a whole is executed concurrently or sequentially,

respectively.

Procedures facilitate decomposition of VHDL code into modules. They can return any number of

values using output parameters. The default mode of a parameter is 'in', the keyword 'out' or 'inout'

is necessary to declare output signals/variables. The syntax rule for a procedure declaration is:

procedure identifier [(parameter_interface_list)] is

{subprogram declarations}

begin

{sequential statements}

end [procedure] [identifier];

Example 2: The following procedure does basically the same thing as the function in the previous

example:

procedure add4_proc

(a, b : in std_logic_vector(3 downto 0);

carry : in std_logic;

signal sum : out std_logic_vector(3 downto 0);

signal cout : out std_logic) is

variable c : std_logic;

begin

c := carry;

for i in 0 to 3 loop

sum(i) <= a(i) xor b(i) xor c;

c := (a(i) and b(i)) or (a(i) and c) or (b(i) and c);

end loop;

cout <= c;

end add4_proc;

3. Packages and libraries

Packages and libraries provide a convenient way of referencing frequently used functions and

components. Packages are the only language mechanism to share objects among different design

units. Usually, they are designed to provide standard solutions for specific problems (e.g., data

types and corresponding subprograms like type conversion functions for a certain bus protocol,

procedures and components (macros) for signal processing purposes, etc.).

A package consists of a package declaration and an optional package body. The package

declaration contains a set of declarations, which may be shared by several design units (for

26

example: types, signals, components, and function and procedure declarations). The body package

usually contains the functions and procedure bodies.

The syntax rule for a package declaration is:

package identifier is

{package declarations}

begin

{sequential_statement}

end [package] [identifier];

A package is analyzed separately and placed in the working library by the analyzer. Each package

declaration that includes function and/or procedure declarations must have a corresponding

package body. The syntax rule for a package body is:

package body identifier is

{package body declarations}

end [package body] [identifier];

Example 3: Simple package declaration and its corresponding body.

library IEEE;

use IEEE.std_logic_1164.all;

package my_package is

function add4_func(a, b: std_logic_vector(3 downto 0); carry : std_logic)

return std_logic_vector;

procedure add4_proc

(a, b: in std_logic_vector(3 downto 0);

carry: in std_logic;

signal sum: out std_logic_vector(3 downto 0);

signal cout: out std_logic);

end package my_package;

Since the package contains subprogram declarations, we declare also the package body:

package body my_package is

function add4_func(a, b: std_logic_vector(3 downto 0); carry: std_logic)

return std_logic_vector is

variable cout: std_logic;

variable cin: std_logic;

variable sum: std_logic_vector(4 downto 0);

begin

cin := carry;

sum := "00000";

loop1: for i in 0 to 3 loop

cout := (a(i) and b(i)) or (a(i) and cin) or (b(i) and cin);

sum(i) := a(i) xor b(i) xor cin;

cin := cout;

end loop loop1;

sum(4) := cout;

return sum;

end add4_func;

procedure add4_proc

27

(a, b: in std_logic_vector(3 downto 0);

carry: in std_logic;

signal sum: out std_logic_vector(3 downto 0);

signal cout: out std_logic) is

variable c: std_logic;

begin

c := carry;

for i in 0 to 3 loop

sum(i) <= a(i) xor b(i) xor c;

c := (a(i) and b(i)) or (a(i) and c) or (b(i) and c);

end loop;

cout <= c;

end add4_proc;

end package body my_package;

Suppose the above package and package body declarations are saved as my_package.vhd, (i.e., as

a VHDL file). Normally, it could be analyzed and placed in any directory, for instance

MY_LIBRARY directory. Then, we can write other VHDL files (or library units) in which we

instantiate items from the newly created library, (i.e., MY_LIBRARY), using the "selected name".

The "selected name" is formed by writing the library name, then the package name, and then the

name of the item (or all if you want to use all items), all separated by dots. For example:

library MY_LIBRARY;

use MY_LIBRARY.my_package.all;

Example 4: Simple 8-bit adder using the above package.

Use ISE WebPack to create a new project. Add to your project the following two VHDL files, and

then synthesize and implement the design.

-------------------------------------------------------------------- First VHDL file: has package declaration and package body.

-- Save it as my_package.vhd

library IEEE;

use IEEE.std_logic_1164.all;

------------------------------------------------------------------package my_package is

function add4_func(a, b : std_logic_vector(3 downto 0); carry : std_logic)

return std_logic_vector;

procedure add4_proc

(a, b : in std_logic_vector(3 downto 0);

carry: in std_logic;

signal sum: out std_logic_vector(3 downto 0);

signal cout: out std_logic);

end package my_package;

------------------------------------------------------------------package body my_package is

function add4_func(a, b : std_logic_vector(3 downto 0); carry: std_logic)

return std_logic_vector is

variable cout: std_logic;

variable cin: std_logic;

variable sum: std_logic_vector(4 downto 0);

28

begin

cin := carry;

sum := "00000";

loop1: for i in 0 to 3 loop

cout := (a(i) and b(i)) or (a(i) and cin) or (b(i) and cin);

sum(i) := a(i) xor b(i) xor cin;

cin := cout;

end loop loop1;

sum(4) := cout;

return sum;

end add4_func;

procedure add4_proc

(a, b : in std_logic_vector(3 downto 0);

carry: in std_logic;

signal sum: out std_logic_vector(3 downto 0);

signal cout: out std_logic) is

variable c: std_logic;

begin

c := carry;

for i in 0 to 3 loop

sum(i) <= a(i) xor b(i) xor c;

c := (a(i) and b(i)) or (a(i) and c) or (b(i) and c);

end loop;

cout <= c;

end add4_proc;

end package body my_package;

-------------------------------------------------------------------------------------------------------------------------------------- Second VHDL file: simple 8-bit adder

-- Uses items from "my_package" created in WORK library directory

-- in your current project directory

-- Save it as bit8_adder.vhd

library IEEE;

use IEEE.std_logic_1164.all;

use WORK.my_package.all;

entity bit8_adder is

port(a, b: in std_logic_vector(7 downto 0);

ci: in std_logic;

y: out std_logic_vector(7 downto 0);

co: out std_logic);

end bit8_adder;

architecture structural of bit8_adder is

signal internal_carry : std_logic;

signal sum1, sum2: std_logic_vector(4 downto 0);

begin

sum1 <= add4_func(a(3 downto 0), b(3 downto 0), ci);

sum2 <= add4_func(a(7 downto 4), b(7 downto 4), sum1(4));

y <= sum2(3 downto 0) & sum1(3 downto 0);

co <= sum2(4);

end;

-------------------------------------------------------------------

29

Lab 3: Four-Bit Binary Counter

1. Objective

The objective of this lab is to design and test a 4-bit binary counter. Aside from learning about the on-board

clock signal and push-buttons as well as about frequency dividers, this lab reinforces the design flow steps

introduced in the previous labs.

2. Description

We design a 4-bit binary counter. Our counter has an output “Q” with four bits. During correct operation,

the counter starts at “0000” and then binary counts up to output “0001”, “0010”, “0011”, and so on until it

outputs “1111”, after which it resets to “0000” and starts again. The first implementation of our counter has

only one input: a clock signal CK. The clock signal is provided by the external (to the FPGA) clock

generator. We use the output Q to drive the first four LEDs on the Atlys board.

The block diagram of the simplest/basic structural implementation of such a binary counter is shown in the

next figure. This implementation is known as a ripple counter.

Figure 1 Block diagram of a 4-bit binary counter

Toggle Flip-Flop

As shown in the figure above, we use four Toggle Flip-Flops (TFF’s). As you remember, the operation of a

TFF is as follows: When the “T” input is logic “1”, the output “Q” will toggle on each clock transition.

When the “T” input is logic “0”, the output “Q” will not change.

To start our design, we first create a new project by launching Xilinx ISE WebPack and following the steps

discussed in lab 2. Call the new project fourbit_counter and select the same location where you created the

previous project.

Create and add to the project a first VHDL file called tff.vhd with the following content:

-- tff.vhd

-- Toggle Flip-Flop with behavioral description

library IEEE;

30

use IEEE.STD_LOGIC_1164.ALL;

entity tff is

Port ( T

: in STD_LOGIC;

CK

: in STD_LOGIC;

Q, QN : out STD_LOGIC);

end tff;

architecture My_behavioral of tff is

signal mem : std_logic := '0';

begin

process (CK, T, mem) -- execute this process only when the clock changes

begin

if T = '0' then null; -- no toggle, so do nothing

elsif (CK'event and CK = '1') then

mem <= not mem; -- rising edge of clock and T = 1, toggle stored value

end if;

end process;

Q <= mem;

QN <= not mem;

end;

Clock Divider

Our counter uses as a clock a signal generated by the on-board clock generator. This clock generator is a

single 100 MHz CMOS oscillator on the Atlys board connected to pin L15 of the Spartan-6 FPGA. Because

the frequency of 100 MHz is too high for the human eye to be able to see how the counter output drives the

LEDs, we must utilize a clock divider to lower the frequency to about 1 Hz.

Create and add to the project a second VHDL file called ck_divider.vhd with the following content:

-- ck_divider.vhd

-- This is a clock divider. It takes as input a signal

-- of 100 MHz and generates an output as signal with a frequency

-- of about 1 Hz.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity ck_divider is

Port ( CK_IN : in STD_LOGIC;

CK_OUT : out STD_LOGIC);

end ck_divider;

architecture Behavioral of ck_divider is

constant TIMECONST : integer := 84;

signal count0, count1, count2, count3 : integer range 0 to 1000;

signal D : std_logic := '0';

begin

process (CK_IN, D)

begin

31

if (CK_IN'event and CK_IN = '1') then

count0 <= count0 + 1;

if count0 = TIMECONST then

count0 <= 0;

count1 <= count1 + 1;

elsif count1 = TIMECONST then

count1 <= 0;

count2 <= count2 + 1;

elsif count2 = TIMECONST then

count2 <= 0;

count3 <= count3 + 1;

elsif count3 = TIMECONST then

count3 <= 0;

D <= not D;

end if;

end if;

CK_OUT <= D;

end process;

end Behavioral;

Read the above code to understand its operation. It takes the 100 MHz external clock as input CK_IN and

generates an output signal CK_OUT of 1 Hz. The output frequency is adjustable according to the following

formula (TIMECONST = 84 in this case in order to get an output frequency of about 1 Hz):

Output Frequency = 100000000 / ( 2 * (TIMECONST ^ 4) )

Note: There are other ways of implementing the TFF or the clock divider. In time, by accumulating more

and more experience, you will develop your own VHDL programming style by adopting different coding

techniques.

4-bit Binary Counter

Finally, let’s create a third VHDL file with the top-level description of our fourbit_counter design described

in Figure 1. Create and add to the project the third VHDL file called fourbit_counter.vhd with the

following content:

-- fourbit_counter.vhd

-- This is a simple 4-bit (Ripple) binary counter made up

-- of four T flip-flops. It also includes a clock divider

-- to bring down the input CK signal from 100 MHz to about 1 Hz.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity fourbit_counter is

Port ( CK : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (3 downto 0));

end fourbit_counter;

architecture Structural of fourbit_counter is

component tff

Port ( T

: in

STD_LOGIC;

32

CK

: in STD_LOGIC;

Q, QN : out STD_LOGIC);

end component;

component ck_divider

Port ( CK_IN : in STD_LOGIC;

CK_OUT : out STD_LOGIC);

end component;

signal all_T, S0, S1, S2, S3, internal_ck : STD_LOGIC;

begin

-- We use signal all_T set to logic '1' to drive

-- input T of all T flip-flops to logic '1'.

all_T <= '1';

CLOCK: ck_divider port map

TFF0: tff port map (all_T,

TFF1: tff port map (all_T,

TFF2: tff port map (all_T,

TFF3: tff port map (all_T,

(CK, internal_ck);

internal_ck, Q(0), S0);

S0, Q(1), S1);

S1, Q(2), S2);

S2, q(3), S3);

end Structural;

Design Implementation

At this time, we have coded the entire design and its components. Before continuing to Design

Implementation, we first take care of two things:

Set the fourbit_counter as the top-level design (we need to do this because currently TFF.vhd is the toplevel because it was added first to the project). To do that, in the Hierarchy window, Right click on

“fourbit_counter – Structural (fourbit_counter.vhd)” and select Set as To-Level.

Pin assignment. As discussed earlier we use the external clock signal connected to pin L15 of the

Spartan-6 FPGA. So, we assign pin L15 to the input “CK” of our design. Also, we use the output “Q”

of our design to drive the first four LEDs of the Atlys board. Now, do the pin assignment as learned in

lab 2. After this step, your UCF file should have the following content:

# PlanAhead Generated physical constraints

NET "Q[0]" LOC = U18;

NET "Q[1]" LOC = M14;

NET "Q[2]" LOC = N14;

NET "Q[3]" LOC = L14;

NET "CK" LOC = L15;

We are now ready to implement the design: in the Processes tab double-click Implement Design (or rightclick on Implement Design and select Run).

Generate the Programming File and Program the FPGA

Double-click on Generate Programming File in the Process tab. Then, program the FPGA using the Adept

software as learned in lab 2. Verify that our counter works correctly.

3. Lab assignment

33

Lab preparation

A major problem with the counter implemented in this lab is that the individual flip-flops do not all change

state at the same time. Rather, each flip-flop is used to trigger the next one in the series. Thus, in switching

from all 1s (count = 15) to all 0s (count wraps back to 0), we don’t see a smooth transition. Instead, output

Q(0) falls first, changing the apparent count to 14. This triggers output Q(1) to fall, changing the apparent

count to 12. This in turn triggers output Q(2), which leaves a count of 8 while triggering output Q(3) to fall.

This last action finally leaves us with the correct output count of zero. We say that the change of state

“ripples” through the counter from one flip-flop to the next. Therefore, this circuit is known as a “ripple

counter”.

This causes no problem if the output is only to be read by human eyes; the ripple effect is too fast for us to

see it. However, if the count is to be used as a selector by other digital circuits (such as a multiplexer or

demultiplexer), the ripple effect can easily allow signals to get mixed together in an undesirable fashion. To

prevent this, we need to devise a method of causing all of the flip-flops to change state at the same moment.

That would be known as a “synchronous counter” because the flip-flops would be synchronized to operate

in unison.

In this lab assignment, you must design a synchronous counter version of our fourbit_counter to arrive to a

new block diagram, where all flip-flops are driven by the same clock signal. You should design this counter

using the Karnaugh Maps method and utilize JK flip-flops instead of T flip-flops. In addition, the top-level

design of the fourbit_counter should have an additional input, “RESET”, which when set to logic “1” forces

the counter to the initial state “0000”. The RESET input should be controlled by one of the pushbuttons of

the Atlys board.

Optional:

Remove entirely the clock divider from the design. Instead of the clock signal of 100 MHz utilize a

signal from one of the pushbuttons of the Atlys board. In this case, the counter will advance each time

the pushbutton is pressed.

Modify the counter such that it can be told to count up or down.

Lab report and demo

You must turn-in a lab report, which should contain the following:

Lab title

Your name

Introduction section – a brief description of the problem you solve in this lab assignment, outlining the

goal and design requirements.

Solution – details of your Karnaugh Maps method. Include all block diagrams and K-maps you need to

illustrate each step. This section must be hand-written.

VHDL code – of your entire design. Use smaller font to save space.

Conclusion – describe your results and any issues you may have faced during this assignment and how

you solved them.

For full credit, you must demo the correct operation of your counter to the TA during the next lab.

34

Lab 3: Supplemental Material - Testbenches

The objective of this supplemental material is to reinforce the concept of testbenches in VHDL.

1. Introduction

On alternative way to verify the correctness of a VHDL description of a design is to use

testbenches.

A testbench is an enclosing VHDL model. Its name comes from the analogy with a real hardware

testbench, on which a Device Under Test (DUT) is stimulated with signal generators and observed

with signal probes. A VHDL testbench consists of an architecture body containing an instance of

the component to be tested and processes that generate sequences of values on signals connected to

the component instance. The architecture body may also contain processes that test the component

instance produces the expected values on its output signals.

During this supplemental lab you will write the VHDL model for a registered ALU using a

package, and test it using a testbench. Your ALU is capable of performing four operations on two

operands as shown in Fig.1. The flag output is high (logic '1') whenever there is either an

underflow or overflow on the C bus.

a(3:0)

b(3:0)

ALU

1

func(1:0)

4

clk

REGISTER

flag

reset

c(3:0)

Figure 1 Simple ALU

2. Writing the package

As you already learned, a VHDL package is an important way of grouping a collection of related

declarations that serve a common purpose. Usually, a package is a set of subprograms that provide

operations on a particular type of data, or they might be just the set of declarations needed to

model a design.

The important thing is that they can be collected together into a separate design unit that can be

worked on independently and reused in different parts of a model or models.

The following VHDL code describes all the operations needed to implement the four basic

operations of your simple ALU. Type it using any text editor (or using the VHDL editor of ISE

WebPack) and save it as alupack.vhd.

35

--------------------------------------------library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

---------------------------------------------- package declarations for procedures and constants

package addorsub is

-- set the default bus size

constant bussize : integer := 4;

-- set up a type for a bus of size bussize

subtype stdbus is signed (3 downto 0);

subtype lrgbus is signed (4 downto 0);

-- set the integer range for a bus of size bussize + 1

subtype medint is integer range -32 to 31;

-- extend performs a one bit signed or signed bit extension based

-- on the value of signex. signex=1 does a signed extension.

procedure extend (signal inbus : in stdbus; variable outbus : out

lrgbus; signex : in std_logic);

-- usadd performs signed or signed addition of two busses of size

-- bussize. the result is a signed or signed bus of size bussize

-- depending on signex (signex = 1 produces a signed result). reportf

-- indicates if there is an underflow or overflow.

procedure usadd (signal abus, bbus : in signed(bussize-1 downto 0);

signal result : out signed(bussize-1 downto 0);

signex : in std_logic;

signal reportf : out std_logic);

-- ussub performs signed or signed subtraction (abus - bbus)

-- of two busses of size bussize (signex=1 causes signed subtraction).

-- reportf =1 if there is an underflow or overflow.

procedure ussub (signal abus, bbus : in signed(bussize-1 downto 0);

signal result : out signed(bussize-1 downto 0);

signex : in std_logic;

signal reportf : out std_logic);

end addorsub;

---------------------------------------------- package body contains the procedure bodies.

package body addorsub is

procedure extend (signal inbus : in stdbus; variable outbus : out

lrgbus; signex : in std_logic) is

begin

outbus := (signex and inbus (bussize-1)) & inbus(bussize-1 downto 0);

end;

procedure usadd (signal abus, bbus : in signed(bussize-1 downto 0);

signal result : out signed(bussize-1 downto 0);

signex : in std_logic;

signal reportf : out std_logic) is

variable tempr : medint;

variable tempa : signed(bussize downto 0);

variable tempb : signed(bussize downto 0);

begin

-- sign/unsign extend abus and bbus to a bus of size bussize + 1;

36

extend(abus, tempa, signex);

extend(bbus, tempb, signex);

--perform signed addition

tempr := to_integer(tempa)+ to_integer(tempb);

-- check for overflows dependent on type of addition

if (signex = ‘0’ and tempr > 15) then

--overflow of signed addition

reportf <= ‘1’;

elsif (signex = ‘1’ and (tempr > 7 or tempr < -8)) then

-- overflow or underflow of signed addition

reportf <= ‘1’;

else

reportf <= ‘0’;

end if;

result <= to_signed(tempr, bussize);

end usadd;

procedure ussub (signal abus, bbus : in signed(bussize-1 downto 0);

signal result : out signed(bussize-1 downto 0);

signex : in std_logic;

signal reportf : out std_logic) is

variable tempr : medint;

variable tempa : signed(bussize downto 0);

variable tempb : signed(bussize downto 0);

begin

-- sign/unsign extend abus and bbus to a bus of size bussize+1;

extend(abus, tempa, signex);

extend(bbus, tempb, signex);

-- perform signed addition

tempr := to_integer(tempa)- to_integer(tempb);

-- check for overflows dependent on type of addition

if (signex = ‘0’ and tempr < 0) then

reportf <= ‘1’;

elsif (signex = ‘1’ and (tempr > 7 or tempr < -8)) then

-- overflow or underflow of signed addition

reportf <= ‘1’;

else

reportf <= ‘0’;

end if;

result <= to_signed(tempr, bussize);

end ussub;

end addorsub; -- end of package body

---------------------------------------------

3. Writing the VHDL description of the ALU

The following VHDL code describes the ALU, which uses the functions declared and

implemented in the package alupack. The ALU should have a register to latch the output. Type it

using any text editor and save it as alu.vhd.

--------------------------------------------library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use WORK.addorsub.all;

--------------------------------------------entity alu is

port (a, b : in stdbus;

37

func : in std_logic_vector(1 downto 0);

clk, reset : in std_logic;

flag : out std_logic;

c : out stdbus);

end alu;

--------------------------------------------architecture rtl of alu is

signal intflag : std_logic;

signal intbus : stdbus;

begin

regp : process (clk, reset)

begin

if (reset = ‘1’) then

flag <= ‘0’;

c <= “0000”;

elsif (clk’event and clk = ‘0’) then

flag <= intflag;

c <= intbus;

end if;

end process regp;

alup : process(a, b, func)

begin

if func(1) = ‘0’ then

usadd(a, b, intbus, func(0), intflag);

else

ussub(a, b, intbus, func(0), intflag);

end if;

end process alup;

end rtl;

---------------------------------------------

4. Writing the testbench

The following VHDL code represents the testbench. It generates inputs for and monitors the

outputs from the ALU. The testbench compares the actual outputs with expected outputs and prints

out if a test is successful or not. Note that you do not need a stimulus file when you work with

testbenches; the design is stimulated with stimulus generated inside the testbench.

Type the following VHDL code and save it as testbench.vhd.

--------------------------------------------library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use WORK.addorsub.all;

--------------------------------------------entity testbench is

end testbench;

--------------------------------------------architecture test of testbench is

type table_type1 is array (0 to 5) of signed (3 downto 0);

type table_type2 is array (0 to 3) of std_logic_vector (1 downto 0);

constant inputa : signed := “0000”;

constant inputb : signed := “0000”;

38

constant outc : table_type1 := (“0001”, “0011”, “0101”, “0111”, “1001”,“1011”);

constant outgen : table_type2 := (“00”, “01”, “10”, “11”);

signal cbus : signed (3 downto 0);

signal flag : std_logic;

signal abus : signed (3 downto 0) := “0000”;

signal bbus : signed (3 downto 0) := “0000”;

signal clk : std_logic;

signal reset : std_logic;

signal sel : std_logic_vector (1 downto 0) := “00”;

component alu

port (a, b : in stdbus;

func : in std_logic_vector(1 downto 0);

clk, reset : in std_logic;

flag : out std_logic;

c : out stdbus);

end component;

for alu_inst : alu use entity work.alu(rtl);

begin

alu_inst : alu port map (abus, bbus, sel, clk, reset, flag, cbus);

clkp : process

begin

clk <= ‘1’, ‘0’ after 50 ns;

wait for 100 ns;

end process clkp;

rset : process

begin

reset <= ‘1’, ‘0’ after 100 ns;

wait for 1 ms;

end process rset;

testp : process

begin

wait for 100 ns; -- this is needed for reset to finish

for j in 0 to 1 loop -- test for unsigned & signed add

sel <= outgen(j);

for i in 0 to 5 loop

abus <= inputa + TO_SIGNED(i, 4);

bbus <= inputb + TO_SIGNED(i+1, 4);

wait for 51 ns;

assert (cbus = outc(i))

report “Result is not correct”

severity warning;

wait for 49 ns;

end loop;

end loop;

for j in 2 to 3 loop -- test for unsigned & signed sub

sel <= outgen(j);

for i in 0 to 5 loop

abus <= inputa + TO_SIGNED(i, 4);

bbus <= inputb + TO_SIGNED(i+1, 4);

wait for 51 ns;

assert (cbus = "1111”)

report “Result is not correct”

severity warning;

wait for 49 ns;

39

end loop;

end loop;

assert false

report “Test Complete”

severity error;

end process testp;

end test;

---------------------------------------------

Read thoroughly the above files to understand the functionality of the testbench, then:

Use Aldec HDL simulator to simulate alu.vhd together with alupack.vhd. Create your own

input signals (as in lab#1) to stimulate the four basic operations performed by the ALU and

verify its correctness.

Simulate testbench.vhd (together with alu.vhd and alupack.vhd) to verify the ALU. Notice that

using testbeches saves your time.

5. Lab assignment

You are required to modify the ALU design such that it can be implemented with ISE WebPack

and verified on the Atlys board. You must add a clock divider to provide a clock frequency of 1 Hz

to the ALU unit. The clock divider uses as input the 100 MHz signal of the Atlys board.

Use output c(3:0) to drive LEDs. The LEDs must display either a number between 0-15 for

unsigned operations, or a number between 0-7 for the signed operations. The output "flag" should

drive the left most LED. As inputs a(3:0) and b(3:0) use all eight slide-switche. As func(1:0) use

the two push-buttons. Synthesize and implement this modified ALU and download its bitstream

file to the board to configure the FPGA. Verify the correct operation.

40

Lab 4: Finite State Machines

1. Objective

The objective of this lab is to study several different ways of specifying and implementing finite state

machines (FSMs). We also discuss finite state machines with datapath (FSMD).

2. Introduction

There are two basic types of sequential circuits: Mealy and Moore. Because these circuits transit among a

finite number of internal states, they are referred to as finite state machines (FSMs). In a Mealy circuit, the

outputs depend on both the present inputs and state. In a more circuit, the outputs depend only on the

present state. The most common way of schematically representing a Mealy sequential circuit is shown in

Fig.1.