VLSI Design Lab Manual: Experiments & VHDL Code

advertisement

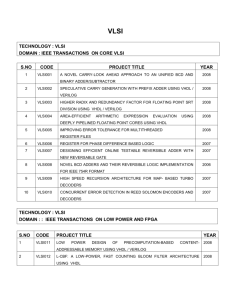

LABORATORY MANUAL VLSI DESIGN LAB EE-330-F (VIth Semester) Prepared By: Vikrant Verma B. Tech. (ECE), M. Tech. (ECE) Department of Electrical & Electronics Engineering BRCM College of Engineering & Technology Bahal-127028 (Bhiwani) Modified on 14 November 2014 VLSI Design Lab Manual Page 1 SYLLABUS VLSI Design Lab (EE-330-F) F - Scheme (w.e.f. August 2009) L T P - - 2 Sessional : Practical : Total : Duration of Exam : 25 Marks 25 Marks 50 Marks 3 hrs. 1) Design of Half-Adder, Full Adder, Half Subtractor, Full Subtractor 2) Design a parity generator 3) Design a 4 Bit comparator 4) Design a RS & JK Flip flop 5) Design a 4: 1 Multiplexer 6) Design a 4 Bit Up / Down Counter with Loadable Count 7) Design a 3:8 decoder 8) Design a 8 bit shift register 9) Design a arithmetic unit 10) Implement ADC & DAC interface with FPGA 11) Implement a serial communication interface with FPGA 12) Implement a Telephone keypad interface with FPGA 13) Implement a VGA interface with FPGA 14) Implement a PS2 keypad interface with FPGA 15) Implement a 4 digit seven segment display Notes : At least 10 experiments are to performed by students in the semester. At least 7 experiments should be performed from the above list; remaining three experiments may either be performed from the above list or designed and set by the concerned institution as per the scope of the syllabus. VLSI Design Lab Manual Page 2 Index S.No. Name of Experiment 1 Page No. Date Signature Write the VHDL Code & Simulate it for the following gates. Two I/P AND Gates. Two I/P OR Gates. Two I/P NAND Gates Two I/P NOR Gates. Two I/P Ex-OR Gates. NOT Gates. 2 Write behavior model of 1- bit Comparator. 3 Write a program for behavior model of 4- bit Comparator. 4 Write the VHDL code & simulate it for 4:1 Multiplexer & 4:1 Demultiplexer. 5 Write a program for behavior model of BCD-toSeven Segment Decoder. 6 Write a VHDL program for behavior model of Parallel-Input-Parallel-Output. 7 Write VHDL programs for the following circuits, check the wave forms and hardware generated. a) Half Adder. b) Full Adder. 8 Write VHDL programs for ALU. 9 Write a VHDL program for behavior model of D Flip - Flop. 10 Write a VHDL program for behavior model of 3Bit UP Counter. VLSI Design Lab Manual Page 3 EXPERIMENT – 1 Aim: Write the VHDL Code & Simulate it for the following gates. Two I/P AND Gates. Two I/P OR Gates. Two I/P NAND Gates Two I/P NOR Gates. Two I/P Ex-OR Gates. NOT Gates. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: VLSI Design Lab Manual Page 4 Program: i) Behavior Model if two I/P AND Gates. Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity and_2 is Port (a, b: in bit; z: out bit); End and_2; Architecture and_2_beh of and_2 is Begin process (a, b) Begin If (a=’0’ and b=’0’) then Z<=’0’; ElsIf (a=’0’ and b=’1’) then Z<=’0’; ElsIf (a=’1’ and b=’0’) then Z<=’0’; ElsIf (a=’1’ and b=’1’) then Z<=’1’; End if; End process; End and_2_beh; ii) Behavior Model if two I/P OR Gates Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity OR_2 is Port (a, b: in bit; z: out bit); End OR_2; VLSI Design Lab Manual Page 5 Architecture OR_2_beh of OR_2 is Begin process (a,b) Begin If (a=’0’ and b=’0’) then Z<=’0’; Elsif (a=’0’ and b=’1’) then Z<=’1’; Elsif (a=’1’ and b=’0’) then Z<=’1’; Elsif (a=’1’ and b=’1’) then Z<=’1’; End if; End process; End OR_2_beh; iii) Behavior Model if two I/P NAND Gates Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity NAND_2 is Port (a, b: in bit; z: out bit); End NAND_2; Architecture NAND_2_beh of NAND_2 is Begin process (a, b) Begin If (a=’0’ and b=’0’) then Z<=’1’; Elsif (a=’0’ and b=’1’) then Z<=’1’; Elsif (a=’1’ and b=’0’) then Z<=’1’; Elsif (a=’1’ and b=’1’) then VLSI Design Lab Manual Page 6 Z<=’0’; End if; End process; End NAND_2_beh; iv) Behavior Model if two I/P NOR Gates Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity NOR_2 is Port (a, b: in bit; z: out bit); End NOR_2; Architecture NOR_2_beh of NOR_2 is Begin process (a, b) Begin If (a=’0’ and b=’0’) then Z<=’1’; Elsif (a=’0’ and b=’1’) then Z<=’0’; Elsif (a=’1’ and b=’0’) then Z<=’0’; Elsif (a=’1’ and b=’1’) then Z<=’0’; End if; End process; End NOR_2_beh; v) Behavior Model if two I/P EX-OR Gates Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; VLSI Design Lab Manual Page 7 Entity EXOR_2 is Port (a, b: in bit; z: out bit); End EX-OR_2; Architecture EXOR_2_beh of EXOR_2 is Begin Process (a, b) Begin If (a=’0’ and b=’0’) then Z<=’0’; Elsif (a=’0’ and b=’1’) then Z<=’1’; Elsif (a=’1’ and b=’0’) then Z<=’1’; Elsif (a=’1’ and b=’1’) then Z<=’0’; End if; End process; End EXOR_2_beh; vi) Behavior Model if two I/P NOT Gates Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity NOT_2 is Port (a: in bit; z: out bit); End NOT_2; Architecture EXOR_2_beh of EXOR_2 is Begin Process (a) Begin If (a=’0’) then Z<=’1’; VLSI Design Lab Manual Page 8 Elsif (a=’1’) then Z<=’0’; End if; End process; End NOT_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of AND, OR, NAND, NOR, EX-OR and NOT gates are simulated & found correct. Typical viva-voce questions for reference: Q1: The output will be a LOW for any case when one or more inputs are zero in a(n): A. OR gate B. NOT gate C. AND gate D. NAND gate Ans: AND gate Q.2: If a signal passing through a gate is inhibited by sending a low into one of the inputs, and the output is HIGH, the gate is a(n): A. OR gate B. NOT gate C. AND gate D. NAND gate Ans: NAND gate Q.3: A single transistor can be used to build which of the following digital logic gates? A. OR gate B. NOT gate C. AND gate D. NAND gate Ans: NOT gate VLSI Design Lab Manual Page 9 EXPERIMENT – 2 Aim: Write behavior model of 1- bit Comparator. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: Program: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity CMP_2 is Port (a, b: in bit; ALB, AGB, AEB: out bit); End CMP_2; Architecture CMP_2_beh of CMP_2 is Begin Process (a, b) VLSI Design Lab Manual Page 10 Begin If (a=’0’ and b=’0’) then ALB<=’0’; AGB<=’0’; AFB<=’1’; Elsif (a=’0’ and b=’1’) then ALB<=’1’; AGB<=’0’; AFB<=’0’; Elsif (a=’1’ and b=’0’) then ALB<=’0’; AGB<=’1’; AFB<=’0’; Elsif (a=’1’ and b=’1’) then ALB<=’0’; AGB<=’0’; AFB<=’1’; End if; End process; End CMP_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of 1- bit Comparator is simulated & synthesized. Typical viva-voce questions for reference: Q.1: How many 3-line-to-8-line decoders are required for a 1-of-32 decoder? Ans: Four. Q.2: What is an Identity Comparator ? Ans: An Identity Comparator is a digital comparator that has only one output terminal for when A = B either “HIGH” A = B = 1 or “LOW” A = B = 0 Q.3: What is Magnitude Comparator? Ans: A Magnitude Comparator is a type of digital comparator that has three output VLSI Design Lab Manual Page 11 terminals, one each for equality, A = B greater than, A > B and less than A < B. Q.4: What is the purpose of a Digital Comparator? Ans: The purpose of a Digital Comparator is to compare a set of variables or unknown numbers, for example A (A1, A2, A3, …. An, etc) against that of a constant or unknown value such as B (B1, B2, B3, …. Bn, etc) and produce an output condition or flag depending upon the result of the comparison. For example, a magnitude comparator of two 1-bits, (A and B) inputs would produce the following three output conditions when compared to each other. VLSI Design Lab Manual Page 12 EXPERIMENT – 3 Aim: Write a program for behavior model of 4- bit Comparator. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: Program: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity COM_2 is Port (a, b: in bit_vector (3 down to 0); z: out bit_vector (2 down to 0)); End COM_2; Architecture COM_2_beh of COM_2 is Begin Process (a, b) Begin If (a=b) then Z<=’100’; Elsif (a<b) then Z<=’010’; Elsif (a>b) then Z<=’001’; End if; End process; VLSI Design Lab Manual Page 13 End COM_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: The VHDL code of 4- bit Comparator is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is comparator? Ans: A digital comparator or magnitude comparator is a hardware electronic device that takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number. Q.2: What are uses of comparator? Ans: Comparators are used in central processing unit s (CPUs) and microcontrollers (MCUs). Examples of digital comparator include the CMOS 4063 and 4585 and the TTL 7485 and 74682-'89. Q.3: What is the voltage comparator? Ans: The analog equivalent of digital comparator is the voltage comparator. Many microcontrollers have analog comparators on some of their inputs that can be read or trigger an interrupt. Q.4: What is the no. of outputs in 4- bit comparator? Ans: Three output. VLSI Design Lab Manual Page 14 EXPERIMENT – 4 Aim: Write the VHDL code & simulate it for 4:1 Multiplexer & 4:1 Demultiplexer. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: VLSI Design Lab Manual Page 15 Program: 4-to-1 Multiplexer’s Behavior Model: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity MUX_2 is Port (i0, i1, i2, i3, s0, s1: in bit; z: out bit); End MUX_2; Architecture MUX_2_beh of MUX_2 is Begin Process (so, s1) Begin If (s1=’0’ and s0=’0’) then Z<=’i0’; Elsif (s1=’0’ and s0=’1’) then Z<=’i1’; Elsif (s1=’1’ and s0=’0’) then Z<=’i2’; Elsif (s1=’1’ and s0=’1’) then Z<=’i3’; End if; End process; End MUX_2_beh; 1-to-4 Demultiplexer: VLSI Design Lab Manual Page 16 1-to-4 Demultiplexer’s Behavior Model: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity DEMUX_2 is Port (a, s0, s1: in bit; z: out bit_vector (3 down to 0)); End DEMUX_2; Architecture DEMUX_2_beh of DEMUX_2 is Begin Process (so, s1) Begin If (s1=’0’ and s0=’0’) then Z (0) <=a; Z (1) <=’0’; Z (2) <=’0’; Z (3) <=’0’; Elsif (s1=’0’ and s0=’1’) then Z (0) <=’0’; VLSI Design Lab Manual Page 17 Z (1) <=a; Z (2) <=’0’; Z (3) <=’0’; Elsif (s1=’1’ and s0=’0’) then Z (0) <=’0’; Z (1) <=’0’; Z (2) <=a; Z (3) <=’0’; Elsif (s1=’1’ and s0=’1’) then Z (0) <=’0’; Z (1) <=’0’; Z (2) <=’0’; Z (3) <=a; End if; End process; End DEMUX_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: a) All the VHDL codes of 4-to-1 Multiplexer is simulated & synthesized. b) All the VHDL codes of 1-to-4 Demultiplexer is simulated & synthesized. Typical viva-voce questions for reference: Q.1 A basic multiplexer principle can be demonstrated through the use of a? Ans. Rotary Switch. Q.2 What is the function of an enable input on a multiplexer chip? Ans. To active the entire chip. Q.3 Will multiplexing create additional harmonics in the system? Ans. No, the total harmonic content while using multiplex mode is no worse than using normal SCR dimmer firing modes. Q.4 Can you accidentally switch a dimmer to multiplex mode? Ans. To minimize the chances of this occurring, a number of steps are required to configure a VLSI Design Lab Manual Page 18 dimmer for multiplexing at the sensor dimmer rack. Each action requires operator confirmation and dimmer status is clearly displayed at all times during setup. VLSI Design Lab Manual Page 19 EXPERIMENT – 5 Aim: Write a program for behavior model of BCD-to-Seven Segment Decoder. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: BCD Input’s Output’s ABCD a b c d e f g 0 0 0 0 1 1 1 1 1 1 0 0 0 0 1 0 1 1 0 0 0 0 0 0 1 0 1 1 0 1 1 0 1 0 0 1 1 1 1 1 1 0 0 1 0 1 0 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 VLSI Design Lab Manual Page 20 Program: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity BCD_2 is Port (b: in bit_Vector (3 down to 0); z: out bit_vector (6 down to 0)); End BCD_2; Architecture BCD_2_beh of BCD_2 is Begin Process (b) Begin Case B is When “0000”=> S<=”1111110”; When “0001”=> S<=”0110000”; When “0010’=> S <=”1101101”; When “0011”=> S<=”1111001”; When “0110”=> S<=”1011111”; When”0111”=> S<=”1110000”; When”1000”=> S<=”1111111”; When”1001”=> S<=”1110011”; When other => S<=”000000”; End case; End process; VLSI Design Lab Manual Page 21 End BCD_Beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of BCD-to-Seven Segment is simulated & synthesized. Typical viva-voce questions for reference: Q.1 What is the full the full form of BCD? Ans: Binary Coded Decimal. Q.2 What is the function of decoder? Ans: In digital electronics, a decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. E.g. n-to-2n, binary-coded decimal decoders. Q.3 What is the full form of LCD? Ans: Liquid Crystal Display. Q.4 What is 7-Segment? Ans: A standard 7-segment LED display generally has 8 input connections, one for each LED segment and one that acts as a common terminal or connection for all the internal display segments. Some single displays have also have an additional input pin to display a decimal point in their lower right or left hand corner. VLSI Design Lab Manual Page 22 EXPERIMENT – 6 Aim: Write a VHDL program for behavior model of Parallel-Input-ParallelOutput. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: Parallel Input's D(0) D(1) D(2) D(3) PR D CLK Q FF0 CR D Q FF1 D Q FF2 D Q FF3 Parallel Output's Program: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity PIPO_2 is Port (Pr, Cr, Clk: in bit; D: is bit_vector (2 down to 0); Q: out bit_vector (2 down to 0)); End PIPO_2; Architecture PIPO_2_beh of PIPO_2 is Begin Process (Pr, Cr, Clk, D) Begin If (Pr=’0’ and Cr=’1’) then Q<=’111’; VLSI Design Lab Manual Page 23 Elsif (Pr=’1’ and Cr=’0’) then Q<=’000’; Elsif (Pr=’0’ and Cr=’1’) then Q<=’0’; Elsif (Pr=’1’ and Cr=’1’) then Q<=’111’; Elsif (Pr=’1’ and Cr=’1’and Clk=’0’ and Clk’s event) then Q<=’D; End if; End process; End PIPO_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of PIPO is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is the purpose of parallel input and parallel output? Ans: The purpose of the parallel-in/ parallel-out shift register is to take in parallel data, shift it, then output. Q.2: Is try-state buffer is necessary in PIPO? Ans: No need. Q.3: Which is fast between PIPO and SISO? Ans: Parallel input parallel output. Q.4: How many stages in PIPO system? Ans: Four stages. VLSI Design Lab Manual Page 24 EXPERIMENT – 7 Aim: Write VHDL programs for the following circuits, check the wave forms and hardware generated. c) d) Half Adder. Full Adder. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: VLSI Design Lab Manual Page 25 Program: a) Behavior Model of Half-Adder: Library IEEE; Use ieee.std_logic_1164_all; Use ieee.std_logic_arith_all; Entity HA_2 is Port (a, b: in bit; s, c: out bit); End HA_2; Architecture HA_2_beh of HA_2 is Begin Process (a, b) Begin If (a=’0’ and b=’0’) then S<=’0’; C<=’0’; Elsif (a=’0’ and b=’1’) then S<=’1’; C<=’0’; Elsif (a=’1’ and b=’0’) then S<=’1’; C<=’0’; Elsif (a=’1’ and b=’1’) then S<=’0’; C<=’1’; End if; End process; End HA_2_beh; VLSI Design Lab Manual Page 26 Inputs A B 0 0 1 0 0 1 1 1 0 0 1 0 0 1 1 1 Outputs Cin Cout S 0 0 0 0 0 1 0 0 1 0 1 0 1 0 1 1 1 0 1 1 0 1 1 1 b) Behavior Model of FULL Adder: Library IEEE; Use ieee.std_logic_1164_all; Use ieee.std_logic_arith_all; Entity FA_2 is Port (a, b, cin: in bit; s, c: out bit); End FA_2; Architecture FA_2_beh of FA_2 is Begin Process (a, b,cin) VLSI Design Lab Manual Page 27 Begin S<=a XOR B XOR Cin; C<= (a and b) OR (a and cin) OR (b and cin); End process; End FA_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: (a) All the VHDL codes of Half Adder is simulated & synthesized. (b) All the VHDL codes of Full Adder is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is Half adder? Ans: Half adder sums the two input and gives output with carry. Q.2: What is full adder? Ans: Full adder sums the three input gives output with carry. Q.3: Which gates are used in design of half adder? Ans: XOR gate and AND gate. Q.4: Using which gates we design the full adder? Ans: AND gate, OR gate and XOR gate. VLSI Design Lab Manual Page 28 EXPERIMENT – 8 Aim: Write VHDL programs for ALU. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: Program: Behavior Model of ALU: Library IEEE; Use ieee.std_logic_1164_all; Use ieee.std_logic_arith_all; Entity ALU_2 is Port (p, q: in bit_vector (3 down to 0); s: in bit_vector (2 down to 0); f: in bit_vector (3 down to 0)); End ALU_2; Architecture ALU_2_beh of ALU_2 is Function of “+” Function add (a, b: bit_vector (2 down to 0) Return bit_vector is Variable cout: bit; Variable cin: bit; VLSI Design Lab Manual Page 29 Variable sum: bit_vector (2 down to 0); Begin For i: in 0 to 2 loop Sum (i): a (i) XOR b (i) XOR Cin; Cout: = (a (i) and b (i)) OR (b (i) and Cin) OR (Cin And a (i)); Cin: = Cout End loop; Return sum; End “+” --function of subtraction of 2 bit array Function “-“(a, b: bit_vector (3 down to 0 Return bit_vector is Variable cout: bit; Variable Cin: bit=’0’; Variable diff (i): bit_vector (3 down to 0); Begin For I in 0 to 3 loop Cout: = ((not a (i) and b (i)) or ((b (i) and cin) or ((not a (i) and cin)) ; Diff (i):= a (i) xor b (i) xor cin; Cin: = cout; End loop; Return diff (i); End “-“; Begin Process (p, q, and s) Begin Case s is When “000”=> F<= “0000”; When “001” => F =q-p; When “010”=> VLSI Design Lab Manual Page 30 F =p-q; When “001”=> F =p+q; When “100”=> F =p and q; When “101”=> F<= p xor q; When “110”=> F<=p or q: When “111” => F<= “1111”; End case; End process; End ALU_Beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of ALU is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is the full form of ALU? Ans: Arithmetic Logic Unit. Q.2: What is the function of ALU? Ans: Arithmetic and logic unit controls the arithmetic and logic operations. Q.3: What are the examples of ALU operation? Ans: Addition, Subtraction, Multiplication, Division etc. Q.4: How many select lines are used in ALU? Ans: Two select lines are used. VLSI Design Lab Manual Page 31 EXPERIMENT – 9 Aim: Write a VHDL program for behavior model of D Flip - Flop. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: Program: Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; VLSI Design Lab Manual Page 32 Entity DIFF_2 is Port (Pr, Cr, Clk: in bit; D: is bit_vector (2 down to 0); Q: out bit_vector (2 down to 0)); End DIFF_2; Architecture DIFF_2_beh of DIFF_2 is Begin Process (Pr, Cr, Clk, D) Begin If (Pr=’0’ and Cr=’1’) then Q<=’1’; Elsif (Pr=’1’ and Cr=’0’) then Q<=’0’; Elsif (Pr=’1’ and Cr=’1’and Clk=’0’ and Clk’s event) then Q<=D; End if; End process; End DIFF_2_beh; Precautions: Make sure that there is no syntax and semantic error. Result: All the VHDL codes of D-Flip Flop is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is a flip flop? Ans: In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bi-stable multi-vibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. Q.2: What are the types of flip flop? Ans: R-S flip flop, j-k, D and T flip flop. VLSI Design Lab Manual Page 33 Q.3: What is D flip flop? Ans: D flip-flops are used to eliminate the indeterminate state that occurs in RS Flip-flop. D flip-flop ensures that R and S are never equal to one at the same time. The D flip-flop has two inputs including the Clock pulse. D and CP are the two inputs of the D flip-flop. Q.4: What is R-S flip flop? Ans: This type of flip-flop is very similar to the one we discussed in the basic circuit. But however a certain difference exists. In this flip-flop circuit an additional control input is applied. This additional control input determines the when the state of the circuit is to be changed. This additional input is nothing but the clock pulse. The RS flip-flop consists of basic flip-flop circuit along with two additional NAND gates and a clock pulse generator. The clock pulse acts as an enable signal for the two inputs. The output of the gates 3 and 4 remains at logic “1” until the clock pulse input is at 0.This is nothing but the quiescent condition of the flip-flop. Now let us see how it works. VLSI Design Lab Manual Page 34 EXPERIMENT – 10 Aim: Write a VHDL program for behavior model of 3- Bit UP Counter. Apparatus used: XILINX 8.1 Software installed in a PC. Theory: T PR T Q T FF0 CLK FF1 Q (0) LSB Program: Q Q(1) Parallel Output’s T Q FF2 Q(2) MSB CR Library IEEE; Use IEEE.std_logic_1164_all; Use IEEE.std_logic_arith_all; Entity COUNTER_2 is Port (Pr, Cr, Clk, t: in bit; Q: out bit_vector (0 to 2)); End DIFF_2; Architecture COUNTER _2_beh of COUNTER _2 is Function of “+” Function add (a, b: bit_vector (0 down to 2)) Return bit_vector is VLSI Design Lab Manual Page 35 Variable cout: bit; Variable cin: bit: = ‘0’; Variable sum: bit_vector (0 to 2):= “000”; Begin For i: in 0 to 2 loop Cout: = (a (i) and b (i)) OR (b (i) and Cin) OR (Cin And a (i)); Sum (i): a (i) XOR b (i) XOR Cin; Cin: = Cout End loop; Return sum; End “+”; Begin Process (Clk, Pr, Cr) Begin If (Pr=’0’ and Cr=’1’) then Q<= ‘111’; Elsif (Pr=’1’ and Cr=’0’) then Q<= ‘000’; Elsif (Pr=’1’ and Cr=’1’and Clk=’0’ and Clk’s event) then Q<=Q+ “000”; End if; End process; End COUNTER _2_beh Precautions: Make sure that there is no syntax and semantic error. Result: The VHDL code of UP-Counter is simulated & synthesized. Typical viva-voce questions for reference: Q.1: What is counter? VLSI Design Lab Manual Page 36 Ans: Counter is a sequential circuit. A digital circuit which is used for counting pulses is known counter. Counter is the widest application of flip-flops. Q.2: How many types of counter are there? Ans: Two types: up counter and down counter. Q.3: How many stages are used in 3-bit counter? Ans: Three (q0,q1,q2). Q.4: Counter is the register type or capacitor type? Ans: Counter is the register type sequential circuit. VLSI Design Lab Manual Page 37

0

0

advertisement

Related documents

Download

advertisement

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

Sign in Available only to authorized users