Casio AL-1000 Calculator

advertisement

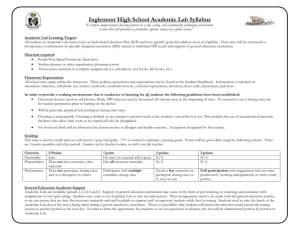

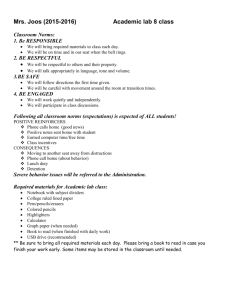

Casio AL-1000 Calculator Contents Section 1 Notes & Signals 2 Block Diagram 3 Modules - Gates 4 Modules - Flip Flops 5 State Graph 6 State Descriptions Timing Diagram 7 8 Timing Casio AL-1000 Calculator Section: Title & Contents Page: 1 Rendition: 2015 Mar 13 Page Title & Contents (this page) 9 Keyboard 10 Control - T State 11 Control - Function Latch & Decoding 12 Control - State Sequencing 13 Control - State Decoding 14 Control - Miscellaneous Digit Counter 15 16 Decimal Point Counter 17 Register Selection 18 A & B Latches 19 Arithmetic 20 Memory Address Drivers 21 Memory Inhibit & Sense Display Power Supply Connectors 1-5 Connectors 6-10 22 23 24 25 26 This schematic has been derived through reverse engineering. This is not the manufacturer’s schematic, nor based on the manufacturer’s schematic. Notes ♦ Gate symbols and signal names are presented in accordance with: logic 0 = 0V, GND logic 1 = +12V Nbspp ♦ The symbol denotes a physical connector pin where b=board (1-7), s=section (A,B), and pp=pin. Solid black end is the male side of the connector. White end is the female side of the connector. ♦ Sections and Signal Descriptions Signal names associated to a flip-flop are obtained from labeling on the printed circuit boards. A lowercase “n” at the beginning of a signal name indicates the logical NOT operation. Section Timing Signal PG SG G1,2 S1,2,3 POR… Description Master clock. A flag to select between memory cycles and state cycles. Timing signals for core memory read/write cycles. Timing signals for state cycling. Power-On-Reset. Keyboard KN1,2,4,8 KNP KF1,2,4,8 KFP KR1,2,4,8 Encoded numeral keys. Numeral key pressed. Encoded function keys. Function key pressed. Encoded position of the rounding switch. Control TA,B,C,D TS… Latch for the T state machine. Assorted states from the T state machine. U1,2,4,8 U=x U… FMUL, FDIV F54 FNEG 4-bit function latch. Function is x. Function signals derived with additional logic. Flags indicating that the next add/subtract completes a multiply or divide. Flag to take the state machine through the rounding sequence. Flag indicating whether the displayed number is negative. NSTx L1…L5 STx STname CAR… Next state in function execution. Current function execution state in binary form(bits of L latch). Current function execution state in enumerated form. State combinations with a particular intent. Control output to Arithmetic. FN FDP GAM BET W0 PC During number entry, flag indicating whether a new number or within a number. Flag indicating that the decimal point has been pressed during number entry. (Gamma) Flag to capture data states within a number cycle (Beta) Flag for miscellaneous uses during function execution. Flag to capture zero-state of output from arithmetic (W=0). Flag indicating the completion of program execution. Decimal Point Counter DP=n Assorted signals indicating when the DP counter matches n. Also used as a digit counter during multiply, divide and square root. Digit Counter DGTn DGTn.m DC8 Individual digit timing. 1 to 8 digit scanning, address for memory Y-axis. 8-th bit of memory digit scanning. connection between different sections. connection limited to same section. Arrows indicate direction of signal or energy flow. ♦ The symbol denotes V+12. The symbol denotes V–6. ♦ Capacitance in microfarads unless otherwise indicated. ♦ These drawings based on a unit missing the case and power supply. “7530” is stamped on some of the PCBs. ♦ Drawn Oct 2003 / Feb 2005 by bhilpert. See www.cs.ubc.ca/~hilpert/eec for additional information. Gate Identification Gates involving a transistor are identified by symbols taking the following form: <board><function><enumeration> where <board> = 1 to 7 <function> NA NO N E = for for for for NAND NOR NOT Buffer (non-inverting) <enumeration> = 1 to n Flip-flops are identified by symbols taking the following form: <board><name> where <board> = 1 to 7 <name> = is taken from the name silkscreened on the board. The preceding name formats are taken from silkscreening on the printed circuit boards. Names beginning with a “$” were created for the sake of a simulation and have no origin in the original machine. Casio AL-1000 Calculator Section: Notes & Signals Page: 2 Rendition: 2015 Mar 13 Register Selection RSrr Q PA PB Selected register, address for memory X-axis. Selects the X or Y operand register. Selects between data registers and program storage. Selects between program 1 and program 2. A, B Latches A1,2,4,8 B1,2,4,8 GR Two 4-bit latches to hold digits from memory and keyboard, and which feed the arithmetic unit. Flag to select the A or B latch to be loaded with data from core memory. Arithmetic W1,2,4,8 C Result of addition or subtraction of digits in A and B latches. Tens Carry Flag. Memory Data MR1,2,4,8 4-bit digit read from memory. D Latch D1,2,4,8 A 4-bit latch to hold the digit being displayed. Timing PG master clock G1 G2 G3 Gn memory read/write cycle timing S1 S2 S3 Sn processing timing Power Supply SG –6V +12V +20V +?V +80V +200V display supply logic supplies Keyboard Numeral Encoder Rounding Encoder Function Encoder TA TC TB TD Flags FMUL FN Function Latch FDIV FDP U1 FNEG BET F54 GAM U2 KF1,2,4,8 Control Function Decoding U4 U=x State Sequencing PC U8 R1 L1 R2 L2 R3 L3 R4 L4 R5 L5 State Decoding State Latches W0 assorted control signals to all sections DP Decoders DP DP1 DP2 DP4 DP8 Counter A&B Digit Latches B2 Inhibit Drivers B4 B8 A8 C Carry Flag 4 8 Display Digit Decoder 14 Digit Drivers D1 D2 D4 4-bit data bus 3 Sense Amplifiers Display Latch Casio AL-1000 Calculator 2 Digit Decoder Memory Core Array 4 • 8 • 14 Logically, it is organized into 6 registers of 16 BCD digits each and 2 registers of 8 digits each. Each 16-digit register occupies 2 columns in each bit plane. Rendition: 2015 Mar 13 1 14 X Address Drivers A1 A4 Section: Block Diagram Page: 3 Digit Counter 8 Y Address Drivers A2 The core memory is physically organised as 4 bit arrays, each array being 14 columns by 8 rows. PB Arithmetic (4-bit BCD adder) GR KN1,2,4,8 PA Register Selection Decoder B1 KR1,2,4,8 Q D8 BCD-todecimal decoder driver 14 Nixie Displays 43210987654321. AND Gates OR Gates NAND Gates NOR Gates bNAn bNOn r RL 5K 20K RG 20K RF 20K r % & %2 @2 - RF 10K 100K RB 50K RG 10K 15K 10K to V+20 20K to V+20 none NAND Gates - Exceptions Name R F The pull-up resistor on AND gates varies. Most are 20K, those that differ are indicated by a symbol at the output in accordance with the above table. RB T Notes Name R F 10 100 EDGE 2 NO1 6 NA2 10 100 EDGE 2 NO2 2 2 NO3 6 NA8 NOR 6 NA9 NOR 15 RF 20K RB 50K RL T 100 2 C641 100 C641 2 2 NO4 RB 50K Notes T Notes 1 N1 15 C641 EDGE 1 N2 15 C641 EDGE 1 N3 15 C641 EDGE INVERTER 1 N4 15 C641 EDGE NAND 2 N1 NAND C641 C641 3 NO1 Name R F 2 C641 3 NO2 15 2 N2 8 NA3 2 C641 3 NO3 15 2 N3 15 8 NA5 2 C641 3 NO4 15 2 N7 10 C641 3 NO5 15 2 N9 15 10 NA1 2 10 NA2 2 CF=200PF 4 NO16 C641 10 NA3 2 CF=200PF 5 NO2 NAND 10 NA4 2 CF=200PF 5 NO8 NAND 10 NA5 2 CF=200PF 5 NO14 NAND 8 N1 5 NO15 BUFFER 8 N3 6 NO2 Edge Pulse Gates 6 NO5 • Logic 0 = GND RL 5K • Most gates adhere to the standard construction and component values as indicated in the above module diagrams. Exceptions are noted in the tables. RB 50K RF 20K T C371 • A few gates are mislabeled relative to their construction. These are indicated in the Notes column with their correct function. • The load resistor of a few gates is supplied from V+20 rather than V+12. These are noted in the Notes column. The ‘Edge Pulse’ gates are fed by differentiating capacitors and resistors and are biased in such a manner that the input normally appear as 1 and the ouput 0. A 1->0 transition at an input to a capacitor sends a differentiated negative-going pulse to the transistor, enough to briefly turn the transistor off so that a 1 pulse appears at the output. Casio AL-1000 Calculator Section: Modules - Gates Page: 4 Rendition: 2015 Mar 13 8 N5 EDGE 8 N6 20 C641 2 C641 NAND C641 EDGE 2 50 2 5 N3 EDGE 2 100 C372 2 C641 2 C641 100 V+20 100 V+20 8 N7 C641 8 N8 name • Logic 1 = V+12 RL 4 N7 8 N4 6 NO1 RB 100 8 NA2 8 NA7 T C371 Inverters - Exceptions RB 15 RL 5K T C371 NOR Gates - Exceptions RL 6 NA1 6 NA3 bNn RL 5K T C371 100K Inverters C641 7 NO2 2 7 NO4 2 7 NO5 2 9 N1 10 2 EDGE (no diode) 7 NO7 2 9 N2 10 2 EDGE (no diode) 10 N5 10 2 8 NO1 100 8 NO2 100 8 NO3 20 8 N9 C641 EDGE 2 C641 C641 EDGE (no diode) INVERTER, V+20 100 C372 V+20 Buffers 10 NO1 2 10 NO2 20 2 10 NO3 20 2 10 NO4 20 2 10 NO5 20 2 NAND bEn RF 5K T C371 RL 5K Buffers - Exceptions Name R F RB 6 E1 2 - 6 E2 2 - RL 2 T Notes Bistable Flip-Flops i Monostable Flip-Flops Q M Name i RL 5K nQ nQ RF RL 5K RF Q 5K T C371 RB 50K RF 50K 5K C Q nQ T C371 Q Name nQ C641 C641 50K 100pF 50K M 20K Bistable Flip-Flop Input Options Types SE and RE 100 pF 20K 100 pF SE 20K Q goes 1 on 1-to-0 edge of SE. Q goes 0 on 1-to-0 edge of RE. RE Types nS and nR 20K 100 pF 100 pF nSD SC 20K RC nRD Q nQ 20K Q goes 1 if nSD=0 on 1-to-0 edge of SC. Q goes 0 if nRD=0 on 1-to-0 edge of RC. 100 pF 100 pF 20K Type T Type RB Q is 0 if RB is 0. RB connection to emitter ES ER Casio AL-1000 Calculator Section: Modules - Flip-Flops Page: 5 Rendition: 2015 Mar 13 Flip Flops Name R F RB RL T Notes Types ES and ER Q is 1 if ES is 1. Q is 0 if ER is 1. Name R F RB - RL T Notes 2 C641 astable 1 D1 15 2 C641 6 PG 1 D2 15 2 C641 6 SG 20 30, 68 2 1 D4 15 2 C641 6 S1 20 2 1 D8 15 2 C641 6 S2 20 2 6 S3 20 2 6 G1 15 2 C641 6 G2 15 1 C641 2 ST 20 100 2 Sr 20 - 2 DP1 15 2 C641 6 G3 15 2 C641 2 DP2 15 2 C641 6 GR 15 2 C641 2 DP4 15 2 C641 6 AC 20 2 DP8 15 2 C641 6 TA 15 2 C641 6 TB 15 2 C641 C641 monostable C=0.0047 Toggle Q on 1-to-0 edge of T. T connection to emitter Flip Flops 30, 68 3 FMUL 30 100 6 TC 15 2 C641 3 FDIV 30 100 6 TD 15 68, 50 2 C641 3 F54 30 100 6 h 15 3 FNEG 15 3 FN 30 100 7 A1 15 2 3 FDP 30 100 7 A2 15 2 3 U1 30 100 V+20 7 A4 15 2 3 U2 30 100 V+20 7 A8 15 2 3 U4 30 100 V+20 7 B1 15 2 3 U8 30 100 V+20 7 B2 15 2 7 B4 15 2 2 - C641 monostable C=0.2 C641 C372 4 BET 15 2 C641 7 B8 15 4 GAM 15 2 C641 7 C 30 100 2 5 L1 20 100 8 PA 30 100 C641 V+20 5 L2 20 100 8 PB 30 100 C641 V+20 5 L3 20 100 8 PC 30 100 5 L4 20 100 8 Q 30 100 C641 V+20 5 L5 20 100 8 1 30 100 C641 V+20 5 R1 30 100 8 2 30 100 C641 V+20 5 R2 30 100 8 3 30 100 C641 V+20 5 R3 30 100 8 4 30 100 2+3 C641 V+20 5 R4 30 100 8 8 30 2 C641 V+20 5 R5 30 100 10 W0 20 2 U≠0 + F54 0 idle if SUB•FN or SUB for multiply or divide: 1->F54 2->DP U=ALLCLR 0->DP 0->BET U=CLRENT (UADDSUB) • nFN + U=MEMACC U=MEMGET + ADD•FN U=MEMSAVE 16 0 -> X if nTRUNC: 5->X[2] 16 16 10 0->X, 0->Y 0 -> X X -> M C 26 YM [dp] – X[dp] -> YM [dp] nC • nW0 25 shift register left one digit shift register right one digit Y[dp]=0 (GAM) Y[dp]≠0 5 YM [dp] + X[dp] -> YM [dp] X ––YM [dp] W0 11 Y ++Y[dp] Y[dp]≠0 Y[dp]=0 (GAM) Y ––Y[dp] nBET • Y[dp]=0 (GAM) 5 Y[dp]=0 (GAM) Y[dp] + X[dp] -> Y[dp] 9 U=MEMACC nC • nW0 Y[dp]–KR->Y[dp] KR->X[dp] 7 Y[dp]≠0 19 Y + +Y[dp] Y[dp]≠0 26 C X[dp] + YM [dp] -> X[dp] W0 7 9 YM + X -> YM Y + X -> Y 1 -> BET (UADDSUB) • nFN 16 W0 • n(U=MEMGET • MEMACC ) 0 -> M 11 Y ––Y[dp] W0 • U=MEMGET • MEMACC 21 nW0 0 F54 BET 21 YM -> X, if nW0: 1->FNEG 0 U=MUL U=DIV UMAS 10 3 X->Y 9 -> X[16] W0 Y ++X[dp] ++DP DP=0 • W0 16 22 0 -> M2 Y – X -> Y 0 -> BET 20 Y[dp] + X[dp] -> Y[dp] DP≠0 • W0 24 26 X ––X[dp] nDP=0 • W0 9 Y + X -> Y nW0 DP=0 • W0 X->Y 19 28 W0 X ––Y[dp] if C on DGT1: 1->GAM nW0 X ––X[dp] Notes: • The following actions occur at the end of function execution, by TEND: • 0 -> DP • 0 -> BET • 0 -> U • 0 -> L (state) TEND is produced as a result of TB returning to 0 when STEND occurs. Casio AL-1000 Calculator Section: State Graph Page: 6 24 W0 X ++X[dp] M2 nGAM Y ++Y[dp] ++DP nBET if nGAM • Y[dp]>=12: 1->BET if DP=0: 1->BET 4 6 7 Y ++X[dp] 11 nDP=0 Y – –Y[dp] nW0 M2 -> X X->Y, except [dp] Y + X -> Y cycle DP, when DP=0: 5->B GAM BET 13 3 cycle DP, when DP=1: ++X[DGT] 9 X – –X[dp] when X[dp] even: 1->GAM 7 22 Y – X -> Y cycle DP, when DP=0: 5->B C 20 1 ++X[dp] Y ++Y[dp] ++DP DP=0 20 X – –X[dp] W0 9 DP<7 Y + X -> Y ++DP DP=7+15 Rendition: 2015 Mar 13 0 -> X nC 9 Y + X -> Y 16 0 -> Y C Y[dp] – X[dp] -> Y[dp] 20 21 16 14 ++M2[dp] nW0 10 nW0 SQRT2 -> U 3 -> DP U=SQRT1 X ++X[dp] nW0 5 4 UDAS 6 X->Y, except [dp] nC Group S t a t e Used During Actions ST2DGT STCOPY S T S H I F T S T D P O N L Y S T Y F I R S T C A R S U B S T D G T I N C Other State Idle 0 - - Shift 4 UMAS,SQRT1 shift Y left, ++X[dp] • UMAS ++DP • UADDSUB,UDAS,SQRT2,F54 shift Y left, ++Y[dp] • • DGT1 UDAS,SQRT2 ++DP • • DGT1 UDAS if nGAM•Y[dp]>=12 or DP=0: 1->BET • • DGT1 UADDSUB,UDAS shift X left, --Y[dp] • • DGT1 STFLIPRADP UDAS if C on DGT1: 1->GAM • • DGT1 STFLIPRADP 24 DIV,SQRT1 shift X left, ++X[dp] • Left 7 19 STFLIPRADP STFLIPRADP 28 UDAS shift M2 left including [dp] • • Shift 11 SQRT1,F54 shift Y right, --Y[dp] • • Right 20 DIV,UDAS,SQRT1,SQRT2 shift X right, --X[dp] SQRT1 if X[dp]=even after decrement: 1->GAM UADDSUB,UMAS,UDAS,SQRT1,SQRT2,F54 YM + X -> YM, 0 -> FNEG • negate* • F54 1 -> BET • negate* • SQRT1 ++DP • SQRT2 cycle DP, when DP=0: 5->B • UDAS,SQRT2 Y - X -> Y, 0 -> BET • • • SQRT2 cycle DP, when DP=0: 5->B • • • UDAS,SQRT2 X -> Y, but [dp] not copied • • MUL,DIV X -> Y • • Arithmetic 9 22 Register Copy 6 10 STM2FORY DGT1 STDGTDOWN • DGT1 STDGTDOWN • DGT1 • • negate* MEMSAVE X -> M • • 13 UDAS M2 -> X • • • 21 fin YM -> X, if nW0: 1->FNEG • • • negate* STM2FORY negate 1 SQRT1 ++X[dp] Point 5 UADDSUB,UMAS,F54 Y[dp] + X[dp] -> Y[dp] Only 14 UDAS ++M2[dp] • • 25 UADDSUB X[dp] + Y[dp] -> X[dp] • • • 26 UADDSUB,UDAS Y[dp] - X[dp] -> Y[dp] • • • F54 Y[dp] - KR -> Y[dp], KR -> X[dp] • • • ALLCLR 0 -> X, 0 -> Y • CLRENT,SQRT2,F54,fin 0 -> X UDAS 0 -> M2 • SQRT1 0 -> Y • MEMGET 0 -> M • F54 if nTRUNC: 5 -> X[2] UMAS 9 -> X[16] SQRT2 cycle DP, when DP=1: ++X[DGT] Other 16 3 STDGTDOWN • Decimal Clearing Signals • • • STM2FORY • STM2FORY negate: if FNEG: CARSUB occurs during nDGT1 negate*: may negate under some circumstances(?) Casio AL-1000 Calculator Section: State Descriptions Page: 7 Rendition: 2015 Mar 13 Power-On Timing Sequence PG POR PORAC AC PORC Gn Primed to G3 Ready Sn Inhibited Ready Power-On Power-On capacitor charged TAB and U loaded to execute All-Clear Basic Core Memory Timing and the Display Cycle 540 585 630 720 0µS 675 45 State Transition Timing 90 PG PG G1 G1 G2 G2 DGT= core memory read core memory write DGT2 DGT1 SG DGT2 S1 DGT15 S2 DGT= 10x digit in A latch 10x digit displayed DGT16 D latch DP load Section: Timing Diagram Page: 8 Rendition: 2015 Mar 13 4 DP increment 3 2 A latch • PG measured as 66 KHz. Casio AL-1000 Calculator DGT1 3 2 1 2 1 0 1 DP 0 16 SN 15 13 S3 R latch L latch 3 2 1 1 1 2 1K 500 2SF101 6E1 N6A26 Memory Read/Write Clock Cycle Generation 100pF 6NA1 6N1 10K 20K Memory / State Clock Cycle Selection nTREQUEST nDGT1 nSTDPONLY DGT1 nSD Q SC 6G1 nSD Q SC 6G2 RC nRD nQ ER RC nRD nQ ER ES nSD Q SC 6G3 RC nRD nQ G1 0 1 0 0 G2 0 0 1 0 G3 1 0 0 1 G2 nSD SC nSD Q SC 6SG N6A13 N1B13 N2A1 nG2 N6A11 N9A18 RE nQ nSG N10A7 G1 N6A24 N8A20 N6A9 N9B25 nG1 N10B31 Master Clock 2K 270pF 6PG State Clock Cycle Generation 270pF 20K 2K 6NA2 6NA11 100pF C641 C641 50K 50K PG (to Arithmetic: carry clock) % N6A22 N2A14 Power-On Reset nSD Q SC 6S1 nSD Q SC 6S2 nSD Q SC 6S3 RC nRD nQ RE RC nRD nQ RE RC nRD nQ RE 2N1 2N4 20K 25 25V 2K C371 2N5 C371 N2B25 N6A6 RE POR 0.0033 50V 15K 5K M 5K Q 2Sr N5A6 S2 N6A16 N3A27 nPORC N8A28 nS2 nQ 2N3 S3 0 0 0 1 1 1 0 nS3 N6A7 6AC 2K S2 0 0 1 1 1 0 0 n(AC+PORC) PORC Q S1 0 1 1 1 0 0 0 N6A18 N2B20 N3A30 N6A5 N4A6 N6A3 N2A8 S1 PORAC (to T machine and Function, to generate All-Clear) N3B7 100 N4A4 nQ N7B25 N8B41 N6A1 N2A18 Casio AL-1000 Calculator Section: Timing Page: 9 Rendition: 2015 Mar 13 nPORC 2NO2 N2A22 N5A4 S1+PORC (to R Latch) whi-whi N3A16 nKCHS CHS 300K N2B6 whi-red N3A19 N2A42 nKDP 200K + V+blu 300K N2B3 0.022 50V V+blu 200K red-red N2A23 1 V+blu 200K red-whi N2A25 2 V+blu 200K red-blu N2A27 3 V+blu 200K red-yel N2A29 4 V+blu 200K red-grn N2A31 5 V+blu 200K red-vio N2A35 6 V+blu 200K red-blk N2A37 7 V+blu 200K red-bwn N2A39 8 V+blu 200K red-org N2A41 300K 200K – V+blu 4 of 20K whi-blu 0.022 50V N2B5 200K M1 V+blu 300K whi-yel 0.022 50V N2B7 200K M2 V+blu 300K whi-grn 0.022 50V N2B9 200K M3 V+blu 300K whi-vio N2B11 0.022 50V 200K M4 V+blu 300K whi-blk N2B13 0.022 50V 200K x V+blu 300K whi-bwn N2B15 0.022 50V 200K ÷ V+blu 300K whi-org N2B17 0.022 50V 200K AC V+blu 300K whi-gry N2B19 0.022 50V 200K KC V+blu 300K 0.022 50V 9 blu-red N2A15 N7A36 N2A19 N7A28 N2A17 N7A18 N2A13 N7A12 nKN1 nKN2 nKN4 nKN8 √ N2B21 200K 300K 4 of 20K N6B13 0.022 50V V+blu red-gry N2A40 N2B8 N6B39 300K 0.022 50V 0 Casio AL-1000 Calculator Section: Keyboard Page: 10 nPREXEC Rendition: 2015 Mar 13 nKNP (to PB flag) (to T state machine) 300K 0.0022 whi 300K yel-bwn N8A5 yel-red N3A22 yel-blk 0.022 50V 300K nPRSEL2 (to PB flag) PRENB (to T state machine, PB flag, FN flag, Display) V+20 0.022 50V N6B31 300K N8A24 0.022 50V 2K 300K 0.022 50V yel-whi yel-blu 300K N8A11 N1A41 20K nPWENB (to PA flag, Display) N2B26 0.022 50V 300K 0.022 50V yel-org TRUNC N7B5 nTRUNC 300K 0.022 50V 300K 0.022 50V % N2A20 N3A10 nPORC N8A3 300K 0.022 50V 300K 0.022 50V n(AC+PORC) N6A8 N2B12 N3A40 N2B16 N3A38 N2B14 N3A36 N2B10 N3A28 nKF1 nKF2 nKF4 nKF8 20K (extra) 200K 200K nPWSEL2 0.022 N2B22 yel-grn N7A4 N2B4 N8A7 V+blu 0.022 50V DP WRITE yel-yel NML yel-vio RUN red nKFP N2B18 N6B41 RND OFF \/ 0 1 2 3 4 5 6 7 8 vio-red vio-whi vio-blu vio-yel vio-grn vio-vio vio-blk vio-bwn vio-org N2A11 N2A28 N2A30 N2A32 N2A34 N2A36 N2A21 N2A9 N2A7 N2A5 N7A44 N2A24 N7A32 N2A26 N7A24 N2A38 N7A16 nKR1 nKR2 nKR4 nKR8 CD=00 : TSDISP - display CD=10 : TSFETCH - instruction fetch CD=01 : TSFCT - function execute CD=11 : TSNML - numeral entry 11 TSNML CD=00 : TSDISP - display CD=10 : TSFETCH - instruction fetch CD=01 : TSFCT - function execute CD=11 : TSNML - numeral entry 11 TSNML KNP KNP RUNPLUS 00 TSDISP 00 10 KFP STEND • nRUN KFP STEND • RUN 01 U≠0 01 $T1 M 10 TSFETCH STEND • nRUN TSFCT TSFCT nKNP nKFP RUNPLUS TSDISP TSFETCH U= STPEND U≠0 STEND • RUN 01 U=STPEND TSFCT % N6A14 N2A6 S1 nS2 Q nPREXEC PORC 6h TEND (to DP counter) N2A4 N3A24 2NO1 N4A13 N5B41 nQ PRENB SE Q N2B34 N6B33 ST 6NA3 nSD SC nSD SC nSD SC 2ST U=STPEND nKFP RE RE nQ nS3 n(AC+PORC) UFCTREQST U=MEMACC ST9 U=ALLCLR ST16 U=CLRENT ST16 4N7 ST21 S1 nS2 W0 $STE7 nMEMACC nSD Q SC 6TC RC nRD nQ RE RE nTC nTD RC nRD nQ RE nTC N6B27 N8A31 6NA5 TC N6B11 N3A18 TD N6A21 N5A25 PORAC $STE5 $STE6 4 NO16 N4A3 N6A37 nSTEND - Q $STE1 TD nSD Q SC 6TD 6TB RC nRD nQ RE RE RE $STE4 $STE2 SE SE nSD SC nSD SC (to L state latch) TC N6A41 N8A13 $STE3 U=MEMGET ST16 S1 Q 6TA (to Beta flag) nTREQUEST (to Timing - SG) nTC nTD nS2 n(TEND+PORC) (to Function latch) RC nRD nQ nTD N6A39 N2A12 TSNML2 (to Control for arithmetic) TSNML4 (to A latch) % TSFETCH (to Function latch, Arithmetic, PA, PB flags) nTD N3A26 TSNML (to FNEG, FDP, FN flags) TSNML3 (to A & B latches) - TC nTSDISP (to Digit Counter) 8N1 nTSFETCH (to PA, PC flags) N8A16 N3A20 nSTEND (to flags[3] ) (extra diode on TB reset inputs) N6A35 N2A10 N4A33 nTC TB (to DP counter) TB (to Beta flag) TD nTD TSDISP+FCT (to Arithmetic) TSNML+FCT (to A & B latches[3] ) TSDISP+FETCH (to A Latch, DP counter) n(TSNML+FCT) (to Function latch: load KF) Casio AL-1000 Calculator Section: Control - T State Page: 11 Rendition: 2015 Mar 13 TSFETCH DP=0 nDGT1 8NA5 N8A4 N3A34 nULDINSTR nU1 U2 nU4 U8 n(TSNML+FCT) U=SQRT1 DP=7+15 S1 $CU1 nW1 nKF1 SE nSD SC nSD SC Q U1 3U1 RE RE PORAC nW2 nKF2 nQ SE 200pF nSD SC nSD Q SC nU1 U2 nW4 nKF4 Q nU1 nU2 U4 U8 RE nQ FMUL Q RE RE U1 nU2 U4 U8 U4 N3A7 N2B33 nFMUL UMAS N3B13 N4A16 N5A15 U=SQRT2 N7B23 N4B9 N3A13 N8A1 nU4 N3A17 N2B24 UMAS U1 U2 nU4 nU8 n(AC+PORC) U=DIV FDIV Q RE RE nFDIV nQ N3A35 N4A34 ADD+SUB FN nU2 nU4 nU8 U=STPEND % U2 nU4 nU8 UDAS N3B15 N4B3 N5A17 UNUL (to State Sequencing) ADD+SUB U4 % U=MEM nU8 % N3B17 N6A12 UFCTREQST (to T Latch) N3A15 N8A30 nU1 @2 U=MEM1 nU2 N3B21 N8A29 U1 ADD+SUB nFN S1 UD54 3NA1 SE SE SE Q N3A8 N4A26 @2 U=MEM2 RE RE @2 U1 U2 U4 @2 F54 N10B37 nQ 3N1 nU1 U2 U4 N7B11 3F54 N3B33 N8A34 nU=MEM2 U=MEM3 N3B11 N8A38 U=MEM4 N3B3 N8A40 nF54 U=CLRENT U=MEM nSTEND PRENB nPB N4A5 FNEGSET N3A3 SE 200pF nSD SC 200pF nSD Q SC FN N3A25 N6B35 3FN $FNG1 UCHS nKCHS SE SE SE SE Q N3A6 N1A3 N5A23 nU2 U8 $FNG2 S1 Section: Control - Function Latch & Decoding Page: 12 Rendition: 2015 Mar 13 SE nU2 U1 Casio AL-1000 Calculator U=END UM54 ST21 S1 nS2 nW0 U1 nU2 nU4 nU8 nU1 nF54 nSTEND n(AC+PORC) nU8 N3B29 N4A14 U2 nU4 nU8 nFMUL nFDIV USUB ADD+SUB FN S2 U8 U1 nU2 nU4 U8 3FDIV nQ U2 nU4 nU8 N5B19 3U8 n(TEND+PORC) U=MUL U=SQRT1 U1 SE 200pF nSD SC nSD Q SC n(AC+PORC) N3B9 N4A40 UDAS nW8 nKF8 SE U=CLRENT nU2 3U4 nQ N3B31 N4B15 3FMUL N3A9 N4A25 U2 U4 U8 nDGT1 nSD SC nSD SC RE U1 U2 nU4 U8 U1 nQ nU1 nU2 nU4 U8 U=ALLCLR N5A18 N5B11 3U2 RE N3A11 N4A19 U=CLRENT ST9 TSNML n(AC+PORC) 3FNEG RE RE RE RE RE nQ FNEG Function Code Change Sign 1 Add 2 Subtract 3 Memory 1 4 Memory 2 5 Memory 3 6 Memory 4 7 Multiply 8 Divide 9 All Clear 10 Clear Entry 11 Square Root 12 Square Root (part 2) 13 Stop (data entry) 14 End Program 15 Display 1 2 3 4 5 6 7 8 9 2. 3. 4. 5. 6. 7. U=MEMGET TSNML RE RE nKDP nSTEND SE SE nQ nFN Q FDP N3A23 N6A28 3FDP U=CLRENT TSNML FN S1 $FDP1 RE RE nQ nFDP ST4 B40 U=SQRT1 B41 UMAS D40 ST0 D41 ST22 U=SQRT2 nC A26 A27 A28 4N1 4 NO15 nNST1 nNST3 ST5 D37 UALIGN D42 UDAS ST22 C A21 A23 B37 ST1 U=SQRT1 W0 A22 B36 B38 A24 A25 B39 C29 D38 D39 ST5 D4 UMAS D5 ST22 U=SQRT2 C nDP=0 W0 ST9 UMAS C5 C6 C7 D6 ST4 nW0 UMAS GAM U=SQRT1 ST20 B6 B7 B8 ST11 4 NO5 nNST4 ST20 C8 U=DIV D14 U=MEMSAVE B9 ST0 U=SQRT1 B10 ST19 UADDSUB GAM C16 D24 D25 ST0 W0 ST26 UALIGN C18 C19 D26 ST7 UALIGN GAM C20 D27 D28 ST11 nBET GAM F54 C21 C22 D29 D32 ST3 C23 UMAS D30 U=SQRT2 A15 ST20 B30 ST13 U=SQRT2 A29 ST9 B42 ST28 ST26 C UALIGN U=MUL 4 NO9 4 NO13 4 NO2* nNST5 nNST6 nNST7 C31 C32 D43 A8 B21 4 NO7 4 NO11 UDAS ST19 nW0 A4 B11 B12 U=SQRT2 DP=0 ST7 A3 B13 B14 ST6 ST10 A7 D7 nW0 D8 ST9 C10 UADDSUB D16 nNST1 BET ST11 F54 C11 C13 D17 nNST3 ST9 W0 UMAS DP=0 C12 C14 D18 D19 nNST6 N5B39 N4B19 5NO 15 nNST4 nNST5 nNST7 nNST9 nNST10 4 NO12 nNST21 nNST11 nNST13 C30 B20 ST0 D15 nNST16 ST9 C26 U=MEMGET D21 nNST19 F54 D35 ST0 D23 nNST20 ST1 nW0 U=SQRT1 A20 B34 B35 nC ST26 nW0 F54 C27 C28 D34 D36 W0 ST4 DP=0 UMAS C15 C17 D20 D22 UDAS nBET ST7 A9 B19 B22 UDAS ST7 BET A18 B32 B33 4N5 nC ST22 UDAS A14 A17 A19 4N12 U=ALLCLR C1 ST0 C2 F54 C3 ST0 D1 UDAS A1 ST0 B1 4 NO6* nNST11 nNST14 A10 ST20 B25 U=SQRT2 A11 ST3 B26 U=SQRT2 ST7 nDP=0 A13 B28 B29 U=SQRT2 A12 ST16 B27 ST16 B15 U=SQRT1 B16 B3 DP=7+15 ST9 U=SQRT1 A2 B4 B5 W0 ST21 U=MEMGET C4 D2 D3 ST16 C9 U=CLRENT B23 F54 D12 ST0 B24 UADDSUB D11 UDAS A16 ST0 D13 ST25 B31 nNST21 nNST22 nNST24 nNST25 nNST26 nNST28 N4B35 N5A3 nSNXT1 UDAS B2 ST26 nNST14 ST14 nNST13 ST0 Section: Control - State Sequencing Page: 13 Rendition: 2015 Mar 13 5 of 20K UNUL U=SQRT1 Casio AL-1000 Calculator nNST20 ST24 nNST9 nNST10 4 NO2 4 NO14 4 NO6 nNST16 nNST19 U=DIV D9 ST0 D10 ST26 nC UADDSUB nW0 C24 C25 D31 D33 UDAS A6 ST16 B18 UDAS A5 ST9 B17 nSD SC SE Q 4 NO8 nNST22 N4B27 N5A5 nSNXT2 nSNXT3 4 NO1 nNST24 nQ RE nQ nL1 nSD SC Q SE Q L2 nNST25 5L2 RE nQ RE nQ nL2 nSD SC Q SE Q L3 5R3 N4B29 N5B15 4N4 nSNXT4 5L3 RE nQ RE nQ nL3 nSD SC Q SE Q L4 5R4 4 NO10 N4B37 N5B25 nNST26 nSNXT5 nS3 S1+PORC 4N3 nNST28 n(TEND+PORC) L1 RE 5R2 N4B33 N5A7 Q 5L1 5R1 5L4 RE nQ RE nQ nL4 nSD SC Q SE Q L5 nQ nL5 5R5 RE nQ 5L5 LCLR % RE nL1 nL2 nL3 nL4 nL5 L1 nL2 nL3 nL4 L2 nL3 nL4 nL5 N5A36 N4A31 5G L11 nL1 nL3 nL4 L5 ST0 5G L10 5N1 nST16 ST16m 5G L5 L1 L2 L5 ST3 N5B7 N2B35 nST3 N5B21 N6B9 5G L22 ST4 N5A28 N4A36 5G L13 nL1 L2 nL4 nL5 5G L16 L1 L2 L3 5G L25 nL2 nL3 L4 nL5 5G L6 nL1 L2 nL3 nL5 5G L17 L1 L2 L4 5G L21 L1 L3 L4 5G L19 ST5 N5A31 N4A18 % ST6 ST7 N5A20 N4A12 5GM6 N5B3 N3A14 0.001 ST19 ST9m 5G L20 L1 L3 L5 5G L18 L2 L3 L5 5G L15 nL1 nL2 nL3 L4 5G L24 L1 L4 L5 5G L14 L2 L4 L5 5G L12 L3 L4 L5 ST10 5G L8 5N3 % ST13 N5A24 N4B23 ST20 N5A29 N4A41 ST21 % ST14 N5A35 N4B25 ST3 (to DP Counter) ST3 (to Arithmetic[2]) nST3 (to A,B Latch) ST7 (to BET) ST7 (to DP Counter) ST9 (to DP Counter) ST9 (to BET) ST9 (to STEND,FNEG) Resistor on 5GL5 and U=MEMGET (fed by 3N2) is 20K, consistency with others would suggest it should be 10K. nST16 (to B Latch) ST16 (to Arithmetic) ST16 (to STEND) Casio AL-1000 Calculator Section: Control - State Decoding Page: 14 Rendition: 2015 Mar 13 5GM16 5 NO9 ST22 N5A32 N4B7 ST24 N5A22 N4A20 % ST25 N5A34 N4B21 L1 ST26 N5A33 N4A32 % N5A38 N4B17 N5A40 N6A32 L5 L1 L2 nST3 ST28 ST16 U=MEMGET nST28 ST16 U=SQRT1 L3 ST19 (to GAM) L4 ST20 (to GAM) L2 ST21 (to STEND,FNEG) L5 ST22 (to BET) ST26 (to B Latch) nST28 (to Control for Arithmetic) ST5 ST25 ST26 5GM11 ST1 5GM10 5GM15 ST14 N5A30 N4A21 Other State Destinations ST4 (to DP Counter) 5G L7 ST6 ST9m ST22 5 NO5 N5A13 N6B17 5NO8 ST16 N5A27 N4A29 5GM17 N5A26 N4A17 UDAS ST11 ST6 ST10 ST13 ST21 nSTALNOMEM (suppress loading of A latch from core) (to A Latch) nSTCOPY (to B Latch) nSTDGTINC (skip DP digit) (to DGT Counter) ST2DGT (doubled digit period number cycle) (to DP, B Latch, Control for arithmetic, Arithmetic) nST2DGT (to GR flag, Q flag, A Latch) nSTDPONLY (to Timing) STSHIFT (to Control for arithmetic) nSTDGTDOWN (DGT Counter counts down) (to DGT Counter, Control for arithmetic) nSTFLIPRADP (Flip Registers After Decimal Point) (to Register Addressing) nSTYFIRST (Start cycle with Y register instead of X) (to Register Addressing) nSTM2FORY (Use M2 instead of Y) (to Register Addressing) STPSUB (some subtract states) (to Control for Arithmetic) N5A11 N6B29 nL1 nL2 L3 nL4 L5 N10B39 N4A42 % 5G L23 N5A14 N6A29 U=ALLCLR N5A9 N6A31 5N2 L2 L3 L4 ST16m N4B5 N7B21 L1 nL2 L3 nL4 nL5 N7B7 5GM9 ST1 N5B5 nST16 ST16 N5A37 N4A27 470 pF N4A39 nL1 nL2 L3 nL5 5G L9 ST24 ST7 ST28 TSNML2 5GM22 5GM23 ST20 5GM18 ST11 5GM19 ST4 5GM20 ST19 5GM21 5G L3 ST19+21+25 5G L4 ST7+11+19 5 NO6 6N2 N5A16 N6A10 5 NO7 5 NO1 5 NO3 5 NO4 5NO2 N5A8 N6A30 N5A12 N8A36 N5A10 N6B15 5 NO13 5G M13 N5B17 N8A26 5G M14 5G M8 5G L1 ST13+14+28 5G L2 ST19+22+26 5 NO12 N5B35 N8A32 I II III IV grn-red grn-whi N3A39 M K + grn-blu N3B19 grn-yel N3A43 M K + grn-grn N3B25 grn-vio N3B23 M K + grn-blk N3B27 grn-bwn U=MEM1 N3A41 M K + N3A29 FMUL $M1S U=MEM2 U=MEM FDIV $CM2 $M2S 3 NO3 nMEMSAVE 3 NO5 2K U=MEM3 $CM1 FN 2K nFDP N3B37 N4A23 $CM3 $M3S 2K U=MEM4 U=MEMGET (to FN flag) 3N2 U=MEMGET (to CMCB, State Sequencing[2] ) N5A19 U=MEMGET (to State Decoding) $CM4 $M4S N3B39 N4B13 $M1A N3B41 N4A8 U=MEMSAVE (to State Sequencing) 2K U=MEM1 2K U=MEM2 $M2A 3 NO4 2K U=MEM3 2K N3B35 N4A7 $M3A nMEMACC (to T latch - STEND) ADD+SUB nFN U=MEM4 U=MEMACC (to T latch - STEND) 3 NO2 3N3 N3A4 N4A28 UADDSUB (to State Sequencing[4] ) $CM5 $M4A 3NO1 nF54 N3A1 N4A24 UALIGN (to State Sequencing[4] ) UALIGN (to Gamma flag) 2K U=SQRT1 ST20 DGT1 A1 UALIGN W0 UDAS ST19 C S1 UDAS 4N8 UDAS ST7 $BET1 $GAM1 A4 N7A35 N4A11 A8 A8A4 TB UDAS nDP=0 $GAM2 4 NO17 $GAM3 DGT1 SE nSD Q SC 4GAM DGT1 $BET2 F54 GAM $BET3 ST9 SE SE SE STSHIFT Q % nST28 DGT1 BET CARCYINJ (to Arithmetic) 6N3 4BET nCARCYINJ (to A latch) N6A17 N7B3 $GAM4 RE nQ ST22 n(TEND+PORC) RE RE nQ nBET 6E2 GR nW1 nW2 nW4 nW8 N10A9 10NO1 nSD Q SC 10W0 nG2 RC nRD nQ 10N6 N10A11 N4A30 W0 n(AC+PORC) U=END nPB N8A18 N10A3 N4A22 SE SE SE nW0 RC nRD nQ PC (to A latch & display) nDGT1 FNEG STPSUB 5G M12 5 NO11 5NO14 N5B33 N6A36 CITSUB nGR 6 NO4 $CAR2 DGT1 Casio AL-1000 Calculator CARNOBC (to Arithmetic) $CAR1 nSTDGTDOWN N10A5 Section: Control - Miscellaneous Page: 15 Rendition: 2015 Mar 13 N6A42 N7A39 ST2DGT Q 8PC DGT1 nTSFETCH CARNOA (to Arithmetic) nGR N6A40 N7A33 nCARSUB (to Arithmetic) n1 n4 n8 200pF G2 nGR 20K 6NO1 N6B19 N8A15 N5B13 200pF G2 nST2DGT 8NA2 DGTCLK (to DP Counter) n2 4 8NA3 20K nSD SC nSD SC %2 8N9 8N3 n4 S2 20K 470pF nSTDGTINC 2 S1 Q N6A34 1 nDGT1 8A39 RC nRD nQ RC nRD RB nTSDISP n1 % DGCNTUP nSD SC nSD SC Q N6A4 N7B33 2 8.2 nSTDGTDOWN 8N5 DGCNTDWN 1 3 n4 n2 RC nRD nQ RC nRD RB nSD SC nSD SC Q n2 1 0 1 1 1 1 0 0 0 0 3 2 0 0 1 1 1 1 0 0 0 3 0 0 0 1 1 1 1 0 0 4 0 0 0 0 1 1 1 1 0 1 n2 n8 @2 n3 4 8 @2 n1 @2 N8A41 N6B37 N8B39 N5B9 200pF 4 2 n3 @2 N8B31 N9B21 1 n3 nSD Qs SC nSD Q SC 3 n1 @2 N8B29 N9B19 4 1 @2 N8B35 N9B17 n4 n1 @2 N8B37 N9A26 n2 DGT5.13 N1A15 @2 N8B27 N9A24 2 100pF DGT4.12 N1A17 4 RC nRD nQ RC nRD nQs RB DGT3.11 N1A31 n4 8.4 DGT2.10 N1A29 n3 3 DGT1.9 N1A27 n2 RC nRD nQ RC nRD RB N7B17 N8B33 N9B23 n4 1 DGT6.14 N1A11 @2 N8B25 N9A22 3 DGT7.15 N1A13 20K 100pF 20K Q 8 8NO1 8N8 n3 @2 N8A43 N9A20 4 DGT8.16 N1A33 8 8.8 DC8 8A27 N1A35 8A25 N1A9 T n8 Casio AL-1000 Calculator Section: Digit Counter Page: 16 Rendition: 2015 Mar 13 RB nQ n8 DGT2 N7B9 8.3 2 N3A37 N5A21 n1 20K n3 N2A3 N4A10 8.1 200pF DGT1 8A37 0.001 nDC8 DGT16 TSDISP+FETCH N6A23 N2B30 G2 U=SQRT2 ST3 DGTCLK DPINCB 100pF 20K TSDISP+FETCH 5G M1 U=SQRT2 ST2DGT GR 5G M2 U=SQRT1 ST9m DGT16 5G M3 U=SQRT2 ST7 DGT16 5G M4 UDAS ST7 DGT16 5G M5 UMAS ST4 DGT16 5G M7 DGT1 G2 100pF 2N9 5 NO10 N5B23 N2B28 DPINCA 100pF 20K Rendition: 2015 Mar 13 nSD Q SC T 2DP1 RE $DP1 nW2 nQ SE nSD Q SC T 2DP2 RE nW4 nQ nSD Q SC T 2DP4 RE RE nW8 nQ nSD Q SC T 2DP8 RE RE 2N6 n1 1 n2 2 n4 4 N2B37 N1A39 DP=0 N4B31 N5B29 N8A14 DP=0 nQ 1 n2 n4 n8 2NO3 U=SQRT2 Casio AL-1000 Calculator Section: Decimal Point Page: 17 nW1 2NO4 TB S1 TEND n1 n2 n4 n8 2N2 n8 1 2 4 4N6 nDP=0 - DP=1 (to Carry flag) N2B41 N3B5 N4A44 DP=7+15 200pF G2 20K nST2DGT 6NO2 200pF PA S1 nSD Q SC 8Q T S2 nSTYFIRST nPA RC nRD nQ RE N6B21 N8A22 QT DGT1 20K 8N7 X OPERAND @2 N8B23 N9B15 nDC8 @2 N8B21 N9B13 Y OPERAND DC8 nSTFLIPRADP @2 (2) RSXH (4) RSYL (6) RSYH (8) RSM1L (10) nDC8 nPA U=MEM @2 N8A35 N9B9 RSXL 8NO3 8N6 $RSY 8N4 @2 @2 N8A33 N9B11 nXY DC8 nSTM2FORY U=MEM1 nTSFETCH nPWENB SE nSD SC Q nDGT1 8PA TSFETCH n(AC+PORC) RC nRD nQ RE RE 8NA1 PROGRAM STORAGE PA (to A latch: enable DP / bit 8) nU=MEM2 REGISTERS N8A9 N7B31 nPA nPA (to Arithmetic: inhibit normalisation) $RSM2 @2 nXY nPA nDC8 @2 N8B19 N9B7 nXY nPA DC8 @2 N8B17 N9B5 nXY nPA nDC8 @2 N8A42 N9B3 nXY nPA DC8 @2 N8B3 N9A15 nXY nPA nDC8 @2 N8B5 N9A13 nXY nPA nDC8 @2 N8B15 N9A11 RSM1H (9) 8NO2 RSM2L (7) RSM2H (5) U=MEM3 nPRSEL2 nPWSEL2 nDGT1 PA TSFETCH W0 $PB2 RSM3L (3) RSM4L (1) RSP2L (13) RSP2H (11) RSP1L (12) RSP1H (14) U=MEM4 $PB1 8N2 DGT1 nPA PRENB PA PRENB U=END n(AC+PORC) SE nSD SC nSD Q SC 8PB RC nRD nQ RC nRD RE RE additional diode between input diodes and base Casio AL-1000 Calculator Section: Register Selection Page: 18 Rendition: 2015 Mar 13 $RSP2 @2 nXY nDC8 nXY DC8 nPB (to PC flag) 8A12 N3A21 nPB (to FN flag) $RSP1 @2 N8B7 N9A5 @2 N8B9 N9A3 @2 nXY nDC8 nXY DC8 @2 N8B11 N9A9 @2 N8B13 N9A7 TSNML3 FN 6NA4 nSTALNOMEM nGR TSFETCH PC DGT1 8NA4 $ALD1 N8A6 N6A27 nALDMINH TSDISP+FETCH TSNML4 DGT2 G1 6 NO3 N6A44 N7A14 TSNML+FCT nST16 GR nALDMENB $ALD2 F54 ST26 (from Mem Sense) G1p N6B25 N7A10 6NA6 ALDKNCLK nMSENSE1 nKN1 nSD SC nSD SC Q G2 nS3 nSD SC Q nMSENSE2 nKN2 GR (load B latch) N6A33 N5B27 RE BLDKRCLK A1 U=SQRT2 ST2DGT nSTCOPY DP=0 nGR N4A15 nQ nSD SC nSD SC T 6GR N10B41 N7A40 10NA1 nMSENSE1 nKR1 nA1 N7A29 nST2DGT S2 nBLDMENB N7A31 N1B9 7A1 RB N6B3 N7A22 6NA10 Q SE nSD SC nSD SC N5B37 N7A42 5NA1 nGR (load A latch) RB N6A15 N5B31 RB nMSENSE2 nKR2 A2 N7A15 N1B11 nMSENSE4 nKN4 nQ T nSD SC nSD SC RB PA DGT2 G1 Note: Curious connection between resistor-cap-diode junctions of T and RE inputs on GR flip-flop. Would appear to be a board design flaw which turns out to be of no logical consequence. N8A17 N7A7 8NA7 10K ALDDP nKDP nA2 Q RB nMSENSE4 nKR4 A4 N7A13 N1B5 nMSENSE8 nKN8 B2 nQ nB2 Q B4 nQ nB4 Q B8 SE nSD SC nSD SC nA4 Q A8 N7A3 RB nMSENSE8 nKR8 N1B3 nSD SC nSD SC 7A8 RB Q 7B4 nQ nSD SC nSD SC nSD SC nB1 nSD SC nSD SC 7A4 RE nQ 7B2 nS SC B1 nBLDFIVE 7A2 nQ Q 7B1 nQ 7B8 nA8 RB nQ nB8 N7A5 TSNML+FCT nST2DGT nST3 nCARCYINJ nGR nSG nG2 $AC1 $ABC1 6 NA9 N6B5 % Casio AL-1000 Calculator Section: A & B Latches Page: 19 Rendition: 2015 Mar 13 N7A6 ACLR 560pF 50K 20K TSNML+FCT nST3 GR $BC1 6 NA8 N6B7 N7A8 BCLR 470pF 50K 20K nCARSUB 7N11 CARNOA 7N3 nB1 7 NO13 $A11 A1 nA1 CARNOBC CARNOBC CARNOA nCARSUB 7N12 0 0 0 W=A-B-C 0 0 1 W=A+B+C 0 1 0 - 0 1 1 W=B+C 1 0 0 W=A 1 0 1 W=A 1 1 0 W=0 1 1 1 W=0 U=SQRT2 ST3 DP=1 7N15 6 NO5 FDP nA1 $A17 A2 $A23 nA2 $A22 % $A24 nA2 7 NO6 nSD SC nB4 7N16 Q 7N2 nS2 S2 7 NO5 $ACONST5 N7B29 N2B27 nW2 N3A33 $AS22 S2 S4 $AS41 N10B29 nS2 nS4 $AS42 nAC2 C A4 $A42 $AS43 $A43 $AS44 nCARSUB % 7N1 $A27 7N5 nA4 AC2 B4 7 NO17 $A41 7 NO3 $A26 CARSUB 6NA7 7N7 % $AS21 $CGAT N7B39 N4A38 $ACONST9 $A25 A2 N6B23 CYCLK N7B27 % nS2 N6A19 N7A37 ARCYENB F54 ST16 nTRUNC DGT2 nAC1 S2 7 NO16 nGR nGR G2 PG UMAS ST3 DGT16 $A16 $CIDP ST2DGT nW1 N3A42 7N14 N7B13 ARCYINJ2 N6A38 6N4 $CINC CARCYINJ 7 NO15 $A21 AC1 B2 7 NO1 ARCYINJ1 N7B15 N2B23 7 NO2 7 NO14 nB2 N8A8 N7A26 $A14 N10B23 A1 ARCYINJ3 DGT1 $A12 % $A15 N2B39 N7A17 TSFETCH TSDISP+FCT B1 Function $A13 7N13 $A44 7 NO8 7N6 7 NO4 N7B35 N2B29 nW4 N3A31 N10B27 S4 S4 nS4 $AS45 $A45 7C S1 RC nRD nQ RE N7B41 N4B11 nC A4 S8 $A46 7 NO9 WC nB8 7N8 $A47 A8 $A83 $A82 % $A84 7 NO10 7N9 A8 $A86 Casio AL-1000 Calculator Rendition: 2015 Mar 13 7NA1 7N4 S2 nS8 $AS82 7 NO7 N7B37 N2B31 N3A32 N10B25 $AS83 S8 nS8 $A85 Section: Arithmetic Page: 20 S2 S4 S8 nPA nDGT1 7N10 nA8 AC4 B8 7 NO11 $A81 nA4 nAC4 $AS81 7 NO12 nA8 $A87 nAC8 S2 S8 $ASC1 S4 S8 $ASC2 7 NO18 7NA2 WC N7B19 nW8 V+20 C371 C367 9B3 9B4 C367 C367 C367 9E30 1K 0.01 50V 9E28 9E70 2K 0.01 20 C367 1K C367 200pF 10K 9E76 300 9N4 RSXL 9E8 9E7 RSM3L 9E26 9E25 9B7 9B8 RSXH 9E11 9E10 C367 C367 RSM2H 9E23 9E22 1K 0.01 1K RSM4L 9N1 100pF 10 20 C367 500 9N3 nG2 20 C367 20 C367 RSYL 9E2 9E1 RSM2L 9E20 9E19 RSYH RSM1H 2K 500 RSM1L 300 9N7 C367 9E67 TDK PT-16M4 9N8 9B1 9B2 C367 C367 20 C367 20 C367 RSP2H 9E5 9E17 9E14 9E41 9E4 9E16 9E13 9E40 RSP1L 9E33 9E31 RSP2L 9E38 9E37 RSP1H 9E35 9E34 MX1 N9A8 MX2 N9B29 N10B21 N10A33 MX3 N9A6 MX4 N9B31 N10B19 N10A35 MX5 N9A4 MX6 N9B35 N10B17 N10A37 MX7 N9B41 N10A39 MX8 N9B33 N10B15 MX9 N9B39 N10A41 MX10 N9B37 N10B13 MX11 N9A16 MX12 N9A10 N10B11 MX13 N9A14 N10B5 MX14 N9A12 N10B9 MY1 N9A27 N10A19 MY2 N9A29 N10A17 MY3 N9A31 N10A23 MY4 N9A17 N10A21 MY5 N9A19 N10A27 MY6 N9A21 N10A25 MY7 N9A23 N10A31 MY8 N9A25 N10A29 N10B3 1K 0.01 V+20 C371 C367 2K 500 9E44 300 9N5 9N6 9B5 9B6 C367 C367 9E43 0.01 50V 10 1K C367 200pF nG1 1K 9N2 10K 9E73 2K 0.01 1K DGT1.9 20 C367 20 C367 500 300 9N9 9N10 DGT2.10 9E47 9E46 DGT3.11 9E50 9E49 DGT4.12 9E53 9E52 DGT5.13 9E56 9E55 DGT6.14 9E59 9E58 DGT7.15 9E62 9E61 DGT8.16 9E65 9E64 CORENEUTRAL N9B27 Casio AL-1000 Calculator Section: Memory Address Drivers Page: 21 Rendition: 2015 Mar 13 N10B7 Address lines flow through all 4 core planes (only one shown). 200pF nG2 300pF 10N5 nG1 20K 10N15 G1p 20K INHIBIT LINES SENSE LINES 5K V+20 C367 % 15 0.01 50V 10E1 nW1 0.01 130 C367 C371 TDK PT-16I1 130 C367 I1 nS1 nI1 S1 500 10K & 2K 10K 2K 10N8 C371 10NA2 N10A13 N7A38 nMSENSE1 10N7 5K 1 50V 10N1 10NO2 5K C371 V+20 C367 % 15 0.01 50V 10E2 nW2 0.01 130 C367 I2 nI2 130 C367 S2 nS2 500 10K & 2K 10K 2K 10N10 C371 10NA3 N10B35 N7A30 nMSENSE2 10N9 5K 1 50V 10N2 10NO3 5K C371 V+20 C367 % 15 0.01 50V 10E3 nW4 0.01 130 C367 I4 nI4 130 C367 S4 nS4 500 10K & 2K 10K 2K 10N12 C371 10NA4 N10B33 N7A20 nMSENSE4 10N11 5K 1 50V 10N3 10NO4 5K C371 V+20 C367 % 15 10E4 nW8 0.01 130 C367 130 C367 0.01 50V I8 nI8 nS8 2K Casio AL-1000 Calculator Section: Memory Inhibit & Sense Page: 22 Rendition: 2015 Mar 13 10K 10N4 & 2K S8 10K 500 10N14 C371 1 50V 5K 10N13 10NO5 10NA5 N10A15 N7A9 nMSENSE8 DC8 nDC8 DGT1.9 ØD1 ØD9 ØD2 ØD10 ØD3 ØD11 ØD4 ØD12 ØD5 ØD13 ØD6 ØD14 DGT2.10 10 of C284 n1 n2 n4 n8 10K DGT3.11 30K DGT4.12 1 n2 n4 n8 10K 30K n1 2 n4 DGT5.13 10K DGT6.14 30K 100pF A1 1N1 20K SE Q DGT7.15 1 1 2 n4 1D1 RE nQ n1 SE Q 2 100pF A2 1N2 20K 1D2 RE nQ n2 SE Q 4 100pF A4 1N4 20K 1D4 RE nQ n4 SE Q 8 100pF A8 1N8 20K G2 nQ ØD7 30K DGT8.16 ØD15+16 ØD8 n1 n2 4 10K 1 n2 4 10K V+200 30K DIGIT 15/16 10K 100pF n8 1 2 4 1K 5K 2K C371 0.05 250V A549A 50K 15K ØD15+16 2 8 4 8 DP=0 nPWENB Rendition: 2015 Mar 13 V+80 100K 4K ØD14 50K NEC 1 3 5 7 9 LD 866 0 2 4 6 8 . 10K 30K 10K 30K V+80 V+200 $DDP1 500K V+80 V+80 C284 $DDP2 $DDP3 N1A25 N2A43 DPa 2N7 2N8 N2B1 N1A23 DPb 10K 15K 100K — (negative) RETURN V+80 N1A5 Note: output resistor on this OR gate is 50K. 100K C284 FNEG Casio AL-1000 Calculator A549A 0.05 250V 30K 1 n2 n4 8 Section: Display Page: 23 2K C371 15K 30K 5K 1K V+80 10K n1 n2 n4 8 DIGITS 13 to 1 (LSD) 300 30K n1 2 4 DIGIT 14 (MSD) 50K 1D8 RE 10K 20K 50K 100K C284 PC PRENB N8A10 N1A7 20K bwn-red RETURN 50K V -6 Reg calc -20 Reg calc Rt Rb I V P(Rb) I R 202 0.00625 P 6 120 456 0.010 0.049 +200 use 20 121 1815 0.010 0.194 +20 use 20.2 0.245 1.26 4.95 +12 use 12 0.645 7.74 -6 Reg calc 5.81612 121 442 0.010 0.047 -6 use 5.8 0.0286 0.17 -20 Reg calc 19.9483 121 1810 0.010 0.193 +20 power reg 4.8 0.245 1.18 8.11983 121 665 0.010 0.071 +12 power reg 4 0.645 2.58 10.2 0.0286 –6 power reg -6 Reg calc 5.96891 121 592 0.008 0.041 0.005 0.102 0.29 18.17 2000 -20 Reg calc 19.6901 121 3570 +200V bleed 200 +80 divider 80.0 0.0002 820000 0.05 36.0 0.0013 27000 0.05 44.0 0.0013 33000 0.06 114.3 0.006 20000 0.65 42.9 0.006 7500 0.24 42.9 0.006 7500 0.24 3570 +200V divider 200.0 V+200 REPLACEMENT POWER SUPPLY 4 of 1N4006 5 Transformer from dismantled HP 2912A reed scanner 154 VAC F8 6 F7 10 350V R7 820K 8 POWER 0.25 AMP. F6 1 100V R6 brown +80V R5 blue +45V mA 202 6.25 N1B39 V+80 79.8 -1.1 V+50 44.2 0.23 V+20 20.2 245 V+12 12 645 5.82 28.6 V-6 V+blu 33K 0.0078 1KV N2A44 V+20 N9A43 3 117 VAC V+80 27K 1 Volts V+200 N1A43 orange +200V V+80 1N4006 7 47 VAC Supply 0.1 AMP F9 2 0.0078 1KV V+20 F5 V+20 12 IN 8 VAC 13 F4 LM317 OUT 1000 16V R4 120 V+20 N3A44 green +20V N8A44 V+20 N9A44 V+20 N10A43 1800 0.5W 4 F3 10 N9A1 16 VAC 11 F1 16 VAC 14 IN 2200 35V 9 LM340K -12 OUT R3 yellow +12V R2 black GND F2 N1A1 N2A2 N3A2 N4A2 N5A2 N6A2 N7A2 N8A2 N9A2 N10A1 N1B43 N2B44 N3B43 N4B43 N5B43 N6B43 N7B43 N8B43 N9B43 N10B43 N2B43 456 (442) 100 35V Casio AL-1000 Calculator Section: Power Supply Page: 24 Rendition: 2015 Mar 13 IN LM337 120 OUT 1 10V R1 violet –6V N6A26 N1B1 N2B2 N3B1 N4B1 N5B1 N6B1 N7B1 N8B1 25 25V 25 25V 25 25V 25 25V 25 25V 25 25V 25 25V 25 25V V+20 470pF 0.001 25 25V N10B1 25 25V V+20 25 25V 25 25V V+20 25 25V N1A 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 V+12 FNEG RETLAMP RETURN nMB8 MDY6 MDY7 MDY5 MDY4 DPb DPa MDY1 MDY2 MDY3 MDY8 MB8 DP=0 nPWENB V+200 N2A G2 DGT1 nKR1 nRND8 nRND7 nRND0 nKN8 nKN1 nKN4 nKN2 nRND6 nK1 nK2 nK3 nK4 nK5 nK6 nK7 nK8 nK9 DPa N1B 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 V–6 A8 A4 A1 A2 G2 V+80 GND 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N3A V+12 n(TEND+PORC) TEND S1 TB nTD PORC nS1 n(AC+PORC) S1+PORC nKR2 nKR4 nRND1 nRND2 nRND3 nRND4 nRND5 nKR8 nK0 nKADD V+blu N2B DPb nKSUB nKM1 nKM2 nKM3 nKM4 nKMUL nKDIV nKAC nKKC nKSQR nW1 POR nW2 nW4 nW8 U=13 ST3 DP=0 ARCYINJ3 DP=7+15 GND 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 Casio AL-1000 Calculator Section: Connectors 1-5 Page: 25 Rendition: 2015 Mar 13 V–6 nKDP nKCHS nKNP nKF8 nKF1 nKF4 nKF2 nKFP PORAC nPREXEC U=STPEND nPRENB (not used) DPINCA DPINCB ST GND UALIGN FNEGSET U=13 U=CLRENT U=ALLCLR U=END U=MEM U=STPEND nKDP nPB FDP FN S2 M4ACC nW4 nW2 UNUL nDGT1 M1ACC M1MEM M2ACC 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N4A V+12 UADDSUB FNEG F54 n(AC+PORC) ST9 nKCHS TSNML nSTEND PRENB n(TEND+PORC) nTD nKF8 PORAC nW8 nULDINSTR nKF4 nKF2 nKF1 nW1 V+20 nSTEND FNEGSET nMEMACC A8A4 n(TEND+PORC) A1 ST19 U=ALLCLR ST21 U=MEMGET U=CLRENT ST16 ST11 ST0 TB ST3 ST20 - 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N5A V+12 S1 nS2 U=MEMACC DGT1 ST7 U=DIV UMAS ST5 ST24 nW0 UALIGN F54 UADDSUB W0 ST26 UNUL ST4 C U=SQRRT ST9 DP=7+15 nSNXT1 nSNXT2 nSNXT3 nST16 ST2DGT nSTDGTINC UMAS UDAS U=MEMGET nDGT1 FNEG TSNML2 ST11 ST20 ST5 ST26 ST14 ST16 - 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 V+12 S1+PORC nS3 STSHIFT nSTFLIPRADP nSTDGTDOWN nSTALNOMEM nSTDPONLY U=ALLCLR ST7 ST24 ST13 ST19 ST4 ST21 ST22 ST25 ST0 ST28 nST28 - N3B N4B N5B 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 V–6 U=MEM4 DP=7+15 S1 U=SQRRT U=MEM3 UMAS UDAS UFCTREQST M2MEM U=MEM1 M3ACC M3MEM M4MEM U=DIV U=MUL nU=MEM2 nMEMACC U=MEMGET U=MEMSAVE U=MEMACC GND Note: Bold-faced expressions are signal source. V–6 UDAS ST1 ST22 U=13 nC U=MEMSAVE U=MUL ST28 ST6+10 ST25 ST13 ST14 nSNXT2 nSNXT4 DP=0 nSNXT3 nSNXT1 nSNXT5 GND V–6 ST9 ST1 ST3 DGT16 U=13 DGTCLK nSNXT4 nSTYFIRST U=SQRRT nST3 DPINCA nSNXT5 GR DP=0 nGR CITSUB nSTM2FORY nBLDFIVE ST6+10 n(TEND+PORC) GND N6A nS1 S1 nS2 nS3 nG1 nG2 G2 nGR CARNOA ARCYENB TSNML2 DPINCB nALDMINH nSTALNOMEM nST16 GR TB nSTEND nTD TC - 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N7A V+12 nDGT1 POR n(AC+PORC) nSTDPONLY UFCTREQST TEND S2 PORAC PORC G1 GND FDP STSHIFT nST28 DGT1 CITSUB ARCYINJ2 nCARSUB CARNOBC nALDMENB A8 (nB8) ALDDP nMSENSE8 A4 A2 ARCYINJ3 (nA1) A1 nCARSUB A8A4 ARCYENB CARNOBC - 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 N8A 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 V+12 nKDP ACLR BCLR ALDKNCLK nKN8 nALDMENB nKR8 nKN4 nMSENSE4 nBLDMENB nKR4 ARCYINJ1 nKN2 nMSENSE2 nKR2 nKN1 nMSENSE1 BLDKRCLK nBLDFIVE nKR1 U=END n(AC+PORC) nPRSEL2 nPWSEL2 nPA nPWENB TC DGTCLK ALDDP nMB8 MB8 U=MEM1 nTSIDLE RSYH RSYL DGT1 nDGT1 DGT2 DGT8.16 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N9A V+12 nULDINSTR nALDMINH ARCYINJ1 RETLAMP nPB DP=0 nTD W0 G1 QT PRENB nSTYFIRST S2 U=MEM nSTM2FORY nU=MEM2 nSTDGTDOWN U=MEM3 U=MEM4 RSM2L V+20 (V+12) RSP2H RSP2L RSP1H RSP1L RSM4L RSM3L RSM2H MY4 MY5 MY6 MY7 MY8 MY1 MY2 MY3 (V+20) 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 N10A V+12 MX5 MX3 MX1 MX12 MX14 MX13 MX11 nG2 DGT8.16 DGT7.15 DGT6.14 DGT5.13 V+20 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 V+12 nW0 nG2 W0 nMSENSE1 nMSENSE8 MY2 MY1 MY4 MY3 MY6 MY5 MY8 MY7 MX1 MX3 MX5 MX7 MX9 V+20 N6B N7B N8B N9B N10B 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 V–6 nBLDMENB ACLR BCLR nST3 TSNML nPREXEC nSTFLIPRADP nSTDGTINC DGTCLK QT CYCLK ALDKNCLK nTSIDLE ST2DGT PRENB ST FN DGT2 nKNP nKFP GND Casio AL-1000 Calculator Section: Connectors 6-10 Page: 26 Rendition: 2015 Mar 13 V–6 CARNOA nTRUNC ST16 DGT2 F54 ARCYINJ2 nW1 DGT16 - (pre-norm carry) ST3 UMAS S1 CYCLK nW2 nPA nDGT1 nW4 nW8 C nC GND Note: Bold-faced expressions are signal source. V–6 RSM2H RSM3L RSP2L RSP2H RSP1L RSP1H RSM4L RSM1H RSM1L RSXH RSXL DGT7.15 DGT6.14 DGT3.11 DGT2.10 DGT1.9 DGT4.12 DGT5.13 DGT16 S1 GND RSM2L RSM1H RSM1L RSYL RSYH RSXH RSXL DGT4.12 DGT3.11 DGT2.10 DGT1.9 nG1 CORENEUTRAL MX2 MX4 MX8 MX6 MX10 MX9 MX7 GND V–6 MX11 MX13 CORENEUTRAL MX14 MX12 MX10 MX8 MX6 MX4 MX2 nW1 nW8 nW4 nW2 nG1 nMSENSE4 nMSENSE2 F54 ST26 BLDKRCLK GND