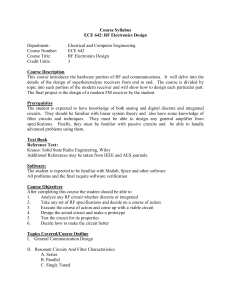

Building Blocks of Digital Circuits Storage Elements

advertisement

So, Why Binary? Electronic computers represent information as voltage levels To make computer hardware simple and reliable, computers represent information in binary form Building Blocks of Digital Circuits » example: voltages greater than 3V are interpreted as representing one value (called “1”), voltages less than 2V are interpreted as representing another value (called “0”) Digital circuits, binary logic and noise flip flops and latches Decoders and multiplexors Memory and Lookup tables (LUTs) Field Programmable Gate Arrays Tristate buffers In Gates, Computers (like all electronics) are affected by noise Noise margin is amount of noise that a system can tolerate and still correctly identify a logic high or low » smaller power supply voltages lead to smaller noise margins » but also improve performance and reduce power requirements AND Gate X Y X OR Gate Y XOR Gate Inverter 5v High Logic 3v 1v Undefined Low 0v noise margin noise margin 1V 3V Storage Elements is basic storage element » when C=1, Q=D (and Q’=D’) » when C=0, Q and Q’ don’t change D flip flop stores value at D input when clock rises » most widely used storage element for digital circuits » can be implemented with two latches If D input of latch changes as C goes from 1 to 0, output value is uncertain X Timing Diagram X Y X+Y X’Y+XY’ X’ XY X+Y X Y X’ gates “compute” elementary binary functions » output of an AND gate is “1” when both of its inputs are “1”, otherwise the output is zero » similarly for OR gate, XOR gate and inverter High Timing diagram shows how output values change over time as input values change ‹#› D-latch X Y XY 4v Undefined 2v Low ‹#› Basic Logic Gates » various sources (nearby signal changes, thermal vibrations of molecules in semiconductor materials, . . . ) » in computers, noise can cause binary signals to be misinterpreted In practice, this is rarely done » requires more complex circuits » circuits are more susceptible to noise, hence less reliable Noise in Computer Systems principle, could use more voltage levels » example: 0 to .75V represents “0”, 1 to 1.75V represents “1”, 2 to 2.75V represents “2”, and so forth ‹#› Review Questions D Q C Q D Q >C Q D C Q » similarly for flip flop » output may oscillate or remain at intermediate value (metastability) » to avoid metastability, keep D stable when C is changing Explain why a circuit that uses three voltage levels is more susceptible to noise than a circuit that uses two voltage levels (assuming the same maximum voltage in both cases). Draw a circuit that implements the exclusive-or function using just AND, OR gates and inverters. Can you do it with just AND gates and inverters (hint: consider DeMorgan’s Rule)? What does it mean for a flip flop to be metastable? What’s the maximum amount of time that a flip flop can be metastable? D Q C Q ‹#› ‹#› 1 Decoders and Muxes Memory 2→4 decoder 1→2 decoder A k→2k decoder converts a k bit binary input to a 1 on one of 2k outputs X0 X0 X1 X1 » can construct larger decoders using by combining two smaller ones » useful for selecting one of a number of cases based on a numerical value A0 X2 X3 A0 A multiplexor selects connects one of its data inputs to its output » can also construct larger muxes from smaller ones, or using decoders » useful for selecting one of several stored values A1 4-mux D0 D1 0 D2 D3 0 1 0 X 1 enable Implements array of n numbered storage locations read/write data_in » index for a location is called its address » each location stores a word with w bits data_out address 00 01 02 . . . FE FF Operation » when enable and read/write are high, value stored in location specified by address appears at data_out » when enable is high and read/write is low, value on data_in replaces value in location specified by address » may operate synchronously, or asynchronously Can be implemented using latches or flip flops, but usually, uses specialized, higher density circuits 1 A0 A1 ‹#› Lookup Tables ‹#› How Many LUTs Does it Take? Digital logic is often implemented using devices called Field Programmable Gate Arrays (FPGA) » configurable device that can implement many different circuits » implemented using “programmable” logic elements and wires A Lookup Table (LUT) can be configured for any logic function with specified number of inputs (typically 4) U V of circuit implemented with LUTs: F X G Y Z U V X Y A B C D Z A B C D using configurable logic circuits, it’s useful to have way to estimate required number of LUTs For circuit with n outputs, need at least n LUTs » if using LUT4s & all functions have ≤4 inputs, n is enough » newest FPGAs use LUT6s, so for functions with up to 6 inputs, one LUT6 is enough » can view LUT as hardware implementation of truth table Example When In LUT4 a circuit with k LUT4s, m inputs and n outputs with k>n, k–n LUT outputs connect to LUT inputs F » so, m+(k–n)≤4k which means k≥(m–n)/3 » so, a 4-mux requires at least (6–1)/3=2 LUT4s and an 8-mux requires at least (11–1)/3=4 LUT4s A’BCD’ LUT4 ABC’+B’+CD G • in practice, need three LUT4s for 4-mux, seven for 8-mux ‹#› Xilinx FPGA Organization ‹#› Xilinx Configurable Logic Block switch matrix wire segments configurable logic blocks (CLB) IO blocks (IOB) main function generators G1 G2 G3 G4 configuration bits CLK EC clock edge select S/R Y S/R C set/reset control LUT4 D PRE >C DIN YQ EC CLR H1 CLBs can be connected to “passing” wires segments connected by switch matrix Long wire segments used to connect distant CLBs Configuration information stored in SRAM bits that are loaded when power turns on ‹#› Wire F1 F2 F3 F4 LUT3 clock enable control 1 D LUT4 PRE >C XQ EC CLR main function generators 1 S/R C flip flop X ‹#› 2 Tri-State Buffers Exercises 1. Consider the circuit shown below, consisting of a D-latch and a positiveedge-triggered D flip flop. control A D Q Q Register 2 LD different components to take turns using shared output wire(s) (often called a bus) Also allows wire(s) to be used for both input and output ‹#› 20 40 3. Such a circuit could be implemented with 4 LUTs. This follows from the equation on page 11. 60 80 100 clk A X Y 2. An 8:1 mux can be implemented with 7 2:1 muxes. A 16:1 mux can be implemented with 15. 4. A circuit that implements a 12 input AND function can be implemented with 4 LUTs. Configure each LUT as a 4 input AND and connect the outputs of three to the inputs of the fourth LUT. This leaves one spare input. The function can be implemented using the 4 LUT circuit shown below. F G H I J K L A B C D Y 3. Consider a circuit with 12 inputs and a single output. What is the minimum number of 4 input LUTs that would be required to implement this circuit? Give an example of a 12 input circuit that could be implemented with this number of LUTs. Give a circuit using LUTs that implements the expression shown below. Suppose we drive the circuit with a 50 (A+ B+C+D+E)(F+G+H+I+J)(K+L) MHz clock, with positive transitions at 20 ns, 40 ns, 60 ns and so forth. Now, Use as few LUTs as you can. How does the number of LUTs compare to the suppose input A starts low, then goes minimum number required for a 12 input high at 25 ns, then low at 55 ns and high at 85 ns. function. Draw a timing diagram covering the 4. Show how you can implement a 4 input time period 0 to 100 ns, showing the mux using a decoder and four tri-state clock and A inputs, plus outputs X and buffers. Y. ‹#› Allows 0 >C clk » when control input is high, output equals input » when control input is low, output is disconnected from input – called high impedance state 1. D Q C tri-state buffer has a data input and a control input Solutions X D Q Register 3 LD LD Register 1 D Q D data_out data_in A 2. How many 2:1 multiplexors are needed to implement an 8:1 multiplexor. How many are needed to implement a 16:1 multiplexor? select 2 24 decoder 0 1 2 3 D0 D1 D2 D3 out (F+G+H+I+J) (K+L) E ‹#› ‹#› 3