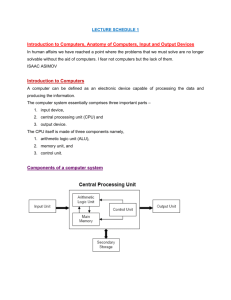

System Organization Chapter Three

advertisement