A 10-bit 50-MS/s Pipelined ADC With Opamp Current Reuse

advertisement

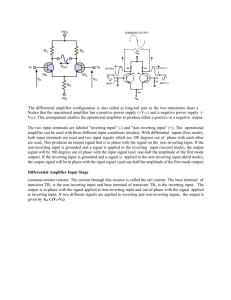

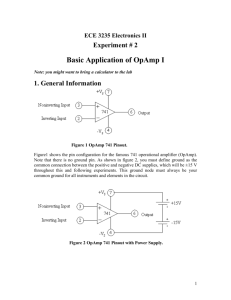

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 475 A 10-bit 50-MS/s Pipelined ADC With Opamp Current Reuse Seung-Tak Ryu, Member, IEEE, Bang-Sup Song, Fellow, IEEE, and Kantilal Bacrania, Member, IEEE Abstract—Power and area saving concepts such as operational amplifier (opamp) bias current reuse and capacitive level shifting are used to lower the analog power of a 10-bit pipelined analog-to-digital converter (ADC) to 220 W/MHz. Since a dual-input bias current reusing opamp performs as two opamps, the opamp summing nodes can be reset in every clock cycle. By using only N-channel MOS (NMOS) input stages, the capacitive level shifter simplifies the gain-boosting amplifier design and enables fast opamp settling with low power-consumption. The prototype achieves 9.2/8.8 effective number of bits (ENOB) for 1- and 20-MHz inputs at 50 MS/s. The ADC works within the temperature range of 0 to 85 C and the supply voltage from 1.62 to 1.96 V with little measured loss in the ENOB. The chip consumes 18 mW (11 mW for the analog portion of the ADC and 7 mW for the rest including buffers) at 1.8 V, and the active area 1 3 mm2 using a 0.18- m complementary metal occupies 1 1 oxide semiconductor (CMOS) process. Index Terms—Capacitor-array multiplying digital-to-analog converter (MDAC), digital-to-analog converter (DAC), low-power technique, opamp-sharing, pipelined analog-to-digital converter (ADC), switched-opamp. I. INTRODUCTION A MONG ADC architectures, pipelined ADCs are most suitable for medium/high speed and resolution applications. Resolution up to 14 bits has been reported without calibration, and the conversion rate of 1 GS/s with 11-bit resolution has been achieved with time interleaving [1]–[4]. Two key elements that enable this wide range of performance are digital error correction with redundancy [1] and capacitor-array multiplying digital-to-analog converter (MDAC) [5]. The accuracy of the residue generated by an MDAC depends on the settling accuracy of the operational amplifier (opamp) and the capacitor matching in the reconstruction DAC. The power consumed in wideband opamps often limits the total ADC power, especially when stringent linearity and resolution requirements have to be met. Various approaches have been proposed in the literature with the aim of reducing the power consumption of the pipelined ADCs. Removing the input sample and hold (S/H) by sampling the input directly on the first MDAC allows some power reduction [6], [7]. The use of open-loop amplifiers [8] or making comparator-based systems without using opamps Manuscript received May 24, 2006; revised November 1, 2006. S.-T. Ryu was with the Department of Electrical and Computer Engineering, University of California at San Diego. He is now with Samsung Electronics, Gyeonggi-do, Yongin 449-711, Korea.. B.-S. Song is with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA (e-mail: song@ece.ucsd.edu). K. Bacrania is with Conexant, Palm Bay, FL 32905 USA. Digital Object Identifier 10.1109/JSSC.2006.891718 [9] can also lower power consumption. New ADC architectures lead to power-efficient ADCs, but creative design solutions can significantly contribute to the power reduction. Most low-power pipelined ADCs achieving good figures of merit (FOM) save the power consumed in opamps by operating them dynamically. Such power-saving techniques try to either share an opamp between stages or switch opamps by turning off power during clock phases in which the opamps are inactive [10]–[17]. As a result, the opamp summing nodes are never reset in the former, and there is a turn-on delay in the latter. This work demonstrates a power-efficient pipelined ADC architecture in which the opamp bias current is reused. The proposed scheme is also free from the summing node reset and turn-on delay problems. Furthermore, the opamp input capacitance stays constant since the two input differential pairs are always operated in saturation. The use of capacitive level shifting allows NMOS transistors to be used as the input devices for all cascode gain-boosting stages, thereby achieving fast settling with low power consumption. Power consumption in pipelined ADCs and previous opamp power-saving techniques are reviewed in Section II. The proposed bias-current reuse concept and an example highlighting some practical design considerations are covered in Section III. Details of the system architecture and circuit design are described in Section IV. II. PREVIOUS OPAMP POWER-SAVING TECHNIQUES A. Pipelined ADC Architecture The pipelined ADC is made of cascaded similarly structured stages separated by S/Hs as shown in Fig. 1. Each pipelined stage generates a coarse ADC output and a reconstructed residue signal for the later stages. The S/H enables the concurrent operation of the pipelined stages for a high throughput rate. The capacitor-array MDAC performs all of the above functions exbits have to be cept for that of the coarse ADC. Assume that resolved in the th pipelined stage. The output residue is generated after the coarse ADC generates an -bit digital code. The residue is defined as the unquantized portion of the signal obtained by subtracting the output of the reconstruction , which DAC from the signal. The residue is amplified by is half of the ideal gain. This allows the other half of the range to be used for digital error correction. The full signal range is ranges using comparators. In gendivided into of a stage expressed in terms of eral, the residue output the stage resolution is 0018-9200/$25.00 © 2007 IEEE Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. (1) 476 Fig. 1. Conventional pipelined ADC architecture. where , and , depending on the coarse ADC result. This residue output is further quantized in finer steps by the later stages in the pipeline. Digital error correction reduces the offset requirement of the opamps and comparators and makes it possible to use open-loop bottom plate sampling. As a result, opamps are idling during the sampling phase other than being reset. Therefore, it is possible to save the opamp power during the sampling phase in two different ways. One way is by sharing the opamp with another stage that is in the amplifying phase, and the other is by switching the opamp power off during the sampling phase. B. Dynamic Power-Saving Techniques The opamp sharing technique refers to the use of one opamp with a 100% duty cycle for two pipelined stages operating out of phase. This is done by disconnecting the summing node from the sampling capacitors during the sampling phase when the opamp is not used, and by attaching it to another stage, which is in the amplifying phase [10]. One opamp serves as the residue amplifier for two different stages during two different clock phases. Therefore, the number of opamps is reduced by half, directly resulting in both power and area savings. The drawback in this method is that the summing node is never reset since the opamp is active in both phases. It also implies that the input-referred offset is affected by the value of the previous residue and by 1/f noise. This can be overcome by using a two-stage opamp in which the high-power second stage is shared by two pipelined stages, but the two first-stage preamplifiers powered on all the time provide two input summing nodes [11]. Each summing node can be reset in such a scheme during the sampling phase. Such a partial opamp sharing scheme requires the same number of preamplifiers as in a conventional design and has no significant power and area advantage. The feedback-signal polarity-inversion method was proposed recently to cancel the opamp offset resulting from the value of the previous sample [12]. It has been predicted that the offset can be reduced by as much as 1/3 in the 1.5-bit MDAC case, but the IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 effect of the offset reduction becomes less significant as the resolved number of bits per stage increases. The dummy switch and timing control, tailored only for the passive capacitor-error averaging (PCEA) method, uses a parasitic path with an opposite polarity signal to reduce the summing node coupling effect [13]. Power saving is achieved in the switched-opamp technique by turning off the opamp during the sampling phase [15]. The summing node can be reset in every clock cycle since each stage has an opamp of its own. This method is particularly useful in low-voltage systems where it is not feasible to make floating signal switches. Turning off the opamp power is equivalent to disconnecting the signal. A drawback in this technique is the additional turn-on delay that has to be accounted for when the opamp is switched back on from the power-saving off state. Note that the opamp input capacitance changes when the input pair devices are turned on and off. So does the feedback factor, and the residue amplifier gain is affected. It is not desirable because the charge sampled on the sampling capacitor, i.e., input signal, changes when the opamp is turned on. The error due to the change of the input capacitance is avoided with a little overhead by using extra preamplifiers that are kept powered up all the time but by switching off the second stage [16]. This partially switched-opamp method allows no delay associated with powering up the first stage, but a turn-on time of the second stage still matters. This can be viewed as a case where the trade-off is made between the power consumed and the speed of operation. The features and issues of various opamp-sharing and switched-opamp methods are summarized in Table I. In short, the opamp sharing method has the summing node reset problem, while the switched opamp scheme suffers from an additional turn-on delay. The proposed opamp current reuse technique solves these problems without incurring an additional power and area overhead. III. OPAMP BIAS CURRENT REUSE ARCHITECTURE A. Opamp With Bias Current Reuse The summing-node reset problem can be avoided by combining features of the switched-opamp and opamp-sharing concepts. The opamp-sharing system can be modified using an additional preamplifier that is switched in so that two separate summing nodes can be used for two inputs as shown in Fig. 2. on the left-hand side is a pipelined part The preamplifier of a stage which is shown to be in its sampling phase, while the on the right hand side is a part of a pipelined preamplifier stage which is amplifying the residue. The preamplifier can be turned off and the summing node can be reset during this phase since it is not in the signal path. This scheme, however, still suffers from the problems associated with the turn-on delay as in the switched-opamp case. In addition, there is an area overhead for the additional preamplifier. This concept of switching preamplifiers is simplified as shown in Fig. 3, where the two preamplifiers in Fig. 2 are merged into a single bias branch allowing the two amplifiers to share the same bias current resulting in both area and power savings. The two switches are turned on and off alternately using non-overlapping clocks, and . Note that this amplifier can be used as a single-stage Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. RYU et al.: A 10-bit 50-MS/s PIPELINED ADC WITH OPAMP CURRENT REUSE 477 TABLE I COMPARISON OF POWER-SAVING TECHNIQUES Fig. 2. Switching preamps in a modified opamp-sharing system. Fig. 3. Modification for area saving with two preamplifier inputs switched. opamp by itself. However, this does not solve the switching transient problem, which results in the change of the input capacitance when the bias current is turned on through the active input transistors. A modified version of this scheme is shown in Fig. 4 in which the summing node is reset with no additional turn-on delay. A P-channel MOS (PMOS) input pair is used instead of adding an extra NMOS input pair. This PMOS input pair is stacked in the same current branch with the NMOS input pair allowing the bias current to be reused. The switches are moved to the gate of the input devices, thus connecting the or to gate to the common-mode bias voltages instead of switching the bias the signal paths current. Connecting the inactive pair of transistors to the bias voltage allows these to act like an active load to the other. For are closed and switches example, during , switches are opened. Then, the PMOS pair becomes the active load to the NMOS differential pair. Similarly, during , the roles of the NMOS and PMOS pairs are reversed with switches in the off position and in the on position. Note that these switches disconnecting the opamp inputs are not necessary because the opamp input nodes are capacitive and can be initialized to any input common-mode bias level. Therefore, the summing node can be reset in every clock cycle since there are two separate input differential pairs that operate in two different clock phases. The device role switching at every clock cycle also helps to avoid the dynamic problems observed while switching opamps. This circuit is not affected by the turn-on delay problem observed in the switched-opamp case, and the input capacitance stays constant since all transistors are operated in saturation. A disadvantage of this scheme is that an additional tail current source has to be stacked in the branch reducing the signal swing range slightly. Table II compares three low-power pipelined ADC architectures. Stage scaling Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. 478 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 Fig. 4. Opamp with bias current reuse. TABLE II LOW-POWER PIPELINED ADC ARCHITECTURES No power scaling is applied. Except for Yu ISSCC96 [11] is not considered to keep the comparison simple. The scaling effect on the power saving is discussed in the Appendix. B. Summing Node Isolation Issue Several design issues are considered in Fig. 5 using a 1.5-bit MDAC example. The NMOS-input MDAC is sampling while the PMOS-input MDAC is amplifying. Ideally, the summing node of the NMOS-input MDAC should stay at the input common-mode bias during the sampling phase. However, the summing node reset is delayed due to the non-zero RC time constant resulting from the sampling capacitance and the sampling switch resistance. This switching operation is common in all dynamic circuit techniques, and different from the turn-on delay or variable input capacitance problems found in the opamp-switching case. The summing node variation is amplified while being reset by the NMOS differential pair if this time constant is not sufficiently short as compared to the sampling period. This affects the output settling behavior of the residue of the P-input MDAC. This gain from the gate of the active load to the amplifier output is estimated as (2) where is the trans-conductance of the NMOS input tranand is that of the PMOS input transistor . sistor is the input parasitic capacitance of the PMOS-input deis the feedback factor of the P-input MDAC loop comvice. , , posed of PMOS-input transistor and the capacitors . Unless the sampling node is reset fast for the given and sampling rate, the finite time constant effect can be avoided by separating the summing nodes from the sampling capacitors by and as explained in Fig. 4. re-inserting series switches These series switches prevent the residue output-settling from Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. RYU et al.: A 10-bit 50-MS/s PIPELINED ADC WITH OPAMP CURRENT REUSE 479 Fig. 5. Interference from the sampling side. Fig. 6. Block diagram of a 10-bit pipelined ADC with opamp bias current reuse. being delayed by the incomplete input common-mode reset of the active load. IV. CMOS IMPLEMENTATION A. Pipelined ADC Using Current-Reusing Opamp Fig. 6 shows the prototype 10-bit ADC system. It is composed of an input S/H, five sub-ADCs, and 4 MDAC stages. Two current-reusing opamps make four MDAC stages. Each stage resolves 3 bits (2.8 effective bits). Each current-reusing opamp has NMOS and PMOS complementary differential inputs. MDAC1 and MDAC4 share the same bias current, and so do MDAC2 and MDAC3. The opamps with NMOS inputs are used for the most significant bit (MSB) stages while those with PMOS inputs are used for the least significant bit (LSB) stages. This is because the MSB stages require a higher gain and a wider bandwidth than the LSB stages. This is also a desirable configuration from ratio of the input device to a noise point of view because the requirethe active load affects the input referred noise. The ment for the PMOS input device in MDAC4 is the least stringent among the stages, and its effect on MDAC1 is not significant. The power consumption of the LSB stages is saved in this implementation compared to the conventional pipeline design. Each pipelined stage is based on a standard tri-level 3-bit thermometer-coded capacitor-array MDAC [18]. Simplified schematic (without the sampling switches) of the MDAC during the amplification phase and the residue plot are shown in Fig. 7. Six arrows indicate the position of the thresholds of the six comparators. The tri-level thermometer code indicates the connection of each of the three capacitors to the , 0, to provide seven DAC three reference levels levels. Fig. 8 shows the operation of the 3-bit MDAC with the opamp bias current reuse scheme in the prototype. Although it is fully differential, the MDAC is drawn on the left side of the opamp, and the common mode feedback is on the right side. The summing node isolation feature is added to the normal MDAC as explained in Fig. 4. The switched-capacitor common-mode feedback [19] still works for this structure because the charge at the gate of the tail current source depends on the output common-mode voltage. The NMOS-input MDAC samples the input signal with both opamp input terminals connected to the input common-mode bias , which is of the NMOS tail current plus of the NMOS input transistor above the Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. 480 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 Fig. 7. Tri-level 3-bit MDAC and its residue output. Fig. 8. MDAC operation in both phases with simplified opamp schematic. negative supply. Similarly, is set to of the PMOS tail current plus of the PMOS input transistor below the positive supply. The NMOS-input MDAC amplifies the residue, during the odd phase , for the input sampled during the previous phase while the sampling capacitors associated with the PMOS-input MDAC samples its new input. This constant gate voltage enables the PMOS input pair to be the active load to the NMOS differential pair. Unlikely the conventional opamp design, the opamp used here has two tail currents for both NMOS and PMOS differential pairs. In most low-power designs, transistor is small, and one extra drop does not reduce the output signal swing significantly. B. Opamp Design Further power reduction is achieved in the prototype with a power-efficient opamp design. The proposed opamp with bias current reuse is shown in Fig. 9. A gain-boosted telescopic opamp with capacitive common-mode feedback has been chosen as the basic topology. A capacitive level shifter [20] is also used to connect the NMOS boosting amplifier to the main amplifier. The advantage of this capacitive level shifting is that a single-ended NMOS-input amplifier can be used for gain-boosting both NMOS and PMOS cascode devices. Typically, the bias constraint forces the boost amplifier to be a folded-cascode structure, which also consumes more power if a PMOS input device is used [21]. The operating principle of this capacitive level shifter is similar to that of the switched capacitor common-mode feedback. Fig. 10 explains the capacitive level-shifting concept in details. One terminal of is connected to , and the other to the capacitor during , where is the desired input bias voltage of the in this figure. is the source boost amplifier, which is Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. RYU et al.: A 10-bit 50-MS/s PIPELINED ADC WITH OPAMP CURRENT REUSE 481 Fig. 9. Opamp with both N and P inputs with bias current reuse. Fig. 10. Capacitive level shifter for boost amplifier. bias voltage of the cascode transistor . refreshes by can be charged charge redistribution during phase so that to the required level shifting voltage, . Due to the , the input of the gain boost capacitive level shifting thru , can have independent amplifier, which is the gate node of DC bias voltage from that of the source node of the cascode . transistor There are a few things to consider in the capacitive level shifter design. The parasitic input capacitance of the gain-boost amplifier forms a capacitive attenuator with capacitor . Another concern is the charge loss in due to the signal swing. Because of the finite gain of the boost amplifier, the gate voltage changes slightly as the opamp swings. of the input transistor and leads This results in the change of the stored charge on . Assume that both the inputs to to a change in the voltage the NMOS and PMOS input pairs in the opamp shown in Fig. 9 are zero and all node voltages are set to the normal bias condi. changes by tions with during clock phase , which in turn causes the cascode node to be regulated by the negative feedback. The charge voltage injected into affects , and is estimated to be Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. (3) 482 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 Fig. 13. Measured FFT of 1/20-MHz tones sampled at 50 MHz. shared opamp needs to swing twice as much compared to the one that is not shared. The bandwidths required for the residue amplifier to settle within 1/2 LSB error of an -bit resolution, and for the residue amplifier in the conventional MDAC the residue amplifier shared between two stages , are given respectively by Fig. 11. Chip die photo. (5) Fig. 12. Measured DNL and INL. V changes by during , and is connected to Then, the change in the capacitor voltage is given by . where is the sampling period. The non-overlapping time between the two clock phases has been neglected in these equations and the slew effect is not considered. It is clear that the opamp used in the shared-opamp architecture has to settle with an extra bit of resolution accuracy as compared to the opamp used in the conventional architecture with its output reset during the inactive phase. One minor issue to consider is that the change in the output node can be coupled to the summing node, which is being reset. This effect is negligible since the input differential pair is usually cascaded, and is operated in the saturation region. V. EXPERIMENTAL RESULTS (4) is zero or the same as to be independent Ideally, be much larger than , of the signal. This requires that and the boost-amplifier gain be set high so that the change can be neglected. In this design, because the opamp is used for both phases, there is no separate reset clock period for the level shifter except for the refresh (charge redistribution) period. This refresh cannot reset the charge difference in the level shifter capacitors ( ’s), but the opamp output should not be affected by the previous state of any internal nodes. To alleviate this previous signal effect, the boost amplifiers are cascoded for a high gain of over 55 dB. Even though the summing node is reset in this design, the output node is not reset because it is shared between the two signal paths. This is how the opamp-sharing concept works. The Fig. 11 shows the die photo of the prototype ADC fabricated in a 0.18- m CMOS process. The active die area is 1.1 1.3 mm . With 1.8-V supply, the opamp swings 1 V with a 1-V common-mode voltage, and two references are 1.25 and 0.75 V, respectively. Fig. 12 shows the measured differential and integral non-linearity (DNL/INL) are 0.2/ 0.4 LSB, respectively. Fig. 13 shows the fast Fourier transform (FFT) outputs of 1- and 20-MHz tones sampled at 50 MS/s. All the harmonics are well below 70 dB with a 1-MHz input. The second harmonic dominates at about 69 dB with a 20-MHz input. The even harmonics are due to the unbalanced transformer at the input. Fig. 14 shows the ADC dynamic performance with 1-MHz input for different sampling frequencies up to 60 MS/s. Both spurious-free dynamic range (SFDR) and total harmonic distortion (THD) are about 70 dB up to 50 MS/s, and signal-to-noise ratio (SNR) starts to degrade Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. RYU et al.: A 10-bit 50-MS/s PIPELINED ADC WITH OPAMP CURRENT REUSE Fig. 14. SFDR, THD, SNR, and ENOB versus sampling frequency. 483 Fig. 16. SFDR, SNDR, and SNR versus input level. TABLE III SUMMARY OF MEASURED PERFORMANCE Fig. 15. SFDR, THD, SNR, and ENOB versus input frequency. VI. CONCLUSION slightly from 40 MS/s onwards. ENOB stays well above 9 bits up to 50 MS/s. Fig. 15 shows the performance metrics when the ADC is clocked at 50 MS/s and the input signal frequency swept up to 20 MHz. The SFDR and THD stay above 65 dB, and SNR remains better than 55 dB. The prototype exhibits signal-to-noise-and-distortion ratio (SNDR) of 54.6 dB and THD of 67 dB with a 20-MHz input. The ENOB starts from 9.2 bits for a 1-MHz input and drops to 8.8 bits for a 20-MHz input. The prototype exhibits only a minor variation in the ENOB for the temperature range of 0 to 85 C and supply voltages from 1.62 to 1.96 V. The dynamic range (DR) test is performed with a 20-MHz input sampled at 41 MS/s as shown in Fig. 16. Note that the SNDR is very close to the SNR. The measured dynamic range is about 58 dB. The chip consumes 18 mW at 1.8-V supply including digital for the ADC core and output buffers at 50 MS/s. The analog portion consumes 11 mW or 220 W/MHz. The figure of merit (FOM) of this 10-bit ADC including output buffers is 0.8 pJ/step. The measured performance is summarized in Table III. An opamp architecture with bias current reuse has been proposed as an alternative to opamp sharing and switched opamp schemes for low-power pipelined ADCs. Here two functionally distinct opamps are stacked in a single bias branch instead of sharing an opamp between two stages to be used during both clock phases or by turning off an unused input stage. The proposed scheme does not suffer from the summing-node reset problem observed in conventional opamp sharing schemes or the turn-on delay problem observed in switched opamp schemes without adding power and area overhead. Making two real input paths in a single-stage opamp reduces the number of opamps by half. A capacitively-coupled NMOS-input boost amplifier is used to regulate both NMOS and PMOS cascode devices resulting in further power reduction. APPENDIX OPAMP POWER SCALING EFFECT IN PIPELINED ADCS The power reduction at the system level can be compared as shown in Fig. 17 taking into account power scaling. A fourstage pipelined ADC without S/H is used as an example. The Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. 484 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 3, MARCH 2007 Fig. 17. Effect of scaling on power consumption. power consumed by the first stage is normalized to 1. Each subsequent stage is scaled by a stage-scaling factor , which is less than 1. Note that this comparison only considers the power consumed by the opamps. The total power consumption of the . The pipelined ADC is in the conventional power consumption is reduced to opamp-sharing technique since only odd stages are used. The switched-opamp method does not reduce the total number of pipelined stages but its operational duty cycle is half of that of a conventional pipelined ADC. This results in a power consump. tion given by Only the MSB stages are used in the proposed opamp current reuse technique. The power consumption for this architecture . can therefore be expressed as This simple comparison shows that the opamp current reuse technique is somewhat less power efficient as compared to the previously mentioned techniques. However, existing opamp-sharing and switched-opamp implementations have additional overheads to compensate for problems such as the summing node reset and turn-on delay. Common solutions using two-stage amplifiers result in partial power savings, and typically consume more power than the single-stage telescopic cascode gain-boosted amplifier. Also some of the other proposed solutions only work for 1.5-bit MDAC architectures. The proposed opamp bias current reuse technique is free from the limitations set by opamp and MDAC architectures, and the gain-boosted telescopic opamp with capacitive level shifting is considered to be one of the more power-efficient opamps. This advantage makes up for the limited scalability in the proposed method. REFERENCES [1] S. Lewis, H. Fetterman, G. Gross, R. Ramachandran, and T. Viswanathan, “A 10-b 20-Msample/s analog-to-digital converter,” IEEE J. Solid-State Circuits, vol. 27, no. 3, pp. 351–358, Mar. 1992. [2] L. Singer, S. Ho, M. Timko, and D. Kelly, “A 12 b 65 MSample/s CMOS ADC with 82 dB SFDR at 120 MHz,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2000) Dig. Tech. Papers, 2000, pp. 38–39. [3] W. Yang, D. Kelly, I. Mehr, M. T. Sayuk, and L. Singer, “A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input,” IEEE J. Solid-State Circuits, vol. 36, no. 12, pp. 1931–1936, Dec. 2001. [4] S. Gupta, M. Choi, M. Inerfield, and J. Wang, “A 1 GS/s 11 b timeinterleaved ADC in 0.13 m CMOS,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2006) Dig. Tech. Papers, 2006, pp. 576–577. [5] B. Song, S. Lee, and M. Tompsett, “A 10 b 15 MHz CMOS recycling two-step A/D converter,” IEEE J. Solid-State Circuits, vol. 25, no. 6, pp. 1328–1338, Dec. 1990. [6] I. Mehr and L. Singer, “A 55-mW, 10-bit, 40-Msample/s Nyquist-rate CMOS ADC,” IEEE J. Solid-State Circuits, vol. 35, no. 3, pp. 318–325, Mar. 2000. [7] G. Geelen, E. Paulus, D. Simanjuntak, H. Pastoor, and R. Verlinden, “A 90 nm CMOS 1.2 V 10 b power and speed programmable pipelined ADC with 0.5 pJ/conversion-step,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2006) Dig. Tech. Papers, 2006, pp. 214–215. [8] B. Murmann and B. Boser, “A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification,” IEEE J. Solid-State Circuits, vol. 38, no. 12, pp. 2040–2050, Dec. 2003. [9] T. Sepke, J. Fiorenza, C. Sodini, P. Holloway, and H. Lee, “Comparator-based switched-capacitor circuits for scaled CMOS technologies,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2006) Dig. Tech. Papers, 2006, pp. 220–221. [10] K. Nagaraj et al., “A 250-mW, 8-b, 52-Msamples/s parallel-pipelined A/D converter with reduced number of amplifiers,” IEEE J. Solid-State Circuits, vol. 32, no. 3, pp. 312–320, Mar. 1997. [11] P. Yu and H. Lee, “A 2.5-V, 12-b, 5-MSample/s pipelined CMOS ADC,” IEEE J. Solid-State Circuits, vol. 31, no. 12, pp. 1854–1861, Dec. 1996. [12] B. Min et al., “A 69-mW 10-bit 80-MSample/s pipelined CMOS ADC,” IEEE J. Solid-State Circuits, vol. 38, no. 12, pp. 2031–2039, Dec. 2003. [13] Y. Chiu, P. Gray, and B. Nikolic, “A 14-bit 12-MS/s CMOS pipeline ADC with over 100-dB SFDR,” IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2139–2151, Dec. 2004. [14] J. Arias et al., “Low-power pipelined ADC for wireless LANs,” IEEE J. Solid-State Circuits, vol. 39, no. 8, pp. 1338–1340, Aug. 2004. [15] M. Waltari and K. Halonen, “1-V 9-bit pipelined switched-opamp ADC,” IEEE J. Solid-State Circuits, vol. 36, no. 1, pp. 129–134, Jan. 2001. [16] H. Kim, D. Jeong, and W. Kim, “A 30 mW 8 b 200 MS/s pipelined CMOS ADC using a switched-opamp technique,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2005) Dig. Tech. Papers, 2005, pp. 284–285. Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply. RYU et al.: A 10-bit 50-MS/s PIPELINED ADC WITH OPAMP CURRENT REUSE [17] H. Choi et al., “A 15 mW 0.2 mm 10 b 50 MS/s ADC with wide input range,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2006) Dig. Tech. Papers, 2006, pp. 226–227. [18] P. Yu et al., “A 14 b 40 Msample/s pipelined ADC with DFCA,” in IEEE Int. Solid-State Circuits Conf. (ISSCC 2001) Dig. Tech. Papers, 2001, pp. 136–137. [19] R. Castello and P. Gray, “A high-performance micropower switchedcapacitor filter,” IEEE J. Solid-State Circuits, vol. SC-20, no. 6, pp. 1122–1132, Dec. 1985. [20] A. Feldman, B. Boser, and P. Gray, “A 13-bit, 1.4-MS/s sigma-delta modulator for RF baseband channel applications,” IEEE J. Solid-State Circuits, vol. 33, no. 10, pp. 1462–1469, Oct. 1998. [21] K. Bult and G. Geelen, “A fast settling CMOS opamp for SC circuits with 90-dB DC gain,” IEEE J. Solid-State Circuits, vol. 25, no. 6, pp. 1379–1990, Dec. 1990. Seung-Tak Ryu (M’06) received the B.S. degree in electrical engineering from Kyungpook National University, Korea, in 1997, and the M.S. and Ph.D. degrees from the Korea Advanced Institute of Science and Technology (KAIST) in 1999 and 2004, respectively. From 2001 to 2002, he was with University of California at San Diego as a visiting researcher sponsored by the Brain Korea 21 program. Since 2004, he has been with Samsung Electronics Company, Ltd., Gyeonggi-do, Korea, where he is involved in designing delta-sigma data converters for audio and modem applications. His research interests include CMOS analog and mixed-mode integrated circuit design, especially high-performance low-power data converters. 485 Bang-Sup Song (S’79–M’83–SM’88–F’99) received the B.S. degree from Seoul National University, Seoul, Korea, in 1973, the M.S. degree from Korea Advanced Institute of Science in 1975, and the Ph.D. degree from University of California at Berkeley in 1983. From 1975 to 1978, he was a research staff at the Agency for Defense Development, Korea. From 1983 to 1986, he was a Member of Technical Staff at AT&T Bell Laboratories, Murray Hill, NJ, and was also a visiting faculty member in the Department of Electrical Engineering, Rutgers University, New Brunswick, NJ. From 1986 to 1999, he was a Professor in the Department of Electrical and Computer Engineering and the Coordinated Science Laboratory, University of Illinois at Urbana-Champaign. In 1999, he joined the faculty of the Department of Electrical and Computer Engineering, University of California at San Diego, where he is endowed with the Charles Lee Powell Chair Professor in Wireless Communication. He was a founder and CEO of Wireless Interface Technologies Inc., San Diego, which was later merged with Chrontel Inc., San Jose, CA, in 2003. Dr. Song received a Distinguished Technical Staff Award from AT&T Bell Laboratories in 1986, a Career Development Professor Award from Analog Devices in 1987, and a Xerox Senior Faculty Research Award from the University of Illinois in 1995. His IEEE activities have been in the capacities of an Associate Editor and a Program Committee Member for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, IEEE International Solid-State Circuits Conference, and IEEE International Symposium on Circuits and Systems. Kantilal Bacrania (M’82) received the B.Sc.(Hons) degree in physics/electronics from the University of Manchester, Manchester, U.K., and the M.Sc. degree in digital techniques from Heriott-Watt University, Edinburgh, Scotland. He is currently a Distinguished Engineer at Conexant Systems Incorporated in the RF and Mixed Signal group where his duties include high-speed converters, signal processing and mixed-signal circuit design in 65 nm and 90 nm CMOS processes for the wireless LAN products. Since 1980, he has worked with Harris Semiconductor, Intersil Corporation and GlobespanVirata Corporation in various positions in the mixed signal groups. He has authored or co-authored articles in the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE International Solid-State Circuits Conference, and VLSI journals and trade magazines and holds 26 patents related to circuit and system design. Previously, he was with Burroughs Corporation and CPI, both in the U.K. His work there was related to magnetic recording, read-write amplifiers and data separators for disk and tape drives. Authorized licensed use limited to: NATIONAL CHANGHUA UNIVERSITY OF EDUCATION. Downloaded on January 12, 2009 at 02:26 from IEEE Xplore. Restrictions apply.