按我下載 - NTU GIEE|國立臺灣大學電子工程學研究所

advertisement

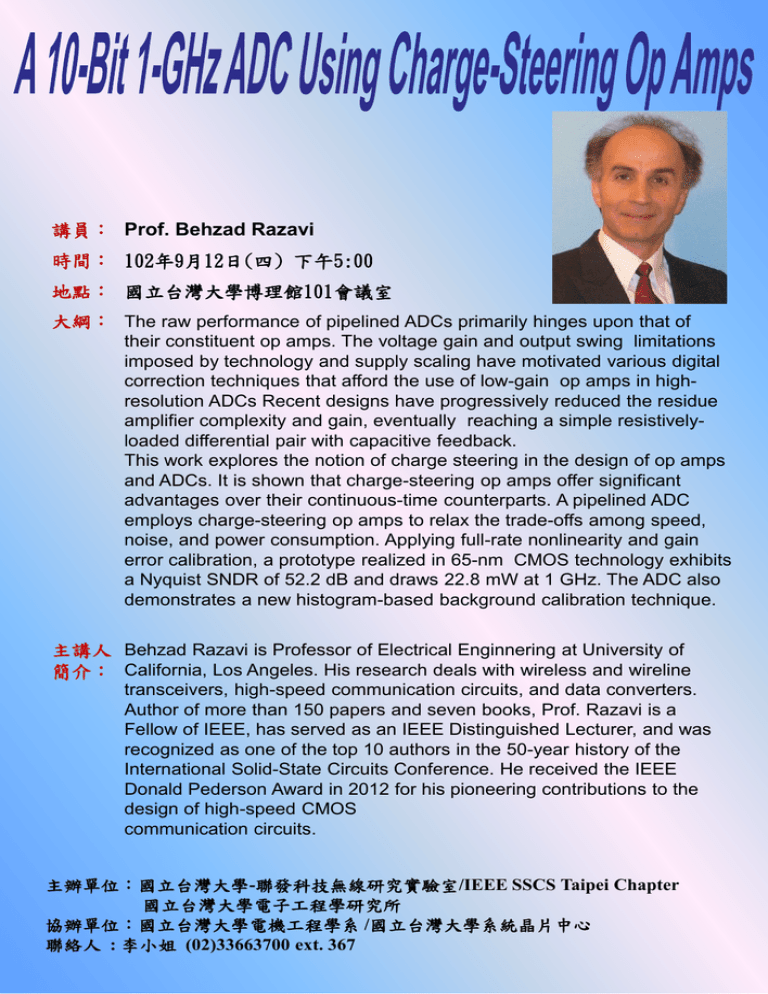

講員: Prof. Behzad Razavi 時間: 102年9月12日(四) 下午5:00 地點: 國立台灣大學博理館101會議室 大綱: The raw performance of pipelined ADCs primarily hinges upon that of their constituent op amps. The voltage gain and output swing limitations imposed by technology and supply scaling have motivated various digital correction techniques that afford the use of low-gain op amps in highresolution ADCs Recent designs have progressively reduced the residue amplifier complexity and gain, eventually reaching a simple resistivelyloaded differential pair with capacitive feedback. This work explores the notion of charge steering in the design of op amps and ADCs. It is shown that charge-steering op amps offer significant advantages over their continuous-time counterparts. A pipelined ADC employs charge-steering op amps to relax the trade-offs among speed, noise, and power consumption. Applying full-rate nonlinearity and gain error calibration, a prototype realized in 65-nm CMOS technology exhibits a Nyquist SNDR of 52.2 dB and draws 22.8 mW at 1 GHz. The ADC also demonstrates a new histogram-based background calibration technique. 主講人 Behzad Razavi is Professor of Electrical Enginnering at University of 簡介: California, Los Angeles. His research deals with wireless and wireline transceivers, high-speed communication circuits, and data converters. Author of more than 150 papers and seven books, Prof. Razavi is a Fellow of IEEE, has served as an IEEE Distinguished Lecturer, and was recognized as one of the top 10 authors in the 50-year history of the International Solid-State Circuits Conference. He received the IEEE Donald Pederson Award in 2012 for his pioneering contributions to the design of high-speed CMOS communication circuits. 主辦單位:國立台灣大學-聯發科技無線研究實驗室/IEEE SSCS Taipei Chapter 國立台灣大學電子工程學研究所 協辦單位:國立台灣大學電機工程學系 /國立台灣大學系統晶片中心 聯絡人 : 李小姐 (02)33663700 ext. 367