What is Packaging?

advertisement

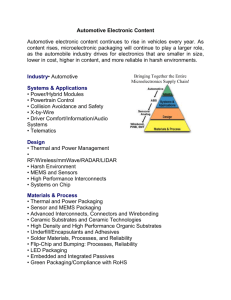

Packaging Challenges for High Speed Analog Devices Ben Sutton, Matt Romig, Souvik Mukherjee, Sreenivasan Koduri Texas Instruments April 30, 2013 1 IEEE International High Speed Interconnects Symposium, April 30, 2013 Agenda • What is high speed Analog? • What is packaging? • Co-design of Die, Package, and System • Specific Example: 7 GHz QFN • Summary 2 IEEE International High Speed Interconnects Symposium, April 30, 2013 What is Analog? Embedded Processing 3 IEEE International High Speed Interconnects Symposium, April 30, 2013 What is High Speed Analog? HDMI RF Optics uWaves High Speed ADC SERDES USB3.0 Thunderbolt High-Speed Current Switching Embedded Processing ESD RF Optics uWave High Speed DAC DDR3/4 SATA Switches 4 IEEE International High Speed Interconnects Symposium, April 30, 2013 WHAT IS PACKAGING? 5 IEEE International High Speed Interconnects Symposium, April 30, 2013 What is Packaging, Electrically Speaking? Simple RLC Section • Old Days – R is small – ωL is small since frequency is low – 1/(ωC) is large – Package behaves like a small resistor At 1 MHz: - R ~ 4 mΩ - L ~ j5 mΩ - C ~ -j3 MΩ • Nowadays – R∝ 𝑓 – ωL is large – 1/ (ωC) is small – Package behaves like a waveguide – Package reflects signals if mismatched At 10 GHz: - R ~ 350 mΩ - L ~ j50 Ω - C ~ -j300 Ω IEEE International High Speed Interconnects Symposium, April 30, 2013 Practical Challenges VS Same Physics Challenge in Different Applications Different Solutions New Packaging Technologies Existing Packaging Technologies High Complexity Low Complexity Long Development Cycle Short Development Cycle 7 IEEE International High Speed Interconnects Symposium, April 30, 2013 Broad Range of Packaging MicroStar Ultra Thin™ Land Grid Array Chip Scale Package (u*UT LGA) Thermally Enhanced BGAs Most Popular Packaging Options Mini Small Outline Package (MSOP) Laminate Chip Scale BGA (nFBGA) QFN MicroStar JR ™ Chip Scale Pkg (u*JR BGA) Small Outline Transistor Package Transistor Outline (SOT23) (TO236) Analog Mirror Packages WCSP Small Outline No Leads (SON) Shrink Small Outline Package (SSOP) Thin Quad Flatpack (TQFP) Heat Sink Thin Quad Flatpack (HTQFP) Plastic Dual-In-Line Package (PDIP) Small Outline Transistor (SOT223) PowerPad Small Outline Package (HSOP) Surface Mount Header (DDPak) Thin Shrink Small Outline Package (TSSOP) MicroStar BGA ™ Chip Scale Tape BGA (u*BGA) Small Outline Integrated Circuit (SOIC) Power Small Outline Package (PSOP3) Wafer Scale Package (WSP) Transistor Outline (TO220) Heat Slug Small Outline Integrated Circuit Miniature Plastic Packages Power Modules SOT-23 SC-70 Multi-Row QFN Multi-Die QFN Flip-Chip QFN ESV Flip-Chip Power Packages SON Stacked-Die QFN 2 Dies + 2Passives 2 Stacked Dies + 6 Passives LLGA U*BGA Chip-on-Lead QFN IEEE International High Speed Interconnects Symposium, April 30, 2013 Stacked Passives An LDO stacked on a Passive 8 Two Emerging Packaging Types Pb-Free Solder Routing Layer Die Metal Silicon Die Backside Coat WCSP: Wafer Chip Scale Package QFN: Quad Flat No-Lead Package 9 IEEE International High Speed Interconnects Symposium, April 30, 2013 CO-DESIGN OF DIE, PACKAGE, AND SYSTEM 10 IEEE International High Speed Interconnects Symposium, April 30, 2013 Electrical Co-Design Methodology of concurrently optimizing the system (viz. Die + Package + PCB), early in the design phase, to: Meet electrical performance in customer end-system Enable use of off-the shelf packaging technology for the product/system thru better product/system spec definition Reduce physical design spins of Si/Package/PCB faster time-to-market Electrical Co-Design Applications Signal Path Integrity Power Management EMI/EMC Compliance High-speed SerDes, Switched Mode Power ICs Integrated Digital-RF SOCs DDRs, Re-timers Isolated Power ICs Switched Mode Power Supplies Consumer interfaces (USB3/HDMI/DSI) High-Speed SerDes Consumer Analog Signal Path Switches Memory Interfaces (DDRs) RF Transceiver paths MEMS 11 IEEE International High Speed Interconnects Symposium, April 30, 2013 Electrical Modeling Capabilities Scalability 3D Modeling of Multi-layer WB PBGA Package Accuracy Model-to-Hardware Correlation 3D Modeling of Package +PCB Breadth 3D current density Analysis in RF Test-vehicle Static IR drop analysis of FCCSP Package 12 IEEE International High Speed Interconnects Symposium, April 30, 2013 Model-to-Hardware Correlation for WB BGA Custom Die Package Extensive efforts and collaboration constantly calibrate modeling flows/tools against measurements. IEEE International High Speed Interconnects Symposium, April 30, 2013 13 CASE STUDY – 7 GHZ IN A QFN 14 IEEE International High Speed Interconnects Symposium, April 30, 2013 Design Challenge • Bandwidth Goal: 3dB >5GHz • Application: FET Switch, 2-Ch • Design Cycle: 3 Months Despite low device complexity, design challenge is significant: – Package size limits optimization of wire length – Differential signaling requires good coupling between P/N – Design cycle drives single-pass success 15 IEEE International High Speed Interconnects Symposium, April 30, 2013 Design Process 1. Reduce Parasitics – Bondpad Geometry: – Bondpad Placement: – Moving bondpads toward the center of the die reduces capacitance and resistance on the die while improving flexibility for reducing P/N skew 2. Package Modeling – Full-wave package modeling captures package behavior out past 7th harmonic of the signal • Capturing references and return path properly is key for accuracy – Design of the leadframe has a major impact on performance 3. Tune Silicon Design 4. Repeat 16 IEEE International High Speed Interconnects Symposium, April 30, 2013 Leadframe Contribution Design on Left: ~75% larger bandwidth! 17 IEEE International High Speed Interconnects Symposium, April 30, 2013 Probe Measurement Performance RSE RLS Leadframe Bandwidth RSE 6.8 GHz RLS 6.2 GHz 18 IEEE International High Speed Interconnects Symposium, April 30, 2013 Summary • Analog semiconductor devices face a significant challenge when it comes to packaging interconnect as frequencies push towards 10’s of GHz • Miniaturization and aggressive market schedules drive re-use of simple, existing packaging technologies, and place physical design constraints on the package internals • These challenges can be met through precise package modeling and co-design with the silicon – a system-level, coupled approach. 19 IEEE International High Speed Interconnects Symposium, April 30, 2013