Informatics 2C Tutorial 5 Basic Logic Design and Processor

advertisement

Informatics 2C Tutorial 5

Basic Logic Design and Processor Organization

Aris Efthymiou and Salman Khan

1. Ripple Carry Adder

Assume that the propagation delay in each gate in a 32-bit ripple carry

adder is 100ps. How fast can a 32-bit addition be performed? Assuming

that the adder delay is the major limiting factor on the clock speed, how

fast can we clock the processor?

The longest path is from carry in at bit 0 to sum 31. For the full adders

at bit positions 0-31, the carry propagates through 2 gates: one AND and

one OR (cout = ab + ac + bc) For the last full adder the slowest path is

to the sum output, not the carry output. The delay is 3 gates: inverter,

AND, OR. (s = !a*!b*c +!a*b*!c+a*!b*!c+a*b*c) So total 31 full-adders

* 2 gates each + 3 gates for the last adder = 65 gate delays * 100ps =

6.5ns

2. Modulo-6 Counter

Design a synchronous Modulo-6 counter that will be able to count up to

5 clock positive edges. When it reaches 5, it resets to 0 and it starts the

whole process again. In order to design this counter you can use D flipflops and any two or three input gate you like.

First note that we need to be able to count up to 6, which means that

we need 3 bits to represent all the possible states of our FSM. The state

machine can be seen in Figure 1. From this FSM we can derive the

transition table and from that we have the circuit shown in figure 2.

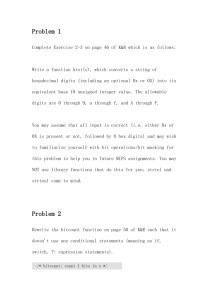

3. Transforming C to Assembly

Write a program in MIPS assembly, that will perform the same operation

as the following C-code excerpt.

#define SIZE

8

int a[SIZE];

int *p;

p = a;

*p = *p +1;

p = p + 1;

for (i=1; i< SIZE; i++, p++) {

1

000

0

101

5

1

100 4

2

001

010

3

011

Figure 1: Modulo Counter FSM

nc2

D Q

nc1

D Q

nc0

D Q

c0

c1

c2

clk

Figure 2: Modulo Counter Circuit

2

if((i%2) == 0){

*p = *(p-1)+1;

} else {

*p = *(p-1)-1;

}

}

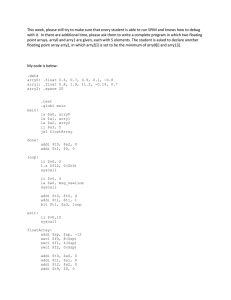

.data

from:.word 1,2,3,4,5,6,7,8

.globl main

.text

main:

# Use $t1 to store SIZE

addi

$t1, $zero, 8

# Use $t2 to store i

addi

$t2, $zero, 1

# Assume that we hold p in $s0

# and *p in $s1

# p = a

la

$s0, from

# *p = *p +1

lw

$s1, 0($s0)

addi

$s1, $s1, 1

sw

$s1, 0($s0)

# increment p - we use words, therefore add 4

addi

$s0, $s0, 4

# Smart compiler knows that loop will be entered first time

# so the condition check moved to end of loop

loop:

# Get *p

lw

$s1, 0($s0)

# Check for the mod 2 of i

andi

$t3, $t2, 1

bne

$t3, $zero, odd

# i was even

addi

$s1, $s1, 1

j

check

3

odd:

# i was odd

addi

$s1, $s1, -1

check:

# update memory first

sw

$s1, 0($s0)

# increase i and p

addi

$t2, $t2, 1

# we use words, therefore add 4

addi

$s0, $s0, 4

# Check whether done

blt

$t2, $t1, loop

end:

4