Outline Positive Edge Triggered D Flip-flop Other Flip

advertisement

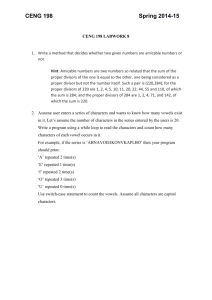

CENG 4534: Digital System Design Outline Other Flip-flops and Latches Combinational Logic Design Rising edge triggered D flip-flop: ARCHITECTURE dataflow OF dff IS BEGIN q <= d WHEN (clk’EVENT AND clk = ‘1’) ELSE q; END dataflow; Sequential Logic Design Falling edge triggered D flip-flop : q <= d WHEN (clk’EVENT AND clk = ‘0’) ELSE q; Pulse triggered D latch: q <= d WHEN (clk = ‘1’) ELSE q; Rising edge triggered T flip-flop: q <= NOT q WHEN (clk’EVENT AND clk = ‘1’) ELSE q; CENG 4534 - 1 Positive Edge Triggered D Flip-flop CENG 4534 - 3 Reset and Preset for Flip-flops Needed for power-up initialization of hardware LIBRARY ieee; USE ieee.std_logic_1164.ALL; Synchronous or Asynchronous (more common) ENTITY dff IS PORT (d, clk : IN std_logic; q : OUT std_logic); END dff; PROCESS (clk, reset) -- sensitive to clk or reset BEGIN IF reset = ‘1’ THEN q <= ‘0’; -- Async reset ARCHITECTURE behavior OF dff IS BEGIN PROCESS (clk) -- sensitive ONLY to clk BEGIN -- rising clk edge IF (clk’EVENT AND clk = ‘1’) THEN q <= d; ELSE q <= q; -- NOT needed (implied) END IF; END PROCESS; END behavior; CENG 4534 - 2 ELSIF (clk’EVENT AND clk = ‘1’) THEN q <= d; END IF; END PROCESS; Change reset to preset: IF preset = ‘1’ THEN q <= ‘1’; -- Asynchronous preset CENG 4534 - 4 1 CENG 4534: Digital System Design Reset and Preset for Flip-flops Counter: ver. 2 Synchronous reset: IF (clk’EVENT AND clk = ‘1’) THEN IF reset = ‘1’ THEN q <= ‘0’; -- Sync reset ELSE q <= d; END IF; END IF; Dataflow version of reset: ARCHITECTURE dataflow OF dff_reset IS BEGIN q <= 0 WHEN reset = ‘1’ ELSE -- Async reset d WHEN (clk’EVENT AND clk = ‘1’) ELSE q; ENTITY count8 IS PORT (clk, reset, load, enable : IN std_logic; data: IN unsigned (7 DOWNTO 0); cnt : BUFFER unsigned (7 DOWNTO 0)); END count8; ARCHITECTURE behavior OF count8 IS BEGIN PROCESS (clk, reset) BEGIN IF reset=‘1’ THEN cnt <= X”00”; -- or (OTHERS => ‘0’) ELSIF rising_edge(clk) THEN IF load=‘1’ THEN cnt <= data; ELSIF enable=‘1’ THEN cnt <= cnt + 1; END IF; END IF; END PROCESS; END behavior; END dataflow; CENG 4534 - 5 CENG 4534 - 7 Counter: ver. 1 State Machines LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE work.numeric_std.ALL; What are state machines? ENTITY count8 IS PORT (clk : IN std_logic; cnt : BUFFER unsigned (7 DOWNTO 0)); END count8; ARCHITECTURE simple OF count8 IS BEGIN PROCESS (clk) BEGIN IF rising_edge(clk) THEN cnt <= cnt + 1; END IF; END PROCESS; END too_simple; CENG 4534 - 6 • Sequential logic circuits which can have only a fixed number of possible states • Their outputs and the next state are dependent on the inputs and the current state Some methods for describing the behavior of state machines: • State diagrams • State tables • Hardware description languages CENG 4534 - 8 2 CENG 4534: Digital System Design Traditional Design Methodology Memory Controller Example ready Given a problem description, perform the following steps to outputs design a state machine: idle 1. Draw a state diagram for the given problem description ready 2. Derive a state table from the state diagram ready ready decision 3. Eliminate equivalent states by matching rows of the state table 4. Make state assignments and create a state transition table read_write 5. From state transition table generate next state and output write equations state oe we idle 0 0 decision 0 0 write 0 1 read 1 0 read_write ready read ready CENG 4534 - 9 CENG 4534 - 11 Memory Controller Example Memory Controller Example Design a state machine for a simple memory controller with the following problem description: INPUTS: read_write, ready OUTPUTS: • To enable and disable the write enable and output enable State q0 q1 00 01 11 10 oe we • The inputs to the controller are ready and read_write, generated by a microprocessor Idle 00 00 01 01 00 0 0 • The outputs of the controller are oe and we Decision 01 11 11 10 10 0 0 • A new operation begins with the assertion of ready following a completed transaction (or upon power up for the initial transaction) Write 11 11 00 00 11 0 1 • One clock cycle after the commencement of the transaction, the value of read_write determines whether it is a read or write cycle Read 10 10 00 00 10 1 0 • – If read_write is asserted then it is a read cycle, else it is a write cycle – we is asserted during a write cycle and oe is asserted during a read cycle A cycle is completed with the assertion of ready CENG 4534 - 10 Next State: Q0 Q1 Q0 = q0’.q1 + q0.ready’ we = q0q1 Q1 = q0’.q1’.ready + q0’.q1.read_write’ + q0.q1.ready’ oe = q0q1’ CENG 4534 - 12 3 CENG 4534: Digital System Design State Machines In VHDL (p2) • A given state diagram can be easily translated into a high level VHDL description without having to generate the state transition table • In VHDL each state can be translated to a case in a CASE-WHEN construct • WHEN decision => oe <= '0'; we <= '0'; IF (read_write = '1') THEN next_state <= read; ELSE DECISION next_state <= write; END IF; WHEN read => oe <= '1'; we <= '0'; IF (ready = '1') THEN next_state <= idle; ELSE next_state <= read; END IF; The state transitions can then be specified in IF-THENELSE statements. READ CENG 4534 - 13 Memory Controller Using VHDL (p1) ENTITY example IS PORT ( read_write, ready, clk: IN bit; oe, we: OUT bit); END example; ARCHITECTURE state_machine OF example IS TYPE StateType IS (idle, decision, read, write); SIGNAL present_state, next_state: StateType; BEGIN state_comb:PROCESS (present_state, read_write, ready) BEGIN CASE present_state IS CENG 4534 - 15 (p3) WHEN write => oe <= '0'; we <= '1'; IF (ready = '1') THEN next_state <= idle; WRITE ELSE next_state <= write; END IF; END CASE; END PROCESS state_comb; state_clocked:PROCESS(clk) BEGIN WHEN idle => oe <= '0'; we <= '0'; IF ready = '1' THEN next_state <= decision; ELSE next_state <= idle; END IF; IDLE IF (clk'event and clk='1') THEN present_state <= next_state; END IF; NEXT STATE END PROCESS state_clocked; END ARCHITECTURE state_machine; CENG 4534 - 14 CENG 4534 - 16 4 CENG 4534: Digital System Design Verifying Design Functionality The Simulation Cycles ns delta • read_write ready clk oe we present_state next_state After the state machine has been described, it must be 0 +0 0 0 1 0 0 idle idle simulated to see if it is an accurate model. 40 +0 0 1 1 0 0 idle idle 40 +1 0 1 1 0 0 idle decision 50 +0 0 1 0 0 0 idle decision 100 +0 0 1 1 0 0 idle decision 100 +1 0 1 1 0 0 decision 100 +2 0 1 1 0 0 decision write 110 +0 0 0 1 0 0 decision write 125 +0 1 0 1 0 0 decision write 125 +1 1 0 1 0 0 decision read 150 +0 1 0 0 0 0 decision read • Typically done using a VHDL simulator • First part of simulation is the initialization phase: • All signals without explicit initialization value are initialized to the ‘left value of their data types, and processes executed to suspension. • All bits are initialized to ‘0’, and present_state and next_state signals are initialized to idle. Both processes are then executed. CENG 4534 - 17 The Simulation Waveform CENG 4534 - 19 The Simulation Steps (t=0) clk • When state_comb process is evaluated, present_state is idle, and CASE statement jumps to that point in the code. • The IF condition is evaluated: input ready is ‘0’ so next_state <= idle is executed. • Execution jumps to end of CASE statement. • At the end of the process, next_state is still idle. • When state_clocked process is evaluated, the IF condition is false and the process suspends. No new value for present_state is scheduled. ready read_write present_state next_state idle idle decision decis. wr. read read idle idle decis. oe we 0ns 100ns 200ns Q0 = q0.q1’ + q0.ready’ Q1 = q0’.q1’.ready + q0’.q1.read_write’ + q0.q1.ready’ 300ns we = q0q1 oe = q0q1’ decision 400ns idle = 00 decision = 01 write = 11 read = 10 CENG 4534 - 18 CENG 4534 - 20 5 CENG 4534: Digital System Design (t=40) (t=110) Processes remain inactive until one of the signals in sensitivity list change value. state_comb will execute if the present state or state machine inputs change. state_clocked will execute at any time the clk changes value. • • At 40ns, ready is asserted. This causes the state_comb process to execute. • • The CASE statement jumps to when present_state is idle. the IF conditions then executes next_state <= decision. • • At 110ns, ready is deasserted. state_comb process is executed. The CASE statement jumps to the proper line. Note: although next_state has changed value, present_state has not, so it is still at decision). The signal assignment next_state <= write does not cause a new value for next_state (it is already write). The process suspends, causing next_state to be updated to decision. CENG 4534 - 21 CENG 4534 - 23 (t=50, 100) (t=125 thru 250) • At 50ns, clk transitions from 1 to 0. The state_clocked process becomes active. The IF condition evaluates false and the process suspends with no new values for present_state. • At 100ns, clk transitions from 0 to 1. The state_clocked process becomes active. The IF condition evaluates true, so present_state is given the value of next_state, which is decision, after the process suspends. • • The transition occurs one delta delay after 100ns because we are simulating the source code, not the postlayout model. After the design is implemented in a PLD, the state transition will occur after some propagation delay. The change in value of present_state from idle to decision causes the state_comb process to be executed. The CASE statement jumps to the proper line. read_write is false, so next_state becomes write after two delta delays after 100ns. CENG 4534 - 22 • At 125ns, read_write is asserted. The state_comb process is executed. The CASE statement jumps to proper line. The IF condition evaluates true because read_write is asserted. The ELSE condition is not executed. The process suspends with next_state as read. • At both 150ns and 200ns, the state_clocked process is executed due to a transition in clk. At 200ns, present_state changes value from decision to read, which causes the state_comb process to be executed. When the process suspends one delta delay after 200ns, oe becomes 1. • At 210ns, read_write is deasserted, causing state_comb to be executed. ready is not asserted, so next_state retains its value. • At 250ns the state_clocked process is executed due to a transition in clk. But the transition is from 1 to 0, so the process suspends. CENG 4534 - 24 6 CENG 4534: Digital System Design (t=300 thru 400) Memory Controller System Description • At 300ns the state_clocked process executes again. This time the IF condition is true, but because next_state is the same as present_state, a new value is not assigned. • At 310ns, ready is asserted, and state_comb is executed. The IF condition is true (ready is asserted), so next_state is scheduled to assume the value idle. • At 400ns, the state_clocked process is executed, and present_state assumes the value of idle. This causes the state_comb process to execute. When the process is suspended, the signal oe is updated, as well as next_state. • Access initiated to the memory buffer by asserting bus_id to X“F3” • Read_write asserted indicates a read from the memory buffer and deasserted indicates a write to the memory buffer • Read _write asserted and burst deasserted: does singleword read • Read_write and burst asserted : does four-word burst read • Following the burst read in the first read cycle the controller accesses four locations from the buffer CENG 4534 - 25 State Machine Example: Memory Controller CENG 4534 - 27 Memory Controller System Description • Each successive assertion of ready precedes access to consecutive locations ADDRESS DATA • During a read, controller asserts the oe (output enable) to the memory buffer and during a burst, increments the lowest two bits of the address BUS_ID OE RESET READ_WRITE READY BURST STATE MACHINE WE SRAM ADDR1 MEMORY • Write is always a single-word write ARRAY • During write we (write enable) is asserted, address specifies the memory location where data is to be written ADDR0 CLK • Read and write accesses completed upon assertion of ready CENG 4534 - 26 CENG 4534 - 28 7 CENG 4534: Digital System Design Memory Controller State Diagram Reset(sync) Idle Bus_id = X “F3” Ready Write Read_write Decision Other Bus_id • Assertion of burst and ready while in the read1 state causes the machine to transition through each of the read states advancing on ready Ready.burst Read_write Read1 Ready.burst State oe we 0 0 00 Decision 0 0 00 Read1 1 0 00 Read2 1 0 01 Read3 1 0 10 Read4 1 0 11 Write 0 1 00 Idle State Diagram Description Ready addr[1:0] Read2 Ready • oe is asserted during each of the read cycles Ready • addr is incremented in successive read cycles following the first Ready Ready Read3 • When read_write is ‘0’ in the decision state, machine branches to write, asserts we, waits for the ready signal and then returns to the idle state Ready Read4 Ready CENG 4534 - 29 State Diagram Description CENG 4534 - 31 From State Diagram to VHDL Code • Synchronous reset places the state machine in idle • The controller remains in idle when the memory buffer is not being accessed • When bus_id is asserted, machine transitions to the decision state • On the next clk cycle the machine transitions to either read or write state depending on the value of read_write • Assertion of ready without burst indicates a single-word read while in the read1 state. The controller returns to the idle state. CENG 4534 - 30 • Section of code inside the state-comb process derived directly from the state diagram • Each state is one of the case statement branches • Sequential signal-assignment statements document the state machine Moore (state-based) outputs • IF-THEN-ELSE statements document the state transitions and Mealy (input&state-based) outputs CENG 4534 - 32 8 CENG 4534: Digital System Design VHDL Code for Memory Controller (p1) (p3) WHEN decision => oe <=‘0’; we <=‘0’; addr<= “00”; IF (read_write = ‘1’) THEN next_state <= read1; ELSE next_state <= write; END IF; WHEN read1 => oe <= ‘1’; we <= ‘0’; addr <= “00”; IF (ready = ‘0’) THEN next_state <= read1; ELSIF (burst = ‘0’) THEN next_state <= idle; ELSE next_state <= read2; END IF; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY memory_controller IS PORT( reset, read_write, ready, burst, clk : IN std_logic; bus_id : IN std_logic_vector(7 DOWNTO 0); oe, we : OUT std_logic; addr : OUT std_logic_vector(1 DOWNTO 0)); END memory_controller; ARCHITECTURE state_machine OF memory_controller IS TYPE statetype IS (idle, decision, read1, read2, read3, read4, write); SIGNAL present_state, next_state : statetype; CENG 4534 - 33 CENG 4534 - 35 (p4) (p2) BEGIN state_comb:PROCESS(reset, bus_id, present_state, burst, read_write, ready) BEGIN IF (reset = ‘1’) THEN oe <=‘-’; we <=‘-’; addr <=“--”; next_state <= idle; ELSE CASE present_state IS WHEN idle => oe <= ‘0’; we <= ‘0’; addr<= “00”; IF (bus_id = “11110011”) THEN -- X”F3” next_state <= decision; ELSE next_state <= idle; END IF; CENG 4534 - 34 WHEN read2 => oe <=‘1’; we <=‘0’; addr <=“01”; IF (ready = ‘1’) THEN next_state <= read3; ELSE next_state <= read2; END IF; WHEN read3 => oe <= ‘1’; we <= ‘0’; addr <= “10”; IF (ready = ‘1’) THEN next_state <= read4; ELSE next_state <= read3; END IF; WHEN read4 => oe <= ‘1’; we <= ‘0’; addr <= “11”; IF (ready = ‘1’) THEN next_state <= idle; ELSE next_state <= read4; END IF; CENG 4534 - 36 9 CENG 4534: Digital System Design (p5) Synchronous Reset in a Two-Process FSM (cntd.) WHEN write => oe <= ‘0’; we <= ‘1’; addr <= “00”; IF (ready = ‘1’) THEN next_state <= idle; ELSE next_state <= write; END IF; END CASE; END IF; END PROCESS state_comb; Reset as the last statement of the process: state_comb:PROCESS(reset,present_state,burst,read_write,ready) BEGIN CASE present_state IS … END CASE; state_clocked:PROCESS(clk) BEGIN IF rising_edge(clk) THEN present_state <= next_state; END IF ; END PROCESS state_clocked; IF (reset = ‘1’) THEN next_state <= idle; END IF; END PROCESS state_comb; END state_machine; CENG 4534 - 37 Synchronous Reset in a Two-Process FSM CENG 4534 - 39 Code Structure - CPLD Architecture Analogy Rather than specifying the reset transition to the idle state in each branch of the case statement, IF-THEN-ELSE statements is used either at the beginning of the process or at the end of the process as its last statement Reset in the beginning of the process: Combinational logic Inputs state_comb:PROCESS(reset, present_state, burst, read_write,ready) BEGIN IF (reset = ‘1’) THEN oe <= ‘-’; we <= ‘-’; addr <= “--”; -- needed to avoid -- creating latches next_state <= idle; ELSE CASE present_state IS … END CASE; END IF; END PROCESS state_comb; CENG 4534 - 38 CASE…WHEN… IF…THEN… ELSE... Flip-flops Next state clk’EVENT AND clk=‘1’ Current state CENG 4534 - 40 10 CENG 4534: Digital System Design Asynchronous Reset in a Two-Process FSM Code Structure - CPLD Architecture Analogy Combinational logic An asynchronous reset is written as follows: Flip-flops NEXT STATE2 D Q CURRENT STATE2 D Q CURRENT STATE1 state_clocked:PROCESS(clk, reset) BEGIN IF reset = ‘1’ THEN present_state <= idle; ELSIF rising_edge(clk) THEN present_state <= next_state; END IF; END PROCESS state_clocked; Inputs NEXT STATE1 •If reset is asserted, then the state machine remains idle regardless of the value of clk. NEXT STATE0 D Q CURRENT STATE0 •If reset is not asserted and the clk change is from ‘0’ to ‘1’, then the state machine transitions to the next state. •Asynchronous CLK Current state CENG 4534 - 41 reset is better than synchronous reset when used only during initialization or system failure, because synchronous reset may require additional device resources (such as product terms) CENG 4534 - 43 One-Process FSM Code Structure - CPLD Architecture Analogy • • • One process describes the combinational logic and another describes synchronization of state transitions to the clock Decoding of present_state and inputs is performed in the combinatorial portion (product-term array) of the logic block just as it is described in the combinatorial process in the code Synchronization of next_state is described in the state_clocked process, which describes a bank of registers such as the macrocells in a logic block CENG 4534 - 42 One Process FSM • State transitions and transition synchronization to the clock are all described in one process. • Outputs are described using concurrent signal assignments (outside the process) One Process FSM code example • Functionally equivalent to two-process FSM with the use of an asynchronous reset instead of a synchronous reset CENG 4534 - 44 11 CENG 4534: Digital System Design One-Process FSM Example (p1) (p3) ARCHITECTURE state_machine OF memory_controller IS TYPE statetype IS (idle, decision, read1, read2, read3, read4, write); SIGNAL state: statetype; BEGIN state_tr: PROCESS (reset, clk) -- one process fsm BEGIN IF reset = ‘1’ THEN -- asynchronous reset state <= idle; ELSIF rising_edge(clk) THEN -- synchronization to clk CASE state IS -- state transitions defined WHEN idle => IF (bus_id = “11110011”) THEN state <= decision; ELSE state <= idle; END IF; WHEN read3 => IF (ready = ‘1’) THEN state <= read4; ELSE state <= read3; -- implicit memory, as in read2 END IF; WHEN read4 => IF (ready = ‘1’) THEN state <= idle; ELSE state <= read4; END IF; WHEN write => IF (read = ‘1’) THEN state = idle; ELSE state <= write; END IF; END CASE; END IF; END PROCESS state_tr; CENG 4534 - 45 (p2) CENG 4534 - 47 (p4) WHEN decision => IF (read_write = ‘1’) THEN state <= read1; ELSE state <= write; END IF; WHEN read1 => IF (read = ‘0’) THEN state <= read1; ELSIF (burst = ‘0’) THEN state <= idle; ELSE state <= read2; END IF; WHEN read2 => IF (ready = ‘1’) THEN state <= read3; END IF; -- implied: else state <= read2; CENG 4534 - 46 -- combinatorially decoded outputs, concurrent assignments WITH state SELECT oe <= ‘1’ WHEN read1 | read2 | read3 | read4, ‘0’ WHEN others; we <= ‘1’ WHEN state = write ELSE ‘0’; WITH state SELECT addr <= “01” WHEN “10” WHEN “11” WHEN “00” WHEN END state_machine; read2, read3, read4, OTHERS; CENG 4534 - 48 12 CENG 4534: Digital System Design State and Output Assignments in One-Process FSM Process state_tr defines state transitions Use of ELSIF rising_edge(clk) THEN • Implies that all signal assignments made within the process are made on the rising edge of the clock State transitions • Defined using the CASE statement following the ELSIF statement described above • implies synchronous state assignment CENG 4534 - 49 State and Output Assignments in One-Process FSM Output Assignments In this example these assignments are made using concurrent signal assignment • Recommended because outputs and transitions are easily identified • Outputs could be assigned in the CASE state branches instead • Not recommended because the code is not as clear to the reader, and the outputs would have to be defined in terms of the next state since they would be registered • Two-process FSM recommended generally Easiest to create and maintain, especially for large FSMs Simple clocked process for state register • Simple combinational process for state transitions and outputs • • CENG 4534 - 50 13