Encounter Timing System

A single view of timing for faster design closure and signoff

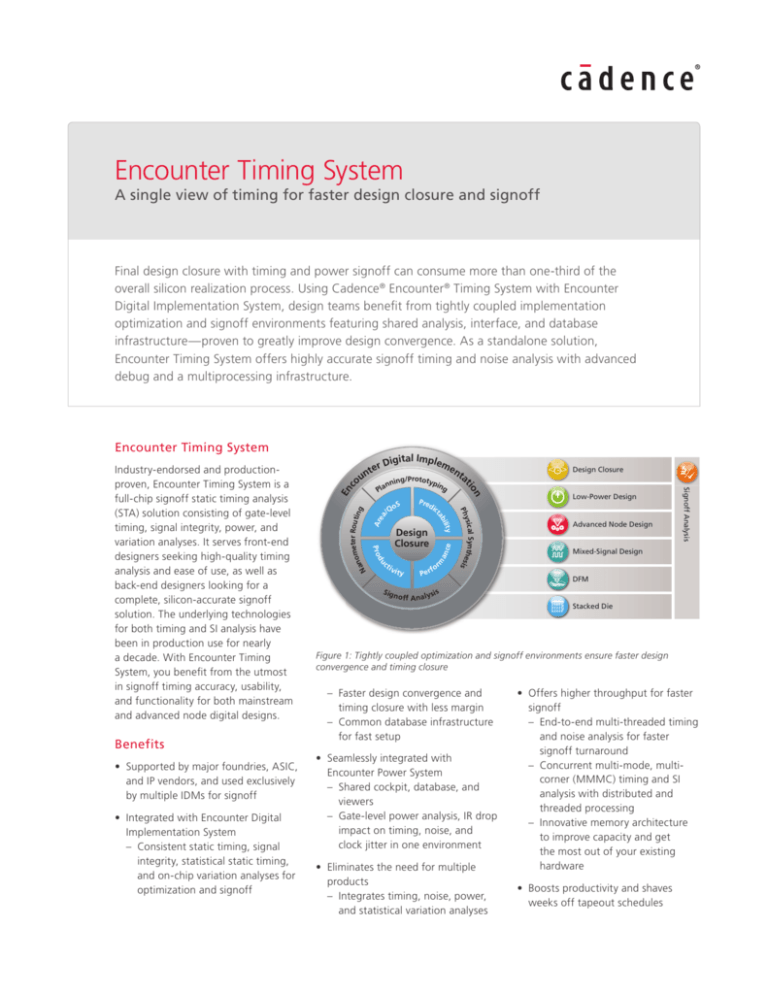

Final design closure with timing and power signoff can consume more than one-third of the

overall silicon realization process. Using Cadence® Encounter® Timing System with Encounter

Digital Implementation System, design teams benefit from tightly coupled implementation

optimization and signoff environments featuring shared analysis, interface, and database

infrastructure—proven to greatly improve design convergence. As a standalone solution,

Encounter Timing System offers highly accurate signoff timing and noise analysis with advanced

debug and a multiprocessing infrastructure.

ce

an

Sig

m

Are

a

eter Routin

nom

g

Na

iv i

ty

Pe

n o ff A n

r

rf o

Design Closure

Low-Power Design

Advanced Node Design

Signoff Analysis

Design

Closure

l Synthe

ysica

sis

Ph

ct

Pred

ic

n

tio

• Integrated with Encounter Digital

Implementation System

–– Consistent static timing, signal

integrity, statistical static timing,

and on-chip variation analyses for

optimization and signoff

oS

/Q

ity

bil

ta

• Supported by major foundries, ASIC,

and IP vendors, and used exclusively

by multiple IDMs for signoff

g

Pl

du

Benefits

lI

Digita mpleme

er

nt

nt

a

u

/Prototyp

o

ning

in

an

P ro

Industry-endorsed and productionproven, Encounter Timing System is a

full-chip signoff static timing analysis

(STA) solution consisting of gate-level

timing, signal integrity, power, and

variation analyses. It serves front-end

designers seeking high-quality timing

analysis and ease of use, as well as

back-end designers looking for a

complete, silicon-accurate signoff

solution. The underlying technologies

for both timing and SI analysis have

been in production use for nearly

a decade. With Encounter Timing

System, you benefit from the utmost

in signoff timing accuracy, usability,

and functionality for both mainstream

and advanced node digital designs.

En

c

Encounter Timing System

Mixed-Signal Design

DFM

is

alys

Stacked Die

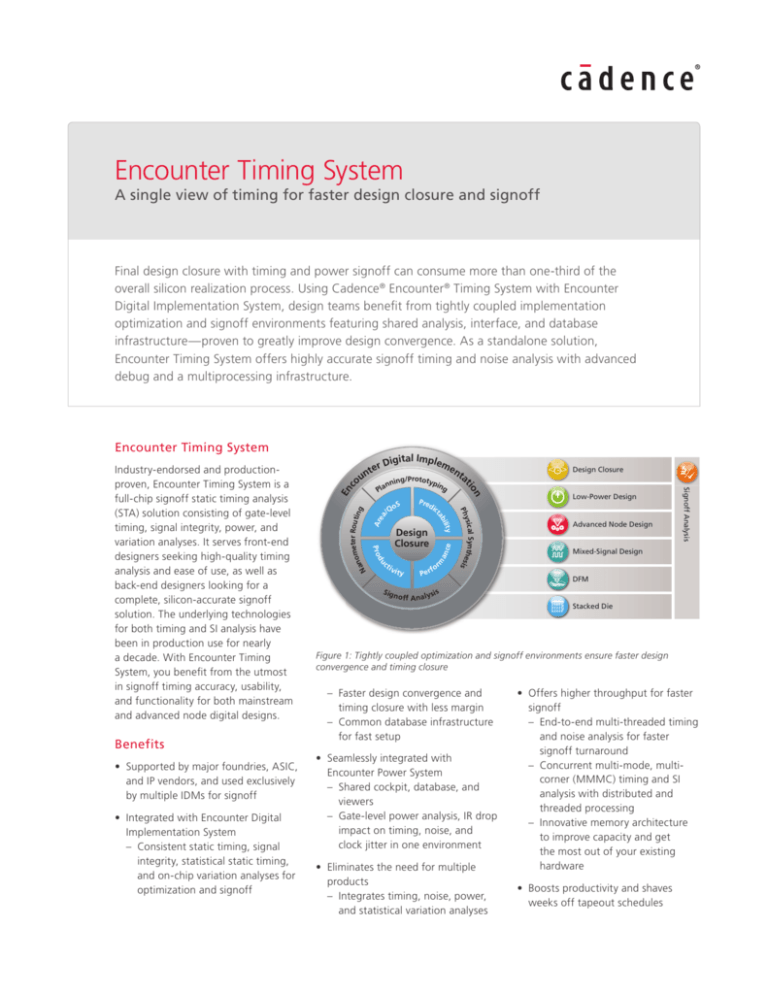

Figure 1: Tightly coupled optimization and signoff environments ensure faster design

convergence and timing closure

–– Faster design convergence and

timing closure with less margin

–– Common database infrastructure

for fast setup

• Seamlessly integrated with

Encounter Power System

–– Shared cockpit, database, and

viewers

–– Gate-level power analysis, IR drop

impact on timing, noise, and

clock jitter in one environment

• Eliminates the need for multiple

products

–– Integrates timing, noise, power,

and statistical variation analyses

• Offers higher throughput for faster

signoff

–– End-to-end multi-threaded timing

and noise analysis for faster

signoff turnaround

–– Concurrent multi-mode, multicorner (MMMC) timing and SI

analysis with distributed and

threaded processing

–– Innovative memory architecture

to improve capacity and get

the most out of your existing

hardware

• Boosts productivity and shaves

weeks off tapeout schedules

Encounter Timing System

–– Industry-renowned global timing

debug accelerates root-cause and

bottleneck analysis

–– MMMC-aware debug quickly tracks

down timing problems across all

modes

–– MMMC- and SI-aware incremental

engineering change orders

–– Advanced analysis algorithms to

reduce false SI failures by 10x

• Unmatched signoff accuracy

–– Prevents the excessive overdesign

that saps performance, power, and

die area

–– Delivers accurate delay calculation to

within 2% of SPICE

–– Leverages current source models for

greater accuracy with advanced node

designs

–– Offers built-in critical path simulation

for delay/SI correlation with SPICE

Features

Encounter Timing System provides a

comprehensive signoff verification

solution that combines static timing

analysis (STA), accurate delay calculation, crosstalk noise analysis, advanced

modeling, and global timing debug.

It helps you achieve first-pass silicon

success and fast time to market on their

multimillion-gate designs. Encounter

Timing System also supports incremental

engineering change orders (ECOs) and

“what-if” analysis, reducing runtimes for

minor design changes and thus improving

productivity.

Powerful GUI

• Command console with command

completion, history, and context

highlighting

• Timing constraint viewer to find

path-specific timing constraints based

on design object name or constraint

group type

• Schematic and layout viewers with the

ability to cross-probe from the timing

report

www.cadence.com

SDC

.lib

VCD

Spice

DEF + LEF

SPEF/SDF

Verilog

ECSM

Encounter

Timing

System

Power

Reports

SDF

SDF

DRVs

Figure 2: Encounter Timing System data flow and user interface

• Script editor for evaluating scripts

to enable cross link and expand Tcl

procedures

• Structural checks on timing paths to

identify potential issues

• Checks for missing or inconsistent

library and design data

Consistent, integrated STA for

optimization and signoff

Designers have traditionally relied on

one STA method for implementation

and another for signoff analysis. This

leads to corrective iterations with the

place-and-route system when discrepancies are found during signoff analysis.

Encounter Timing System is a consistent,

integrated STA environment for optimization during the place-and-route stage

and for final signoff verification. This gives

you the flexibility to use Encounter Timing

System as a standalone solution or as

part of the integrated Encounter Digital

Implementation System.

Global timing debug

With global timing debug, you can quickly

pinpoint the root cause of timing and

constraint problems. You can view the

slack histogram and generate detailed

timing views with individual cell/wire

delays, slack details, hierarchy allocations, and constraint cross-probing.

Global timing debug employs unique path

visualization capabilities to determine

a path’s cause of failure. Paths that

share a common failure mode can then

be categorized dynamically while the

debugging of “uncategorized” paths

continues. Path categories can be

visualized in the global timing context

to determine which categories can be

“fixed” in parallel and which ones should

be fixed first. This reduces iterations to

timing closure by intelligent debugging

more than just the worst path.

Global clock debug

With global timing debug, you can quickly

pinpoint the root cause of timing and

constraint problems. You can view the

slack histogram and generate detailed

timing views with individual cell/wire

delays, slack details, hierarchy allocations, and constraint cross-probing.

Global timing debug employs unique path

visualization capabilities to determine

a path’s cause of failure. Paths that

share a common failure mode can then

be categorized dynamically while the

debugging of “uncategorized” paths

continues. Path categories can be

visualized in the global timing context

to determine which categories can be

“fixed” in parallel and which ones should

be fixed first. This reduces iterations to

timing closure by intelligent debugging

more than just the worst path.

2

Encounter Timing System

Advanced nanometer electrical

analysis

Implementing multimillion-instance

nanometer designs requires very efficient

yet highly precise delay calculation.

Designers must also consider SI effects

such as IR drop and crosstalk, and

advanced low-power design techniques

that use multiple voltage levels and level

shifters. Delay calculation based on table

lookup or polynomial models are not

accurate enough for today’s nanometer

circuits. Encounter Timing System

supports the effective current source

model (ECSM), which enables accurate

prediction of actual silicon performance,

particularly for complex nets, long RC

networks, and multiple driver scenarios

(clock meshes).

Figure 3: Global timing debug

Global clock debug

Fast, Accurate Signoff

With global clock debug, you can see

the clock structure and quickly get to the

root of clock-related problems. You can

quickly determine if there are issues with

the specifications, clock re-convergence,

skew, transition time, or insertion delay—

and get relevant physical information

on how to fix them. You can display the

graphic structure of a large and complex

clock structure as needed, folding or

unfolding the clock tree at any stage

to tune into the relevant information,

without being overwhelmed by other

details.

Encounter Timing System offers accurate

analysis of signal integrity (SI) and IR drop

as well as its impact on both timing and

functionality. It builds on the strengths

of the customer-trusted, tapeout-proven

Cadence CeltIC® Nanometer Delay

Calculator (NDC) engine. And it employs

more accurate libraries (ECSM, cdB) to

analyze the complex effects of crosstalk

delay, noise (glitch), timing, and IR drop.

Accurate crosstalk analysis and faster

SI closure

Encounter Timing System calculates the

impact of crosstalk using a combination

of cell- and transistor-level models. For

noisy nets that exhibit the most non-linear

behavior, Encounter Timing System uses

an on-the-fly SPICE simulation engine

to accurately calculate noise-on-delay

effects. It also deploys the unique pathbased alignment (PBA) technique to

ensure realistic SI delay effects on critical

Interface to Encounter Conformal

Constraint Designer

A seamless interface between Encounter

Timing System and Encounter Conformal®

Constraint Designer enables advanced

constraint checking and critical false-path

analysis. Constraint checking eliminates

bad constraints that cause iterations,

longer design time, and silicon failure.

Critical false-path analysis greatly reduces

the need to manually remove false paths

from the critical paths. Removal of these

false paths eliminates unnecessary netlist

optimizations and can improve design

area and timing.

www.cadence.com

Figure 4: Global clock debug

3

Encounter Timing System

crosstalk failure. Encounter Timing System

accurately models the non-linear IR drop

impact and eliminates the inaccuracies of

the traditional linear K-factor approach.

It incorporates instance-based IR drop

data from Cadence VoltageStorm® Power

Verification to account for the effects of

static and dynamic IR drop on path delays

and SI.

Reported SI Violations

10000

90nm

130nm

65nm

45nm

# of Violations

1000

100

10

1

499k

39.5k

2.7M

810k

184k

1.3M

682k

ETS XL

Propagated

1

8

18

1

1

14

25

No

Propagation

29

49

496

272

5

31

4400

Figure 5: SI pessimism reduction and critical path simulation

timing paths. Without PBA, SI delay

calculation can create an unrealistic or

overly pessimistic worst-case path delay.

Further removal of path delay pessimism

is achieved through noise path pessimism

removal (NPPR), which finds the maximum

noise delay change for the overall critical

path instead of for each individual net on

that path.

Encounter Timing System also ensures

functional validity by performing glitch

noise propagation to register end points

and by ensuring that the register is not

driven unstable. These unique PBA,

NPPR, and glitch noise propagation

capabilities greatly reduce the number of

false crosstalk problems. This translates

into much less work for place-and-route

systems and significantly fewer SI closure

iterations.

Automated MMMC signoff and ECO

Encounter Timing System’s unique

multi-mode multi-corner (MMMC) infrastructure enables you to quickly analyze

and debug timing problems across all

modes and corners. It features concurrent

MMMC analysis with distributed and

threaded processing capability that

provides simplified management of

MMMC runs coupled with the highest

possible throughput. This is complemented by the MMMC-aware incremental engineering change order (ECO)

capability, which allows you to make an

ECO and see the effect on timing and

SI across all modes in a single session,

without running additional reports or

scripts.

www.cadence.com

Multi-processing architecture

Encounter Timing System utilizes both

threaded and distributed processing

to greatly improve overall signoff

turnaround. Through threaded timing and

SI analysis, you can gain up to four times

the performance over a single CPU run. In

addition to threading on a single machine,

Encounter Timing System includes MMMC

timing analysis and “superscaling”

SI analysis, which can be distributed

across multiple machines. By distributing different parts of a task between

two or more processors, Encounter

Timing System can significantly improve

turnaround time and handle larger, more

complex designs.

Unified power analysis

Encounter Timing System provides a

comprehensive static and dynamic

solution for cell-level power analysis by

combining timing and power analyses

in a single environment. This integrated

environment delivers faster results and

improves your productivity. Encounter

Timing System supports both vectored

and vectorless approaches to power

analysis. The vectorless approach enables

accurate power analysis early in the

design flow, while vectors are used to

achieve the highest accuracy.

Low-power–driven signoff

In smaller geometries, power supplies

are typically around 1 volt, and even

small voltage drops can compromise

signal timing and lead to chip failures.

IR drop further increases the risk of

Advanced low-power design techniques

such as multi-supply/multi-voltage

(MSMV) and dynamic voltage and

frequency scaling (DVFS) can introduce

errors and complicate the traditional

timing signoff flow. Encounter Timing

System enables a simple flow where you

can characterize just three libraries at

three voltage points, which are sufficient

to perform accurate non-linear delay

calculation across a much wider range of

voltage points. Encounter Timing System

also supports the Common Power Format

(CPF), which describes power intent

throughout the design flow from system

specification to tapeout.

Critical path simulation

Encounter Timing System enables on-thefly path simulation of critical paths and

offers a graphical view of the impact of

crosstalk and IR drop along the path,

including the propagation of non-linear

waveform effects. This enables easy

validation of timing, SI, and IR drop

effects—and verification of fixes—prior to

implementation.

Comprehensive variation support

At 65nm and below, process control

becomes very difficult. Manufacturing

variations result in deviations in electrical

behavior for devices and interconnect.

Traditionally, these variations have been

factored into the design flow by adding

bulk margin to the timing constraints or

libraries. But this practice can negate the

advantages gained from using smaller

process nodes over larger process nodes.

In addition, designs required only to

pass traditional signoff standards could

still fail in silicon if the corners are not

chosen properly.

4

Encounter Timing System

Encounter Timing System enables you

to properly analyze and account for

process variation without resorting to

excessive margins or overdesign to restore

predictability to the design flow. It offers

common-path pessimism removal (CPPR),

advanced on-chip variation analysis,

statistical static timing analysis (SSTA),

and statistical leakage and thermal

analyses to achieve maximum design

performance with minimum power

consumption at advanced process nodes.

These technologies help reduce the

design cycle with fewer timing runs and

help you tape out with greater confidence.

Location-based on-chip variation

Designers must address on-chip variation

(OCV) effects, including removal of

pessimism caused by common paths.

However, traditional OCV analysis is

inaccurate and overly pessimistic since

it employs a constant de-rating factor.

Encounter Timing System employs

location-based on-chip variation (LOCV),

which uses logic level, cell complexity,

and physical location to select the optimal

de-rating factors. LOCV helps eliminate

the excessive guardbanding associated

with traditional de-rating, and it improves

timing closure.

Statistical static timing analysis

Traditional STA accounts for process

variations by introducing more aggressive

gross guardbanding and by using multiple

analysis corners to model different

process and environmental variation

combinations. This corner-based approach

can be overly pessimistic since it reports

timing scenarios that have an extremely

small likelihood of occurring. Also, the

exponential growth in the number of

corner combinations with the increasing

number of parameters makes analysis on

every corner impractical.

Encounter Timing System supplements

traditional corner-based methods with

powerful and accurate statistical static

timing analysis (SSTA) that can account

for the process variability in a single run.

www.cadence.com

It uses advanced statistical ECSMs to

identify cells and nets on both clock and

data paths that are sensitive to variations. It also determines the probability

of timing failure over the full range of

process variation. These features reduce

both pessimism and guardbanding,

resulting in decreased area and power

consumption while improving chip performance. Encounter Timing System lets

you explore potential tradeoffs between

parametric yield and clock speed.

and introduce timing failures across the

die. Simply applying more guardbanding

to your design to account for this variation

can negatively affect chip performance.

Encounter Timing System includes a

powerful thermal analysis engine that

takes chip packaging into account and

provides an accurate thermal map and

per-instance temperature. This reduces

the need for more guardbanding and

enables you to target thermal hotspots

more effectively.

Encounter Timing System SSTA features

include:

Statistical leakage power analysis

• Within-the-die, die-to-die, and random

variation support

• Block-based and path-based modes

• Crosstalk noise impact

• Standardized statistical ECSM library

models and characterization support

• Consistency and integration with

Encounter Digital Implementation

System to fix variation problems

automatically

Thermal analysis

Designers targeting advanced node

processes are quickly discovering that

on-chip thermal variation can no longer

be ignored. Thermal impact at smaller

process nodes can affect leakage power

At smaller process geometries, leakage

power begins to dominate the power

consumed by CMOS devices. Accurate

analysis of device leakage is paramount

to achieving a power-efficient design.

Existing leakage power analysis

techniques use a pessimistic worst-case

approach, which is ineffective. Since cell

leakage has an exponential response to

process variation (that is, a small change

in process variation causes a major shift

in transistor leakage), the probability

of the extreme worst case occurring in

real silicon is very small. This leads to

aggressive over-design, overcompensation

for IR drop, and potentially unnecessary

architectural changes. The solution is to

model the leakage power as a statistical

probability to avoid designing to the

worst-case limit.

SDC

Spice

.lib

VCD

SPDF

DEF + LEF

SPEF/SDF

Verilog

S-ECSM

Encounter

Timing

System

Power

Reports

SDF

Statistical

Reports

DRVs

Figure 6: SSTA data flow

5

Encounter Timing System

The statistical leakage power analysis

(SLPA) of Encounter Timing System helps

you target a smaller, more reasonable

leakage number. This number reported by

statistical analysis can be as much as 40%

smaller than that of traditional worst-case

leakage power analysis. Using advanced

statistical ECSMs, Encounter Timing

System can model the following:

• State-dependent exponential leakage

power variation with respect to process

parameters

SLPA

Spice Monte Carlo

3 -s igma L eakage

(99.7% confidenc e)

Up to 200% Difference

0

15000

25000

35000

45000

55000

Leakage (nW)

• Die-to-die, within-the-die (spatially

correlated), and random variation

Platforms

Figure 7: Statistical leakage power distribution

• Linux: 32-bit, 64-bit

Packaging

• Sun Solaris: 64-bit

Encounter Timing System is available in L

and XL base licenses with an Advanced

Analysis GXL Option.

• IBM AIX: 64-bit

Standard Interface Support

Cadence Services and Support

• Inputs

–– Verilog, .lib, SDC, SDF, SPEF, Tcl

–– Optional: ECSM, cdB, DEF, CPF, OA,

VCD, OCV

–– SSTA: Statistical ECSM (S-ECSM),

Statistical SPEF (S-SPEF), Statistical

Parameter Distribution File (SPDF)

• Cadence application engineers can

answer your technical questions by

telephone, email, or Internet—they can

also provide technical assistance and

custom training

• Outputs

–– Timing reports, SDF, DRV report,

power reports

Worst-Case

L eakage

• More than 25 Internet Learning

Series (iLS) online courses allow you

the flexibility of training at your own

computer via the Internet

• Cadence Online Support gives you 24x7

online access to a knowledge base of

the latest solutions, technical documentation, software downloads, and more

• Cadence certified instructors teach

more than 70 courses and bring

their real-world experience into the

classroom

Cadence is transforming the global electronics industry through a vision called EDA360.

With an application-driven approach to design, our software, hardware, IP, and services help

customers realize silicon, SoCs, and complete systems efficiently and profitably. www.cadence.com

© 2011 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, CelHC, Conformal, Encounter, and VoltageStorm are

registered trademarks of Cadence Design Systems, Inc. All others are properties of their respective holders.

21298 09/11 KM/DM/PDF