EE130: Integrated Circuit Devices

advertisement

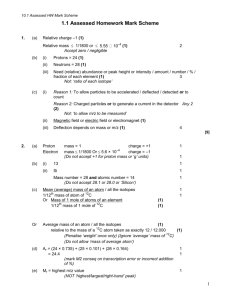

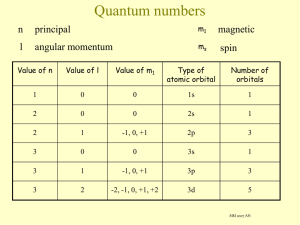

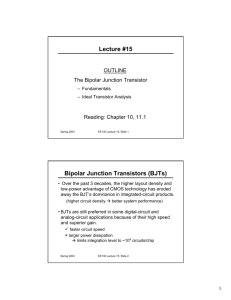

EE130: Integrated Circuit Devices Instructor: Prof. Tsu-Jae King (tking@eecs.berkeley.edu) TA’s: Mohan Dunga (dunga@eecs.berkeley.edu) Kenny Zhang (zhangjh@eecs.berkeley.edu) Web page: Newsgroup: http://www-inst.eecs.berkeley.edu/~ee130/ ucb.class.ee130 Schedule Lectures (247 Cory?): TuTh 3:30-5:00 PM Discussion Sections: – – – – Section 101 (241 Cory): Section 102 (289 Cory): Section 103 (285 Cory): Section 104 (203 McLaughlin): Mo 3-4 PM; Mohan Dunga We 4-5 PM; Kenny Zhang Fr 10-11 AM; Kenny Zhang Tu 5-6 PM; Mohan Dunga ** SECTIONS WILL BEGIN ON FRIDAY, AUGUST 31st ** • Office Hours: – T.-J. King (567 Cory): – M. Dunga (278 Cory): – K. Zhang (278 Cory): Fall 2001 Tu 12-1 PM & We 5-6 PM TuTh 10-11 AM MoWe 11AM-12PM EE130, Lecture 1 2 Relation to Other Courses • Prerequisite: – EECS40: Simple pn-junction and MOSFET theory; MOSFET circuit applications; basic microfabrication technology – Familiarity with the Bohr atomic model • Relation to other courses: – EE130 is a prerequisite for the following courses: • EE131: Semiconductor Electronics (may be taken concurrently) • EE231: Solid State Devices – EE130 is also helpful (but not required) for IC analysis and design courses such as EE140 and EE141, as well as for the microfabrication technology course EE143 Fall 2001 EE130, Lecture 1 3 Reading Material • Primary Text: Semiconductor Device Fundamentals by R. F. Pierret (Addison Wesley, 1996) • Reference Texts: Solid State Electronic Devices by B. G. Streetman, S. Banerjee (Prentice Hall, 2000) Device Electronics for Integrated Circuits by R. Muller, T. Kamins (Wiley & Sons, 1986) • EE130 Course Reader: - available at Copy Central (2483 Hearst Ave) - contains sample HW, quizzes, exams; supplementary reading Fall 2001 EE130, Lecture 1 4 Grading – Homework • due Th (beginning of class) • late homeworks not accepted 10% Letter grades will be assigned based approximately on the following scale: – Mid-term design project • due on November 20th • You may work in pairs 20% – 6 quizzes • ~25 minutes each • open book and notes • no make-up quizzes 30% – Final exam • 12/19 from 12:30-3:30PM • bring calculator • open book and notes Fall 2001 EE130, Lecture 1 40% A+: 95-100 A: 85-95 A-: 83-85 B+: 80-83 B: 70-80 B-: 67-70 C+: 65-67 C: 55-65 C-: 53-55 D: 40-53 F: <40 5 Schedule Week 1 2 3 4 5 6 Dates 8/28, 8/30 9/4, 9/6 9/11,9/13 9/18^, 9/20 9/25, 9/27 10/2^, 10/4 Topics Semiconductor Fundamentals: intro., carrier modeling … carrier properties, distributions, and concentrations ... carrier action Metal-Semiconductor Contacts and Schottky Diodes pn Junction Diode: electrostatics ... I-V characteristics Chapter 1&2 2 3 14 5 6 7 19/9, 10/11 8 10/16, 10/18 9 10/23^, 10/25 10 10/30, 11/1 11 11/6^, 11/8 ... junction capacitance, transient response Bipolar Junction Transistor: structure and operation ... BJT static characteristics ... BJT dynamic performance Metal-Oxide-Semiconductor Capacitor 7&8 10 11 12 16 12 11/13, 11/15 13 11/20* MOS Field-Effect Transistor: structure and operation … I-V characteristics (Thanksgiving Holiday 11/22) ... performance limitations … Advanced transistor structures; Review FINAL EXAM: Wednesday, 12/19 12:30 - 3:30 PM 14 11/27^ - 11/29 15 12/4^, 12/6 *Design Project Due Fall 2001 17 18 19 ^Quiz date EE130, Lecture 1 6 Introduction Integrated-Circuit Devices History: Source: Mark Bohr, Intel Corporation Fall 2001 EE130, Lecture 1 8 Planar Process Technology Source: Mark Bohr, Intel Corporation Fall 2001 EE130, Lecture 1 9 IC Technology Advancement Rapid advances in IC technology have been achieved primarily by scaling down transistor lateral dimensions: Source: Mark Bohr, Intel Corporation Fall 2001 EE130, Lecture 1 10 Benefit of Transistor Scaling “Moore’s Law” # transistors/chip doubles every 1.5 to 2 years 1,000,000,000 100,000,000 10,000,000 1,000,000 100,000 10,000 1970 Fall 2001 1980 1990 2000 EE130, Lecture 1 1,000 2010 11 Example: Microprocessor Evolution Generation: 1.5µ 1.0µ 0.8µ 0.6µ 0.35µ 0.25µ Intel386™ DX Processor Intel486™ DX Processor Pentium® Processor Pentium® II Processor Fall 2001 EE130, Lecture 1 12 Miniaturization => Market growth Technology Scaling Investment Better Performance/Cost Market Growth Courtesy Prof. Chenming Hu (Sources: VLSI Research Inc.; United Nation yearbook; World Bank Database; IMF) Fall 2001 EE130, Lecture 1 13 Si MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor: Gate Source Drain Substrate Desired characteristics: • High ON current (Idsat) • Low OFF current Fall 2001 EE130, Lecture 1 14 Semiconductor Fundamentals (Textbook Chapter 1) What is a Semiconductor? • Low resistivity => “conductor” • High resistivity => “insulator” • Intermediate resistivity => “semiconductor” – conductivity lies between that of conductors and insulators – generally crystalline in structure for IC devices • In recent years, non-crystalline semiconductors have become commercially very important polycrystalline amorphous crystalline Fall 2001 EE130, Lecture 1 16 Semiconductor Materials Elemental: Compound: Alloy: Fall 2001 EE130, Lecture 1 17 Silicon Crystal Structure • Unit cell of silicon crystal is cubic • Each Si atom has 4 nearest neighbors 5.43 Å Fall 2001 EE130, Lecture 1 18 Compound Semiconductors 3-D model 2-D model Ga As Ga As Ga As Ga As Ga As Ga • GaAs has the same crystal structure as Si • III-V compound semiconductors: GaAs, GaP, GaN, etc. ü important for optoelectronics Fall 2001 EE130, Lecture 1 19 How Many Silicon Atoms per cm-3? • Number of atoms in a unit cell: • 4 atoms completely inside cell • Each of the 8 atoms on corners are shared among cells à count as 1 atom inside cell • Each of the 6 atoms on the faces are shared among 2 cells à count as 3 atoms inside cell ⇒ Total number inside the cell = 4 + 1 + 3 = 8 • Cell volume: (.543 nm)3 = 1.6 x 10-22 cm3 • Density of silicon atoms = (8 atoms) / (cell volume) = 5 x 1022 cm-3 Fall 2001 EE130, Lecture 1 20 Crystallographic Planes and Si Wafers z z z y x (100) plane y y x x (111) plane (011) plane (100) plane (011) flat Fall 2001 EE130, Lecture 1 • The standard notation for crystal planes is based on the cubic unit cell • Silicon wafers are usually cut along the (100) plane with a flat or notch to orient the wafer during IC fabrication 21 From Hydrogen to Silicon # of Electrons 1 2 3 Z Name 1s 2s 2p 3s 3p 3d Fall 2001 Notation 1 1H 1 1s 2 He 2 1s2 3 Li 2 1 1s2 2s1 4 Be 2 2 1s2 2s2 5B 2 2 1 1s2 2s2 2p1 6C 2 2 2 1s2 2s2 2p2 7N 2 2 3 1s2 2s2 2p3 8O 2 2 4 1s2 2s2 2p4 9F 2 2 5 1s2 2s2 2p5 10 Ne 2 2 6 1s2 2s2 2p6 11 Na 2 2 6 1 1s2 2s2 2p6 3s1 12 Mg 2 2 6 2 1s2 2s2 2p6 3s2 13 Al 2 2 6 2 1 1s2 2s2 2p6 3s2 3p1 14 Si 2 2 6 2 2 1s2 2s2 2p6 3s2 3p2 15 P 2 2 6 2 3 1s2 2s2 2p6 3s2 3p3 16 S 2 2 6 2 4 1s2 2s2 2p6 3s2 3p4 17 Cl 2 2 6 2 5 1s2 2s2 2p6 3s2 3p5 18 Ar 2 2 6 2 6 1s2 2s2 2p6 3s2 3p6 EE130, Lecture 1 22 Bond Model of Electrons and Holes 2-D representation: When an electron breaks loose and becomes a conduction electron, a hole is also created. Fall 2001 EE130, Lecture 1 Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si 23 What is a Hole? • Mobile positive charge associated with a half-filled covalent bond – Treat as positively charged mobile particle in the semiconductor • Fluid analogy: Fall 2001 EE130, Lecture 1 24 Holes as Positive Mobile Charge Fall 2001 EE130, Lecture 1 25 Intrinsic Si Fall 2001 EE130, Lecture 1 26