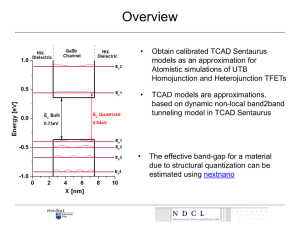

Low-power tunnel field effect transistors using mixed As and

advertisement