Εργασία 1

advertisement

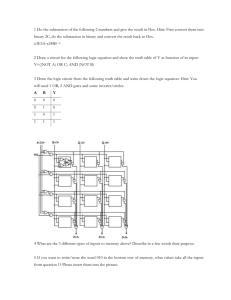

Psifiak Exercises - Series I: Adders, Subtracters, Encoders, Decoders Exercise 1 Design a digital circuit, which implements the addition of two binary numbers with 4 bits length, which are XS3 encoded. The result of the addition must be also a binary number with 4 bits length and XS3 encoded. You must design the previously described circuit by following the next steps: 1. Design a digital circuit, which converts a binary number with 4 bits length and XS3 encoded to a regular binary number with 4 bits length. (The circuit must have 4 inputs: a0, a1, a2, a3 and 4 outputs: b0, b1, b2, b3) 2. Design a digital circuit, which implements the full addition of two binary numbers with 1 bit length. (The circuit must have 3 inputs: carry, a0, b0 and 2 outputs: s0, carry) 3. Design the digital circuit, which implements the full addition of two binary numbers with 2 bits length, by using the circuit of the step 2. (The circuit must have 5 inputs: carry, a0, b0, a1, b1 and 3 outputs: s0, s1, carry) 4. Design the digital circuit, which implements the full addition of two binary numbers with 4 bits length, by using the circuit of the step 3. (The circuit must have 9 inputs: carry, a0, b0, a1, b1, a2, b2, a3, b3 and 5 outputs: s0, s1, s2, s3, carry) 5. Design a digital circuit, which converts a regular binary number with 4 bits length to an XS3 encoded binary number with 4 bits length. (The circuit must have 5 inputs: s0, s1, s2, s3, carry and 5 outputs: x0, x1, x2, x3, error) 6. Design the total digital circuit of Exercise 1 by using the circuits of the steps1, 4 and 5. (The circuit must have 8 inputs: a0, b0, a1, b1, a2, b2, a3, b3 and 5 outputs: s0, s1, s2, s3, error) Restrictions and other notes: The circuits of the steps 1, 2 and 5 must be designed by using AND-OR implementation (3 columns of gates 1st=NOT, 2nd=AND, 3rd=OR) and must be as simple as possible by using the CARNAHG simplifying method. The outputs of these 3 circuits must have a total delay of 3 time periods. The symbols aN, bN, sN, xN, where Ν=0, 1, 2, 3 denote the N-th bit (where 0 is the least important bit) of the binary numbers a, b, s, x respectively. Example: a = 1310 = 11012 where a3=1, a2=1, a1=0, a0=1. All circuits must be designed and simulated by using the Psifiak application. You can download it from the web-page: www.psifiak.8m.com. There is Tutorial and Help index available. Must be handed: For every circuit a PSF file (for a total of 6 files) and one library file, which will contain all the designed circuits. Finally the simulation results of the total circuit must be saved in HTML format and must also be handed out. (Totall: 6 PSF files, 1 LIB file and 1 HTML file) The solution of the above exercise is available from www.psifiak.8m.com For questions contact: Angelos Barmpoutis, Psifiak Administrator angelbar@csd.auth.gr Psifiak: Free Academic Digital Circuit Designer and Simulator - www.psifiak.8m.com Exercise 2 Design a digital circuit, which is similar to the circuit of exercise 1, and the only difference is that it implements subtraction instead of addition. Exercise 3 Design a digital circuit, which is similar to the circuit of exercise 1, and the only difference is that it uses Gray encoded numbers instead of XS3 encoded numbers. Exercise 4 Design a digital circuit, which is similar to the circuit of exercise 1, and the differences are that it implements subtraction instead of addition and uses Gray encoded numbers instead of XS3 encoded numbers. Exercise 5 Design a digital circuit, which is similar to the circuit of exercise 1, and the only difference is that it uses BCD 4221 encoded numbers instead of XS3 encoded numbers. Exercise 6 Design a digital circuit, which is similar to the circuit of exercise 1, and the differences are that it implements subtraction instead of addition and uses BCD 4221 encoded numbers instead of XS3 encoded numbers. Other suggested type of circuits for implementation: Carry prediction units Circuit for both Addition and Subtraction (choose operation by using a flag bit) Multiplexers De-multiplexers