Simultaneous Capacitance Voltage (CV) Measurement

advertisement

Simultaneous Capacitance Voltage (CV) Measurement

FACULTY OF ENGINEERING

LAB SHEET

ENT 3036 SEMICONDUCTOR

DEVICES

TRIMESTER 2 2010-2011

SD2 – C-V MEASUREMENT OF MOS CAPACITOR

*Note: On-the-spot evaluation may be carried out during or at the end of the experiment.

Students are advised to read through this lab sheet before doing experiment. Your

performance, teamwork effort, and learning attitude will count towards the marks.

Page 1 / 17

Simultaneous Capacitance Voltage (CV) Measurement

1. Introduction

1.1 What is Capacitance Voltage (CV) Measurement

It is the measurement of device capacitance against a sweep voltage

The capacitance of the device is measured at quasistatic (very low frequency of mHz) and high

frequencies (either 100kHz or 1MHz)

Best measurement results are obtained from measuring both low and high frequencies

simultaneously

Measured data is used as information of device characterization and process adopted

1.2 MIS Capacitor

Base on Metal Insulator Semiconductor structure

Most common is Metal (Polysilicon), Oxide-Semiconductor Capacitor (MOSCAP)

Devices can be transistors (MOSFET), P-N junctions or Schottky diodes

1.3 Why MIS Capacitor?

Simple structure, easy to fabricate

Readily integrate into process

Similar to MOSFET structure, just add Source and Drain

1.4 Objectives:

1. To investigate the effect of low and high frequencies on the operating modes of a MOS capacitor

2. To analyse the device parameters of a MOS capacitor from C-V measurement

2. CV Measurement System

2.1 Keithley 82-WIN CV System

The Keithley model 82-WIN Simultaneous CV System consists of the following components:

Keithley model 590 / 100k /1M CV Analyzer

o Source a high frequency of 100 kHz or 1 MHz selectable signal to the Device Under Test (DUT)

and measures the Capacitance, termed as CH.

Keithley model 595 Quasi-static CV Meter

o Keithley model 595 Quasi-static CV Meter

o Source a low frequency (almost DC Voltage) signal to the DUT and measures the Capacitance,

termed as CQ.

o Provides the step voltage (max. of 40 V range) for simultaneous CV measurement

o Measures the leakage current through the DUT, (Q/t).

o Provides triggering to Keithley model 590 / 100k / 1M CV Analyzer

Keithley model 230-1 Programmable Voltage Source

o Provides a DC offset bias voltage of +/- 100 V

Keithley model 5951 Remote Coupler

Page 2 / 17

Simultaneous Capacitance Voltage (CV) Measurement

o Consists of tuned and resonant circuits to separate the low and high frequencies for

simultaneous CV measurements. Ensures minimal interaction between instruments when

performing measurement

o Acts as the interface to connect between DUT and instruments for simultaneous CV

measurement

Metrics Interactive Characterization Software (ICS)

o Software control of instrument interface, data acquisition and analysis and test setup

System Controller

o Installed with General Purpose Interface Bus (GPIB) conforming to IEEE488.2 for

communication between Software and instruments

2.2 Hardware Connection Diagram

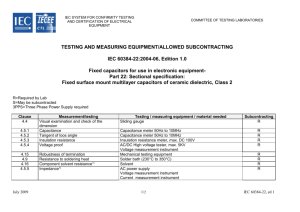

Figure 2.2 shows the cable connection between the instruments.

Note: All connections to the model 5951 Remote Input Coupler are to use Keithley model

4801 low noise co-axial cables. Failure to comply with this will result in unreliable data

measurement.

Figure 2.2

2.3 GPIB Address of Instruments

Page 3 / 17

Simultaneous Capacitance Voltage (CV) Measurement

The GPIB addresses of the instruments are to be set as follow:

Keithley model 590: Address 15

Keithley model 595: Address 28

Keithley model 230: Address 13

Please ensure that the addresses of the hardware and software are the same settings.

3. Typical CV Measurement Characteristic

Two Curves

o Quasistatic CV (low frequency)

o High Frequency CV (100kHz or 1MHz)

Figure 3.0 shows a typical simultaneous CV measurement for a p-type semiconductor of a MOS-CAP

structure

Figure 3.0: Typical Simultaneous CV (p-type)

3.1 Fundamentals of CV Measurement

A typical CV measurement will consists of three regions:

Accumulation region

In the accumulation region, the majority carriers will accumulate near the semiconductor surface.

Capacitance = Oxide Capacitance, Cox

Figure 3.1.1: Accumulation (p-type)

Depletion region

Page 4 / 17

Simultaneous Capacitance Voltage (CV) Measurement

When the device starts to deplete, the majority carriers will be push away from the semiconductor

surface. Separation of High and Low Frequency begins to take place due to generation of minority

carriers and Interface Traps.

Capacitance = Oxide Capacitance, Cox and Depletion Layer Capacitance in series

Figure 3.1.2: Depletion (p-type).

Inversion region

During Inversion, minority carriers will be generated and dominant near the semiconductor surface.

Semiconductor Surface Charge is inverted. Minority carriers do not respond to high frequency stimulus

and generation are relatively slow.

Capacitance = Oxide Capacitance and Maximum Depletion Layer Capacitance in Series.

(For High Frequency Only)

Low Frequency Capacitance = Oxide Capacitance

Figure 3.1.3: Inversion (p-type).

3.2 Characteristic of CV

Page 5 / 17

Simultaneous Capacitance Voltage (CV) Measurement

Figure 3.2.1 shows a typical CV characteristic of p-type MOS-CAP (MOS-C) while Figure 3.2.2 is that

of an n-type MOS-CAP.

Figure 3.2.1: p-type material

Figure 3.2.2: n-type material

Oxide Capacitance, Thickness and Gate Area

The oxide capacitance, Cox is the high frequency capacitance with the device biased in strong

accumulation. Oxide Thickness, Tox is calculated from Cox and the gate area as follows:

Tox= Aox / Cox

EQ (3.2.1)

Where: Tox is the Oxide Thickness in nm

A is the Gate Area in cm2

ox is permittivity of oxide material in F/cm (3.4 E-13)

Cox is oxide capacitance in F

Note: ox and other constants are initialized for use with silicon substrate, silicon dioxide

insulator and aluminum gate material, but may be changed for other materials.

Threshold Voltage

Page 6 / 17

Simultaneous Capacitance Voltage (CV) Measurement

The Threshold Voltage, VTH is obtained when the surface potential, S is twice that of the bulk potential,

B (Please refer to Figure 3.2.1 and 3.2.2). This corresponds to onset of strong inversion of MOS-CAP.

For an enhanced mode MOSFET, VTH correspond to the point where the device starts to conduct.

The VTH can be calculated from:

VTH = [ ± (A / Cox){(4Sq |Nbulk| |B|)} +2|B|] + VFB

EQ (3.2.2)

Where: A is the Gate Area in cm2

Cox is the oxide capacitance in Farads, F

S is the permittivity of substrate material (F/cm) [material constant=1.04E-12]

q is the electron charge of 1.60219 x 10-19 coul

B is the Bulk potential in V

Nbulk is the bulk doping concentration in cm-3

Flatband Voltage (VFB) and Capacitance (CFB)

The Keithley model 82-WIN uses the flatband capacitance, CFB method of finding flatband voltage, VFB.

The extrinsic debye length, is used to calculate the ideal value of flatband capacitance and can be

calculated as follow:

= (SkT / q2Nx)

EQ (3.2.3)

Where: kT is the thermal energy at room temperature (4.046E-21) in Joules, J

Q is the electron charge (1.60219E-19) in columbs, coul

Nx is N at 90% Wmax or NA or ND when input by user

N at 90% Wmax is chosen to represent the bulk doping

Once the value of CFB is known, the value of VFB is interpolated from the closest Vgs value. Based on

doping, the calculation of CFB uses N at 90% Wmax, or user-applied NA (bulk doping for p-type,

acceptors) or ND (bulk doping for n-type, donors) The Flatband capacitance is first calculated as follows:

CFB = (CoxSA / ) / (Cox + SA / )

EQ (3.2.4)

Where: A is the Gate Area in cm2

Cox is the oxide capacitance in Farads, F

S is the permittivity of substrate material (F/cm) [material constant=1.04E-12]

is the extrinsic debye length

At Flatband, surface potential is zero.

3.3 Doping Profile

Depletion Depth vs Gate Voltage

The doping profile is plotted as Depletion Depth vs Gate Voltage (Vgs). For the Keithley model 82-WIN,

the system computes the depletion depth, W from the high frequency capacitance and oxide

Page 7 / 17

Simultaneous Capacitance Voltage (CV) Measurement

capacitance at each measured value of Vgs. In order to graph this function, each W element needs to

be computed as follows:

W = AS [(1 / CH) – (1 / Cox)]

Where: W is the depletion depth expressed in um

S is the permittivity of substrate material, 1.04E-12 F/cm

CH is the high frequency capacitance in F

Cox is the oxide capacitance in F

A is the gate area in cm2

EQ (3.2.5)

Doping Concentration vs Depth

The doping profile of a device is derived from the CV curve based on the definition of the differential

capacitance (measured by Keithley models 590 CV Analyzer and 595 Quasistatic CV Meter) as the

differential change in depletion region charge produced by a differential change in gate voltage.

Standard Doping (N) vs Depletion Depth(W) does not compensate for onset of accumulation and is

accurate only when in depletion. In the Keithley model 82-WIN, in order to correct for errors caused by

interface traps, the error term [{1 – (CQ / Cox)} / {1 – (CH / Cox)}] is included in the calculations in the

extraction of the doping concentration and termed as Corrected Doping Concentration, NCORR.

The extraction of the concentration level will be extracted at 90% depletion depth.

3.4 Interface Trap Density

The Interface Trap Density, DIT is calculated from Interface Trap Capacitance, CIT as follows:

Thus from EQ (3.4.1)

CIT = [(1 / CQ) – (1 / Cox)]-1 – [(1 / CH) – (1 / Cox)]-1

EQ (3.4.1)

DIT = CIT / A

EQ (3.4.2)

Where: CIT is the Interface Trap Capacitance in F

DIT is the Interface Trap Density in cm-2 eV-1

CQ is the Quasistatic Capacitance in F

CH is the High frequency Capacitance in F

Cox is the Capacitance Oxide in F

A is the gate Area in cm2

4. CV Measurement Procedure

4.1 Equipment Requirement

Experiment Wafer and Wafer Map Sheet

Page 8 / 17

Simultaneous Capacitance Voltage (CV) Measurement

Keithley model 82-WIN Simultaneous CV Measurement System consisting of components as

listed in Section 2

MicroManipulator model S6-EVG probe station (vacuum type) with enclosure / light source

consisting of:

o 2 x co-axial manipulators / probes

o 1 x 6” chuck

Glove / Twister for Wafer handling

4.2 Connection

Please check the system connection with the diagram as in Figure 2.2. Once the connection is

established, power on the CV measurement system by pushing the power ON / OFF switch of the

respective instruments / equipments:

Keithley model 590 CV Analyzer

Keithley model 595 Quasistatic CV Meter

Keithley model 230-1 Programmable Voltage Source

The light source for MicroManipulator model S6-EVG probe station

Vacuum pump

4.3 Setup Procedure

Turn the vacuum switch to “OFF” position to disable the vacuum. (Switch is positioned on the right of

the chassis probe enclosure) Place the assigned experiment wafer on top of the chuck and turn “ON”

the vacuum switch. Ensure that the wafer is positioned properly on the chuck. Check the wafer map

sheet and select a appropriate site for your CV measurement from the listed wafer map sheet. Position

the tip of the probe that is connected to the OUTPUT of Keithley model 5951 (adjust using the X, Y

and Z-axis fine adjust) on the DOT wafer that CV measurement is to be performed. Ensure that the tips

are just contacting the DOT wafer and not scratching it. Similarly, position the tip of the probe that is

connected to the INPUT of Keithley model 5951 (adjust using X, Y and Z-axis fine adjust) on the top

surface of chuck. Once the probes are properly positioned to the DOT wafer, probe up again for both

left and right probes. (That is, the tips of the probe should not make contact with the DOT wafer or

chuck) Close the probe station enclosure.

4.4 Starting Metrics ICS and Setup of Experiment

Double-Click on the Metrics ICS icon

Measurement.

on the Desktop to execute Metrics ICS for CV

4.4.1 Selection of Experiment File

From the File Menu Options, Select “File Open”.

From the Attribute #1, Select “Expt” from the drop-down list and click “OK” when done.

The Project file that was opened will consist of the Setup for CV measurement for this

experiment.

Page 9 / 17

Simultaneous Capacitance Voltage (CV) Measurement

Figure 4.4.1A: File Open Select

Figure 4.4.1B shows the Project File named “Expt” of the CV measurement experiment

4.4.2 Loading of Calibration File Constant

From the icon option, click “Setup Editor”

From Setup Editor Menu, click “Opts” icon

Page 10 / 17

Simultaneous Capacitance Voltage (CV) Measurement

The KI82 options Setup Menu will be prompted

Figure 4.4.2: Setup Editor Menu

Select “Load cal….”

Select the most appropriate CAL file to use for the experiment. Please note that only

calibration constant files having the extension .CAL can be selected.

Once the appropriate calibration constant file is loaded, press “OK”.

Note: Calibration constant file is required to compensate for the High Frequency offset of the

connecting cables during measurement so as to obtain a more reliable and accurate

capacitance reading. Please check with relevant personnel on the correct calibration file

constant to be loaded.

4.4.3 Setup of Test Conditions for CV Measurement

From the Setup Editor (See Figure 4.4.2), click on the OUT instrument icon (That is connected

to the Gate,G Terminal), the Source Setup for KI82-WIN will appear as in Figure 4.4.3.

Depending on the wafer provided for the experiment, select an appropriate site for the CV

measurement that is listed on the wafer map sheet (As done in procedure 4.3).

From the wafer map sheet, check the Start and Stop Voltage of the wafer site selected and key

the respective values to the “Start V” and “Stop V” accordingly.

Select 20mV as the “Step V”

Select “Mode” to Single Stair

Select 100kHz for High Frequency Stimulus

Page 11 / 17

Simultaneous Capacitance Voltage (CV) Measurement

Figure 4.4.3: KI82-WIN Setup

Select “Delay” to be 0.1

From the Time measurement bias, set “Bias Voltage” equal to the voltage at “Start V”

Select Range of measurement for 590 to 2nF and 595 to 20nF

Check the “Leakage Correction” box

Select Filter to “3rdg”

Click “OK” When completed and return to Editor Setup Menu

4.4.4 Defining Pre-Stress Time

From the Editor Setup Menu, click on Time icon

to activate the Time

Parameter Setup Dialogue.

Check on the “Sec” box to select units of time measurement to be in seconds

Select “LIN” for Type to indicate a linear time measurement is preferred

On the “Wait” box, enter 30 (indicates 30 seconds of pre-stress time for device under test

before measurement will take place).

Press “Done” on the Setup Editor when completed and return to Data Sheet View.

Note: In CV measurement, a pre-stress time is allowed to bias the device to ascertain that the

device is in a state of equilibrium. That is the carriers are in the appropriate interface when

measurement is begin performed.

4.5 Performing CV Measurement

Page 12 / 17

Simultaneous Capacitance Voltage (CV) Measurement

Once the appropriate and necessary setup had been completed from procedures 4.1 to 4.4, CV

measurement can be made.

To perform CV measurement, select Measure icon

to activate the Measure Dialogue.

For CV measurement, select from the drop down list, “BIAS DELAY”. This will setup the CV

measurement to stress the device for 30 seconds at a voltage defined as in the Time Bias

Voltage

Ensure that both probes are not in contact with the wafer or chuck and close the probe shield

enclosure

Click on the ZERO CANCEL of the Measure Dialogue and follow the instructions as prompted.

This procedure is to offset any drift exhibit by the measuring system, interconnecting cables

and probes.

Figure 4.5: Measure Dialogue

Once the ZERO CANCEL had been completed, adjust the probes to contact the wafer and the

chuck according to procedure 4.3

Once the probes are in contact with the wafer, close the probe shield enclosure

Press on the “SINGLE” button of the Measure Dialogue to begin the CV Measurement

Once the CV measurement is completed, the results will be reflected in the Data Sheet View

4.6 Graph Plotting

Upon completion of the CV measurement, plot the following graphs:

Simultaneous CV measurements, VGS versus SIM CV (X-axis=VGS, Y1-axis=SIM CV)

Doping Concentration versus Depth (X-axis=DEPTHM, Y1-axis (log scale)=NCORR)

Interface Trap Density versus Trap Energy (X-axis=EIT, Y1-axis (log scale)=DIT)

Surface Potential versus Gate Voltage (X-axis=VGS, Y1-axis=PSISPSIO)

The graphs can be plotted as follows:

Click on the Plot View icon

Page 13 / 17

Simultaneous Capacitance Voltage (CV) Measurement

From the Plot View Setup Menu, select the appropriate measurement vectors from the drop

down list of Data Group for the respective axis

Ensure that selection of “Scale Type” for linear or Log scale is correct for each graph

Click “Apply” then “Done” when completed to exit from Plot View Setup

Figure 4.6: Plot View Setup Menu

4.7 Calculations and Extraction of CV Parameters

4.7.1 Minimum Capacitance, CH (min)

Extract the minimum High Frequency Capacitance from the CV plot

CH (min) = ____________ pF

4.7.2 Capacitance Oxide, Cox

Extract the Oxide Capacitance from the CV plot

Cox = _________________ nF

(Hint: Cox = Maximum Capacitance at High Frequency)

4.7.3 Oxide Thickness, Tox

Calculate the oxide thickness (Tox) from the given equation EQ (3.2.1)

Tox = __________________ nm

(Note: Please check the Area, A from the Wafer Map Sheet)

4.7.4 Depletion Depth, W

Find the maximum depletion depth, W(max) from Doping Concentration versus Depth graph or Data

View Spreadsheet and calculate depth at 90% level

W(max) = _________________ nm

W(90% ) = __________________ nm

Page 14 / 17

Simultaneous Capacitance Voltage (CV) Measurement

4.7.5 Doping Concentration, N

Given N90%W = 1.31 x 1013 cm-3

4.7.6 Extrinsic Debye Length,

Calculate the extrinsic debye length, using the equation as in EQ (3.2.3)

= _______________________ nm

4.7.7 FlatBand Capacitance, CFB

Calculate the FlatBand Capacitance, CFB using equation as in EQ (3.2.4)

CFB = _____________________ nF

4.7.8 FlatBand Voltage, VFB

Extract the Flatband Voltage, VFB at CFB from the CV graph or Data View Spreadsheet

VFB = _____________________ mV

4.7.9 Bulk Potential, B

Calculate the Bulk Potential, B given the following:

B = (kT / q) [ln (N90%W / i)]

Where: kT is the thermal energy at room temperature (4.046E-21) in Joules, J

q is the electron charge (1.60219E-19) in columbs, coul

N90%W is the calculated doping concentration at 90% depletion depth

i is the intrinsic carrier concentration (1.45E10) in cm-3

B = ______________________ mV

4.7.10 Threshold Voltage VTH

Calculate Threshold Voltage, VTH using the formula in EQ (3.2.2)

VTH = _____________________ V

Note: Nbulk to take at N90%W

5. Questions

5.1

What is the three basic schemes of a MOS-C operation? Draw diagram (CV

Characteristics) and use only 1 sentence to describe each schemes of a p-typed MOS-

Page 15 / 17

Simultaneous Capacitance Voltage (CV) Measurement

C operation, draw the CV diagram for n-type MOS-C operations also. Indicate the

flat band and strong inversion positions. (18 points)

Derive an expression for the potential distribution (W) in an ideal MOS-C in the

depletion condition in terms of the surface potential, E s and the depletion width, Wmax

at the surface taking the zero potential in silicon bulk. The silicon is p-doped type and

x=0 at the oxide-silicon interface. (14 points)

Note: please approximate the space charge and field gradient are constant and negative in the

silicon for (0 ≤ W ≤ Wmax).

5.2

5.3

A MOS-C is maintained at T=300K, oxide thickness WOX = 90nm, and the silicon

doping is NA=1.5x1015/cm3. Compute (assuming surface potential equals to bulk

potential, SF): (8 points)

a)

Fin kT/q units and in volts

b)

depletion width, Wmax

c)

Surface electric field (oxide-semiconductor) Es

Marking Scheme

Lab

(10%)

Assessment Components

Hands-On & Efforts (2%)

On the Spot Evaluation

(2%)

Lab Report

(6%)

Details

The hands-on capability of the students and their efforts during the

lab sessions will be assessed.

The students will be evaluated on the spot based on the lab

experiments and the observations on the capacitor characteristics.

Each student will have to submit his/her lab final report within 7

days of performing the lab experiment. The report should cover the

Page 16 / 17

Simultaneous Capacitance Voltage (CV) Measurement

followings:

1. Introduction, which includes background information on

metal oxide semiconductor capacitor.

2. Experimental section, which includes the general summary

of the lab experiment work.

3. Results and Discussions, which include the measured

results, analysis, and evaluations, with neat graphs/images

of the results and recorded data.

4. Conclusion, which includes a conclusion on the

experimental.

5. List of References, which includes all the technical

references cited throughout the entire lab report.

The report must have references taken from online scientific

journals (e.g. www.sciencedirect.com,

http://ieeexplore.ieee.org/xpl/periodicals.jsp,

http://www.aip.org/pubs/) and/or conference proceedings (e.g.

http://ieeexplore.ieee.org/xpl/conferences.jsp).

Format of references: The references to scientific journals and text

books should follow following standard format:

Examples:

[1] William K, Bunte E, Stiebig H, Knipp D, Influence of low

temperature thermal annealing on the performance of

microcrystalline silicon thin-film transistors, Journal of

Applied Physics, 2007, 101, p. 074503.

[2] Hodges DA, Jackson HG, Analysis and design of digital

integrated circuits, New York, McGraw-Hill Book Company,

1983, p. 76.

Reports must be typed and single-spaced, and adopt a 12-point

Times New Roman font for normal texts in the report.

Any student found plagiarizing their reports will have the

assessment marks for this component (6%) forfeited.

The lab report has to be submitted to the Electronics lab staff.

Please make sure you sign the student list for your submission. No

plagiarism is allowed. Though the electrical characteristics of the

measured capacitor from the same group can be similar, the report

write-up cannot be duplicated for group members. The individual

report has to be submitted within 7 days from the date of your lab

session. Late submission is strictly not allowed.

Page 17 / 17