A p-channel MOSFET with a heavily-doped p

advertisement

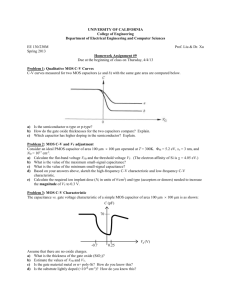

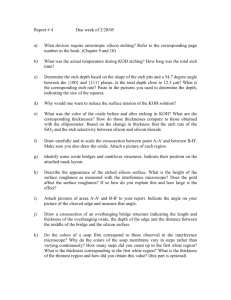

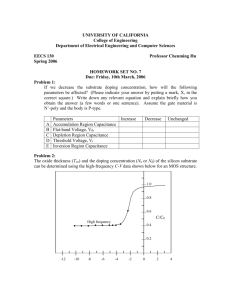

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences EE 130/230M Spring 2013 Prof. Liu & Dr. Xu Homework Assignment #9 Solution Problem 1: Qualitative MOS C-V Curves The C-V curves measured for two MOS capacitors (a and b) with the same gate area are compared below. a) Since more positive gate voltage results in decreased capacitance, the semiconductor surface is depleted for more positive gate voltage; therefore the semiconductor must be doped p-type, i.e. these are NMOS capacitors. b) The gate oxide thicknesses for the two capacitors are the same since they have the same value of maximum capacitance (Cmax = Cox). c) The minimum capacitance corresponds to the series combination of the oxide capacitance and the minimum depletion capacitance: Cmin = CoxCdep,min /(Cox+Cdep,min). For the same Cox (ref. part (b)) larger Cdep,min results in larger Cmin. Since capacitor a has larger Cmin, it has higher doping in the semiconductor. (The maximum depletion width WT is smaller and hence the minimum depletion capacitance Cdep,min = S/WT is larger, for a more heavily doped semiconductor.) Also, it can be seen that the threshold voltage VT (corresponding to the gate voltage at which the minimum capacitance is reached) is larger for capacitor a, which is also indicative of more heavily doped semiconductor. Problem 2: MOS C-V characteristic and VT adjustment For a PMOS capacitor of area 100 m 100 m operated at T = 300K, with M = 5.2 eV, xo = 3 nm, and ND = 1017 cm-3: The bulk potential, f F = - kT N D ln = -0.42V q ni The flatband voltage, VFB = F M - F S = F M - ( c + ( The oxide capacitance, Cox = eox xo = EG - f F )) = 5.2 - (4.05 + (0.56 - 0.42)) = 5.2 - (4.05 + 0.14) = 1.01V 2q 3.45 ´10-13 = 1.15 ´10 -6 F / cm 2 3´10 -7 The threshold voltage, VT = VFB + 2f F - 2qN De si | 2f F | Cox 2 ´1.6 ´10-19 ´10-12 ´1017 ´ 0.84 1.15´10-6 = 1.01- 0.84 - 0.143 = 0.027V = 1.01- 0.84 - a) The maximum small-signal capacitance, ACmax = ACox =10-4 ´1.15´10-6 =1.15´10-10 F b) The minimum small-signal capacitance, 1 1 2(2 | f F |) 1 2 ´ (2 ´ 0.42) 1 1 = + = + = + =11.1´10 6 cm 2 / F -6 -19 17 -12 -6 Cmin Cox qN De si 1.15´10 1.6 ´10 ´10 ´10 1.15´10 0.976 ´10 -7 Þ Cmin = 9 ´10-8 F / cm 2 Total minimum capacitance, ACmin = A ´ 9 ´10 -8 F / cm 2 = 10-4 cm 2 ´ 9 ´10 -8 F / cm 2 = 9 ´10 -12 F c) The high-frequency C-V characteristic and low-frequency C-V characteristic are sketched below. d) The threshold voltage must be shifted by -0.327V in order to become -0.3V: VT 0.3 0.027 0.327V | VT | qN I 1.6 10 19 N I 0.327V Cox 1.15 10 6 N I 2.35 1012 cm 2 In order to shift the threshold voltage to a more negative value (i.e. to make it more difficult to invert the surface to become p-type), donor atoms (e.g. phosphorus or arsenic) must be added. Problem 3: MOS C-V Characteristic Given the C-V characteristic for a MOS capacitor of area 100 um 100 um = 10-4 cm2: C (pF) 70 Vg (V) -0.7 0.25 a) The maximum capacitance is equal to the oxide capacitance ACox: Cox × A = Þ xo = eox A xo = 70 ´10-12 F 3.45´10 -13 ´10-4 = 4.9 ´10-7 cm = 4.9nm 70 ´10 -12 b) The steep transition from a minimum capacitance (corresponding to a depleted semiconductor surface) to a nearly maximum capacitance (corresponding to an inverted semiconductor surface) occurs as the gate voltage is increased in the positive direction; thus, the inversion layer is negatively charged and hence the semiconductor is p-type, i.e. this is an NMOS device. From the C-V curve it can be seen that the flatband voltage (at which the capacitance begins to decrease due to depletion of the semiconductor surface) is -0.7 V and the threshold voltage (at which the capacitance increases steeply) is 0.25 V. c) The decrease in capacitance with increasing gate voltage beyond the threshold voltage is characteristic of the gate depletion effect which increases the effective oxide thickness; therefore, the gate material is n-type polycrystalline silicon (poly-Si). Note: If the gate material were p+ poly-Si, then positive charge is added to the gate electrode as the gate voltage is increased, by increasing the number of holes in an accumulation layer at the oxide interface rather than by increasing the thickness of a depletion region with positive charge density as for an n+ poly-Si gate, so that there would be no gate depletion effect. d) Since (assuming no oxide charges) VFB= M−S= −0.7 V and M4.1 eV, we know thatS 4.8 eV. This corresponds to lightly doped p-type silicon. (The electron affinity of silicon is 4.05 eV so EF-Ev 4.05+1.124.8 = 0.37 eV 6×60 meV = 6× (kT/q)ln(10) so p is ~6 orders of magnitude smaller than Nv, i.e. p 1013 cm-3) Problem 4: Effect of Oxide Charge Charge within the oxide has greater impact on the threshold voltage when it is located closer to the semiconductor interface (at depth x closer to xo), which is why ox is weighted by x in the equation for the shift in VT: xo VT 1 SiO 2 x ox ( x)dx 0 a) Since the magnitude of the positive trapped oxide is equal to the magnitude of the negative oxide trapped charge, the charge that is located closer to the semiconductor interface (i.e. the negative trapped charge) will have greater impact and hence there will be a positive shift in VT. b) The applied gate bias is positive for NMOS and negative for PMOS. Therefore, the Na+ ions will drift toward the semiconductor interface in the NMOS device, whereas the Na+ ions will drift toward the gate interface in the PMOS device, and hence the Na+ ions will have a greater effect on VT for the NMOS device.