Circuit Extraction EECS 141 - University of California, Berkeley

advertisement

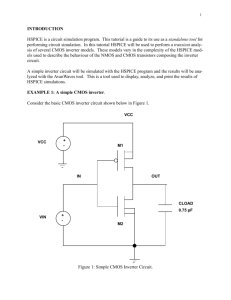

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on September 8, 2003 by Sean Kao (kaos@eecs.berkeley.edu) Borivoje Nikolic Lab #4: Circuit Extraction EECS 141 1. Objective The main objective of this lab is to familiarize you with the procedure to extract a SPICE netlist from Cadence and to prepare and analyze the simulation. 2. Tasks Part I:______________________________________________________________ a. Open the inverter layout in Cadence and extract the layout by clicking Verify -> Extract… on the menu. The extraction menu should come up and should look like the picture below. Make sure flat is selected from Extract Method. In the CIW there will be many commands, at the bottom there should “Total errors found: 0”. If you look in your Library Manager, there should be an additional view for your cell, extracted. b. Examine the extracted inverter view. There will be simple outlines designating different layers in the layout. The blue polygons are the metal 1 wires, green outlines represent active area, red strips are poly, and orange boxes represent contacts. You should also see large red boxes and bold white lines that stand out from the outlines. These are the ports of your devices and the nets that connect them. c. To netlist the extracted cell view, you will need to run Affirma Analog Environment by clicking on Tools -> Analog Environment. Analog Environment is a graphical interface for running and analyzing Spectre (a language similar to SPICE) simulations on circuits. You may find this tool useful for running analysis on your project. For now, we will use Analog Environment to generate SPICE netlists. In the Affirma Analog Circuit Design Environment window click Setup -> Environment…. In the window that opens select hspice from the Include/Stimulus File Syntax field and flat in the Netlist Type field, then click OK. Now go to Setup ->Simulator/Directory/Host…and change the Project Directory field to your lab directory then press OK. If you are prompted to save the state, go ahead press OK. Finally, click Simulation -> Netlist -> Create Final in Analog Environment. You will be able to see the netlist commands in the CIW and a “…successful” line then your netlist should open in a separate window. d. Now go back to your command line and in your lab directory go to CELLNAME/hspiceS/extracted/netlist where CELLNAME is the name of your cell. In that directory, your extracted netlist will be called hspiceFinal. Examine the netlist and you will see all the MOS transistors. Make sure the NMOS and PMOS have the correct width, length, drain and source area, and perimeters. e. We will not be using the NCSU model libraries, so comment out the lines: .lib "/ncsu/cadence/local/models/hspice/public/publicModel/tsmc25dP" PMOS .lib "/ncsu/cadence/local/models/hspice/public/publicModel/tsmc25dN" NMOS if they are present. Copy the EE141 spice model for TSMC 0.25 to the lab directory. > cp ~ee141/MODELS/g25.mod . Then add the line to reference the library, .lib ‘g25.mod’ TT for EE141 models. Change the NMOS and PMOS models from the “TSMC25DN” “TSMC25DP” to “NMOS” and “PMOS”, respectively. Finally comment out the Analog Artist options: .OPTION + f. INGOLD=2 ARTIST=2 PSF=2 PROBE=0 Simulate the extracted SPICE netlist to obtain the transient response and the DC transfer characteristics. Use Vdd = 2.5V. The netlist you obtain from extraction will only give you the two transistors. You will have to add the rest of the code for a simulation to run. Using your results, obtain the following: VOH, VOL, VIH, VIL, VM, NMH, NML from the VTC, and tplh and tphl from the transient analysis. *Turn in: Layout, extracted SPICE deck, edited SPICE deck, VTC and transient plots, and your calculated values. g. Add a 50fF load capacitor in your SPICE deck. Now resize your transistors so that the new circuit will have a transient response within 10% of the original. Modify your layout to reflect these changes, re-extract, and re-simulate. The book’s draft chapters offer methods by which the new dimensions can be determined. *Turn in: Your new layout, SPICE deck, transient plots, and your calculated tplh and tphl. Please qualitatively explain your reasoning for the transistor sizing, and hand in your hand analysis. Part II:______________________________________________________________ The following steps are in preparation to use the IRSIM switch level simulator, which will allow you get an idea of the functional operation of a circuit. You will use a script that converts the HSPICE netlist obtained in Part I to a .SIM format that can be used in IRSIM. . a. Extract the hspice netlist of the inverter created in Part I. Make sure that the extraction is flat and that no parasitics are extracted. Also, modify the net names for vdd, gnd, input and output. Call the input net in, output net out, vdd net vdd and ground net gnd. Look at the netlist and make sure that there are only transistors and that the net names are correct. There’s no need to modify anything else in the extracted netlist. b. Create a directory in your working directory called sim_netlist. Copy the extracted hspice netlist of the inverter to this directory and call it inverter.hsp. Copy the hspice to sim conversion script file to this directory. The script file is located at ~ee141/LAB5/hspice2sim Now you should have 2 files in the sim_netlist directory; hspice2sim and inverter.hsp c. Type the following command to convert the hspice netlist to the sim format. /usr/xpg4/bin/awk –f hspice2sim -v "l=0.12" "n=TSMC25DN" "p=TSMC25DP" inverter.hsp >! inverter.sim A file inverter.sim is created. Open up the file and look at the sim format. Check that the net names have been preserved. You can find more information regarding this format if you search Google for sim format. d. You do not need to run IRSIM for this lab as you will use IRSIM for the next lab. But for those who are curious, you can run IRSIM with the following command. /share/b/bin/irsim /share/b/cad/src/irsim/test-input/scmos60.prm inverter.sim More information on irsim can be found in http://bwrc.eecs.berkeley.edu/Classes/icbook/IRSIM/irsim.pdf 3. Report For your report, please hand in the following: Printouts of your schematics and layouts from Cadence Printouts of your SPICE input decks (extracted and edited) The manual calculations for the parameters determined in Part I. A comparison between your hand analysis and SPICE, along with an explanation of the differences. Qualitative reasoning and hand calculations used in your decision for the transistor sizing in Part I inverter.sim printout