Synchronous Sequential System

advertisement

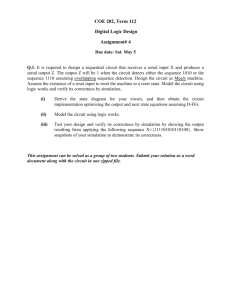

Synchronous Sequential System Design steps: 1) Generate a state diagram from problem statement. 2) Minimize the number of the states., “state reduction”. 3) Select a binary encoding for each state. --“state assignment” 4) Generate a binary encoded state table. 5) Generate next state Karnaugh maps for each memory device. 6) Select the type of the memory device to be used. 7) Generate a Karnaugh map for each memory device input using the associated next state Karnaugh map and the appropriate excitation truth table. Also generate a Karnaugh map for each output. 8) Generate minimized output and next state logic expressions. 9) Implement memory and combinational logic. 10) Document final design. Example : Derive the state diagram for a synchronous sequential circuit requiring to recognize the 4bit sequence 1101 and to produce an output of “1” whenever the sequence occurs in a continuous serial input. Re-used Example if input sequence is x = 010110110101 The o/p sequence is z = 000000100100 Time This specification assumes that after detecting the correct sequence the last “1” from the previously received sequence will be part of the new sequence Solution. We assume an initial state A where the circuit waits to receive the first input A At this state the circuit can receive a “1” or a “0” .There is no change in state if 0 is received (indicated by a self loop). If a “1” is applied, the circuit goes to a new state B with an output “0”. 1/0 A 0/0 B I f while in state B, a “1” is received ( ie. the sequence 11) The circuit changes to state C ; on the other hand, a “0” input takes the circuit back to state A. 0/0 0/0 1/0 A 1/0 B C When in state C, if a “1” is received the circuit remains in the same state. The circuit moves to a new state D if a “0” is applied. ( ie the sequence 110 is reached) 0/0 A 0/0 1/0 C B D 1/0 0/0 1/0 The next input will be the fourth bit of the 4-bit sequence; therefore the circuit must decide whether or not the sequence is the one to be recognized. If a “1” is applied, the sequence is correct and the circuit changes to B and gives the required output. However if a “0” is received when the circuit is in state D, it returns to state A to await the start of another sequence. 1/1 0/0 0/0 A 1/0 B 1/0 C 1/0 0/0 0/0 D Example : Derive the state diagram for a synchronous sequential circuit with one output zi. The output is the sum of the inputs. 2 inputs xi ,yi and Serial adder xi yi Xi= …. 010101001 Yi= …. 111011001 ----------------------------Zi=0 100000 010 Si 00/0 11/1 11/0 A 01,10 / 1 B 00/1 01,10 / 0 Input / Output XY / S We start at state A, where we assume it is the state of no Carry. At this state we examine the inputs possibilities of xy. For the 4 possible input combinations we determine whether we stay at the same state and produce an output or go to state B ( having a carry). In state B we again examine all possible inputs and decide where we would go and what output we will produce. For example if we are at state B with input 11, we have S=1 and C=1 therefore we stay at the same state and produce of output 1. Example 3: Derive the state diagram for a sequential circuit with the following specification: The circuit has one input and one output. The inputs arrive serially on the input line synchronized with the clock. The circuit is to examine the input data in consecutive sequence of 4-bits and generate a 1 if the 2 out of 4 bits are “1”. (only exactly 2 “1”s) A separate reset mechanism is used to reset the circuit. 2-out of 4 decoder xi Reset Z Xi= …. 0000 1010 1001 0111 1111 Zi= …. 0 1 1 0 0 --------------------------------------------- Example 4 Draw the state diagram for a circuit with the following specification: The circuit has one input and one output. The inputs are synchronized with the clock. The bits appear in descending order of significance. The output Z will be “1” the third input corresponding to the inputs “000” or “111”. A separate reset mechanism will reset the device.