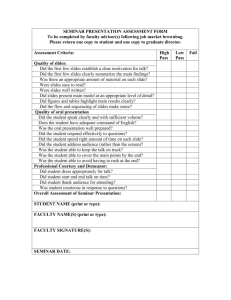

High Speed Brochure for printing

advertisement

High Speed Digital Design Seminar Locations throughout the United States plus at your site! Americom Seminars, Inc. 2533 No. Carson Street, Suite 4213 Carson City NV 89706 Control Clock Loading Eliminate Transmission Line Effects Solve signal integrity dilemmas Design High speed PCB right the first time Ensure your PCB meets your high speed requirements Learn how to avoid EMI/EMC problems Look inside! Send to: HIGH SPEED DIGITAL DESIGN SEMINAR Locations throughout the U.S. plus at your site! Increasingly fast microprocessors cause coupling, crosstalk, EMI and signal integrity dilemmas in today’s PCB designs. Attend this course to become skilled at the critical elements of proper design at CAE and CAD to control clock loading and eliminate transmission line effects; to select the tool set to ease the design process; and to recognize key aspects of the PCB including stack up, laminate choice, and embedded components. Share this with colleagues! Digital design engineers Design managers Test engineers EMI/EMC engineers IC digital logic designers Project managers of high-speed designs “Best short course I’ve ever taken. Instructor was very organized, knew the subject well, and creatively explained complex terms. Every aspect of the class was well thought out.” Have you thought this? “We have a problem with the layout of a board.” “My job requires more knowledge about high speed design.” “I have intuition about high speed issues but little solid knowledge.” “My company has high speed digital PCBs.” “Our customers use a high speed interface.” “We encounter signal integrity issues requiring high frequency solutions.” “I hope to learn valuable information quicker than I would on-the-job.” “The designs keep getting faster and faster.” Unlike other high-speed seminars, Mr. Hanson spends a full three days on central highspeed concerns plus a full day on related EMI-EMC issues. Mr. Hanson supplements Howard Johnson and Tim William’s texts with over 480 pages of notes. This is not cursory; this is in-depth. Robert Hanson teaches and consults for 3-Com, Advanced Fibre Communications, Alcatel, Allied Signal, Apple, AT&T, Boeing, Chrysler, Cisco, Compaq, Cray, da Vinci Systems, Data Device, Dell, Delphi, EDA Technologies--South Africa, Ford, Gateway, GE, Gen Rad, Honeywell, HP, IBM, Intel, Lockheed, Lucent, Marconi, Micron, Motorola, NEC, eLuminant, Nortel, Northrop Grumman, Panasonic, Qualcomm, Rockwell, Samsung-Korea, Solectron, Storage Tek, Sun, Tektronix, Teradyne, TI, TRW, Tycom Laboratories, U.S. Trade Commission, Xerox, and Xilinx Signal Integrity Demo Mr. Hanson spends time answering student questions so that you get the information you need. This course benefits you Observe demonstrations of high speed PCB simulation on a PC/overhead format on the second night of the seminar. This setting will provide an excellent opportunity for students to interchange ideas, problems, and solutions. Contingent on vendor availability. The speed of today’s logic devices mandates that the interconnects on PCBs must meet the high switching rise/fall times of these devices. Switching edges are in the 200ps to 300ps range and some devices have edges that have reached the 17ps barrier. This has resulted in high-speed design problems such as: A lack of control over impedance and reflections TAB :Mr. Hanson Crosstalk and bypassing failures shows polyimide Time delays, false triggering and reflections lead frame that provides low L and Failure to meet EMI and FCC requirements C is a good high It is the edge rate, not the frequency, which exacerbates this problem. So, speed device. even if your design is for moderate frequency, the edge rates can cause these designs to reflect the high-speed effects. Most designs today use a microprocessor and today’s micros have clock rates over 1000 times higher than the original 8 and 16 bit machines. A key factor is the minimization of the semiconductor device (now at .09 microns) leading to less parasitic L and C and thereby faster switching rates. This phenomenon is also apparent in RAMs, ROMs, ASICs and Gate Arrays. This leads to PCBs requiring terminators, new CAD routing disciplines, and component additions to minimize ground bounce effects. More and more designs are requiring these faster devices to meet more demanding specifications that match or beat the competition. The purpose of this course is to provide you with the knowledge to do it right the first time. The course provides tools for recognizing the problems with any proposed high-speed design. Design rules and design processes are taught that insure the PCB will function properly at the prototype stage. The course emphasizes cost competitive design without sacrificing high-speed integrity. Taught by an internationally recognized expert “Mr. Hanson is well spoken, patient, knowledgeable . . . gives practical examples.” “(I)nstructor’s presentation was superb. Very good job of connecting electronics to the real world.” “The course was excellent. Hanson demystified high speed.” Participants in Mr. Hanson’s courses Robert Hanson, MSEE, is President of Americom Seminars, Inc. As a digital design engineer at The Boeing Company, Rockwell, Honeywell, and Loral, Mr. Hanson designed and provided prototype operational analysis on many high-speed designs including PCBs for AWACS, B1-B, 747-400, missiles, and ground support test equipment. Mr. Hanson teaches high-speed digital design courses throughout the United States, Europe, South Africa, and Asia. He has presented electrical engineer courses at all Nepcon conferences, University of California–Berkeley, University of Wisconsin, University of Oxford-England, IPC, and SAE. He has also done on-site private consultations and training sessions for over eighty companies in the United States and internationally. Mr. Hanson does On-site Private Seminars as well. www.americomseminars.com HIGH SPEED COURSE OUTLINE This course is for anyone who has worked with today’s ICs, high-speed designs and PCB layouts. No advanced math is required though attendees will find it helpful to bring a scientific calculator to the course. The course is presented at a technical level that will provide experienced designers with information to design and layout a high speed PCB including designing so that it meets Signal Integrity (SI) & EMI. Fundamentals Transmission Lines Power Systems EMI-EMC Issues Frequency, Time and Distance Lumped Versus Distributed Systems Four Kinds of Reactance Ordinary and Mutual Capacitance & Inductance EM Fields Geometry, C, L, & Zo, interrelationships C & L Resonance The quality factor, Q, and why lumped circuits can ring and cause EMI. Infinite Uniform Transmission Line Effects of Source and Load Impedance Special Transmission Line Cases Determining Line Impedance & Propagation Delay using TDR and VNA Skin/proximity effect & Dielectric Loss The Capacitive Load - Zo and propagation delay Matching Z0 with trace alturations (neckdowns) – minimizing the C load 0 90 , 450 bends – are they concerns? Characteristics of T. lines: coax, pair, micro strip, buried micro strip, stripline & differential: asymmetric, dual, edge. Providing a stable Voltage Reference – Cu planes Distributing Uniform Voltage – Sense lines, bulk C and interplane C Choosing a Bypass Capacitor – Electrolytic/tantalum and ceramic Power plane resonance – serial and parallel, how to minimize both Designing a .1 ohm bypass system up to Fknee Designing for constant ESR IC die capacitance, discrete C in the IC package Why the 0201 – Both for better bypassing and EMI control Minimizing L-Capacitor layouts for SOICs, PLCCs, and various configurations of BGAs You’ll learn design considerations at both CAE and CAD to provide a compliant radiation/susceptibility product. You’ll examine and identify ways to prevent common EMI/EMC problems regarding power supplies, cables, connectors, slots, discontinuity of ground planes and antenna loops. Even/odd, differential/common modes are their effects on LVDS. Mutual and Series Inductance – How Connectors Create Crosstalk and EMI Using Connectors on a Multidrop Bus (Z mismatch reflection) and how to match Zc to Zo, Measuring Coupling in a Connector Continuity of Gnd Underneath a Connector Special Connectors for High-Speed requirements – Crosstalk and matching Zo Differential Signaling Through a Connector BGA: Mr. Hanson discusses how to route at CAE/CAD so that the balls can be paralleled to minimize L. The pads are NSMD and 8 mils vias are on stringers. If done right, this is a very good high-speed device. High-Speed Properties of Logic Gates Quiescent vs. Active Dissipation Driving Capacitive Loads Input Power and External Power TTL, CMOS, SiGe, In Pn, ECL, & GaAs; Output Power, Speed and engineering disciplines, Dv, di effects and Voltage Margins ICs: Cu vs Al, what are the issues? Low K Di-electrics Intersymbol Interference (ISI), eye diagrams and jitter Shoot Through Current (SSO) and how to minimize it Ground Bounce, Lead Inductance, Simultaneous Switching Noise (SSN) Electronic Packages: QFPs, PGAs, SOIC, PLCC, BGA, COB, TAB, FC, CSP and their relationship to SI Lead Capacitance and Thermal Considerations “Excellent content. Bob Hanson is very knowledgeable but most importantly he explains how things work.” Participant in one of Mr. Hanson’s seminars. Measurement Techniques Rise Time and Bandwidth of Oscilloscopes and probes Self-inductance and Spurious Signal Pickup of a Probe Ground Loop How Probes Load Down a Circuit Special Probing Fixtures Avoiding Pickup from Probe Shield Currents Viewing a Serial Data Transmission System, the eye pattern closure ISI, Skin effect and tan loss. PLL and DLLs Communications - SONET, SERDES, OC 192/768, Fiber Slowing Down the System Clock Observing Crosstalk Measuring Operating Margins Observing Metastable States in FlipFlops Terminations End/Source/Middle Terminators AC Biasing for End Terminators, where should it be used and how to choose the capacitor Hairball networks, bifurcated lines and capactive stubs Terminating differentials – Eliminating common mode and minimizing power What causes differentials unbalance? Diode and active terminators, Resistor Selection and Crosstalk in Terminators Connectors & Cables Vias Mechanical Properties of Vias Capacitance & Inductance of Vias Return Current and Its Relation to Vias Through Hole, Blind, Buried, Micro Vias Intelligent Vias and autorouters Via discontinuity and via resonance concerns Ground Planes and Layer Stacking High-Speed Current Follows the Path of Least Inductance Crosstalk in Solid and Slotted Ground Planes Inductive/capacitive ratios for micro strips, striplines, and asymmetric, dual, and edge LVDS Guard Traces – Do they stop crosstalk, can they resonate? Near-End and Far-End Crosstalk Separating analog from ECL/PECL and TTL/CMOS the concept of moats/floats/drawbridge Split planes - CMOS/TTL, PECL and analog using the same bias voltages How to Stack Printed Circuit Board Layers (e.g. 4, 6, and 10 layer) for Zo and crosstalk control, Cu fills on signal layers, minimizing warpage Interplane Capacitance – How thin, what material and stackup placement SIR vs. frequency, software for performing crosstalk and ground bounce tests “I know several people who would really benefit from this.” PCMCIA: Mr. Hanson discusses substitution materials instead of FR4 to control capacitance. This will address its 3 mils/layer with fine lines which makes it hard to control Z0 and causes crosstalk. BGA: By paralleling pwr/gnd balls to Cu planes, Mr. Hanson shows how inductance can be minimized. Usually 4 perimeter rings are routed (signals). Pwr/Gnd are paralleled with vias in the center cluster and inner perimeter ring. EMI, Source, path and receptor. EMI regulations – standards for USA, Europe (EU), and Asia. Conducting an EMI Test (Radiated/Conducted for Emissions/Immunity) ESD, Lighting and Transient RFI, EMI regarding PCBs, computers, analog designs, & systems “Very good anecdotes.” “Real-world examples used to help explain.” Buses Multidrop systems: Drivers, Transceivers, PCI, BTL, GTL & RAMBUS How they function, Clock rates, typical failures ISI – Minimize the effect with Equalization and Preemphasis LVDS: types, unbalance, noise, layout & making them function Methods to speed up busses – Distributive driving and load capacitance matching Clock Distribution “Exceptional seminar (on high speed).” Participants in the course Cables/Connectors Interfaces, Filtering and Shielding Timing Margin and Clock Skew Using Low-Impedance Drivers and Clock Distribution Lines Source Termination of Multiple Clock Lines Controlling Crosstalk on Clock Lines Delay Adjustments – Serpentine traces/DACs and varisters for dynamic delay Differential Distribution Controlling Clock Signal Duty Cycle using the integrator Source synchronous clocking, DDR & RDRAM www.americomseminars.com Grounding designs/Filtering CM Radiation Antenna Loops Basics of PCB Radiation PCB Suppression Techniques Crosstalk/Termination Power/Ground Planes Spread Spectrum Clocking Bypass and Radiation on PCBs Interference Coupling Mechanism – Near/Far Field, Coupling modes (Differential/common) and resonance Capacitive & Magnetic Shielding Slots Shield Grounding Cable Radiation Shielding Types Transfer Impedence Shielding Connection – Leakage Loss of Ground Plane in Cables Cables Configuration Antenna Loops with Cable Connections High Speed Connectors Filtering Shielding vs Filtering Using Ferrites Filtering Mains Supply Using Transients Suppressors on Mains & I/O Lines Radiation Through Shields REGISTRATION INFORMATION Locations throughout the United States and at your site! See our web page for the latest information. Schedule: 8am to 5pm, First day; 8:30am to 5pm, Second, Third and Fourth day; lunch break from 12:30 to 1:30pm each day; Demos on the second night occur from 5:15 to 8:00 pm if the vendor is available. E-mail the form’s info to americomseminars@aol.com Fax the form to 775-8832384 Sign up on our web page: www.americomseminars.com Call us: 1-800-650-3033 (outside US, 360-479-0949) Share this seminar with colleagues Mail the form to Americom Seminars; 2533 No. Carson Street, Suite 4213; Carson City NV 89706 I want to attend in or near this city _____________________________ ___ the 4-day High Speed & EMI-EMC Seminar optional: ___ 3 day seminar (high speed/PCB) only ___ 1 day EMI seminar only Name _________________________________________ Job Title _________________________________________ Company/Organization _________________________________________________________________________________________________ Address _____________________________________________________________________________________________________________ City ________________________________________________________ State ____________ Zip ____________________________________ Work Phone* (with area code) _____________________________________ Fax No. _______________________________________________ E-mail Address* (please write very clearly) __________________________________________________________________________________ *phone numbers and e-mail address are used to update you on the seminar. Paying with _____ Check-Money Order (enclosed) _____ Mastercard _____ VISA _____ Am. Express _____ Discover ______ P.O. Credit Card or PO Number is: ______________________________________________ Expiration Date _________________________________ Credit Card Address ___________________________________________________________________________________________________ Authorization Signature _____________________________________ Print Name __________________________________________________ If you wish, include a note stating the high-speed issues most salient to you. If you have not received confirmation within 7 working days of sending your registration, please e-mail us at americomserminars@aol.com or call us at 1-800-650-3033 (outside US 360-479-0949) Discounts for three persons from the same company. Encourage your colleagues to join you. Course Fee Payment See our web page for the fee. The fee includes: Instruction covering the most critical and salient aspects of high speed design and troubleshooting and key issues of EMI/EMC Exhibits for viewing all four days For the high speed portion of the course: A copy of High-Speed Digital Design: A Handbook of Black Magic by Howard Johnson, Ph.D. and Martin Graham, Ph.D. and a complete 360+ page book of class notes For the EMI portion of the course: A copy of EMC for Product Designers, by Tim Williams and 128 pages of comprehensive course notes. Continental breakfast, lunch, and refreshments each day Certificate of Completion Firms that send 3 or more attendees receive a $100 discount for each person for the four day course. Checks or Money Orders made to Americom Seminars, Inc. VISA, MasterCard, American Express, Discover Purchase Orders; 10% fee for P.O.’s, waived if paid within 30 days of the invoice date. Cancellations You may cancel your enrollment up to 15 days prior to the seminar, but you must pay a $100 processing fee. Cancellations 2 to 14 days before the seminar pay a $250 fee ($150 for 1 day class). Cancellations the day before or day of the seminar, owe the full amount. You may substitute enrollees at any time. If this course is not held for any reason, Americom Seminars, Inc.’s liability is limited to refund of the full course fee. Questions: Email us at americomseminars@aol.com Call us at 1-800-650-3033 (outside U.S., call 360-479-0949) Write us at: Americom Seminars; 2533 North Carson Street Suite 4213; Carson City NV 89706 You can register at www.americomseminars.com