Curriculum vitae

advertisement

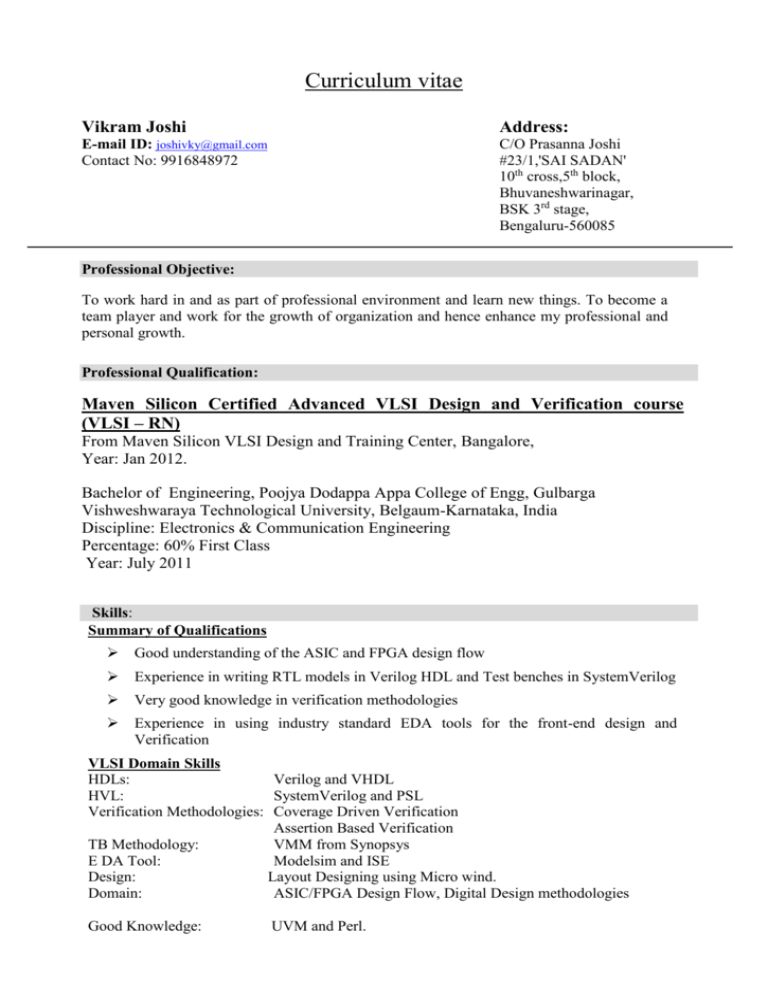

Curriculum vitae Vikram Joshi Address: E-mail ID: joshivky@gmail.com Contact No: 9916848972 C/O Prasanna Joshi #23/1,'SAI SADAN' 10th cross,5th block, Bhuvaneshwarinagar, BSK 3rd stage, Bengaluru-560085 Professional Objective: To work hard in and as part of professional environment and learn new things. To become a team player and work for the growth of organization and hence enhance my professional and personal growth. Professional Qualification: Maven Silicon Certified Advanced VLSI Design and Verification course (VLSI – RN) From Maven Silicon VLSI Design and Training Center, Bangalore, Year: Jan 2012. Bachelor of Engineering, Poojya Dodappa Appa College of Engg, Gulbarga Vishweshwaraya Technological University, Belgaum-Karnataka, India Discipline: Electronics & Communication Engineering Percentage: 60% First Class Year: July 2011 Skills: Summary of Qualifications Good understanding of the ASIC and FPGA design flow Experience in writing RTL models in Verilog HDL and Test benches in SystemVerilog Very good knowledge in verification methodologies Experience in using industry standard EDA tools for the front-end design and Verification VLSI Domain Skills HDLs: Verilog and VHDL HVL: SystemVerilog and PSL Verification Methodologies: Coverage Driven Verification Assertion Based Verification TB Methodology: VMM from Synopsys E DA Tool: Modelsim and ISE Design: Layout Designing using Micro wind. Domain: ASIC/FPGA Design Flow, Digital Design methodologies Good Knowledge: UVM and Perl. Projects: VLSI Projects UART- IP Core – Verification HVL: System Verilog EDA Tools: Modelsim. The UART IP core consists of a transmitter, a receiver, a modem interface, a baud generator, an interrupt controller, and various controls and status registers. This core can operate in 8-bit data bus mode or in 32-bit bus mode, which is now the default mode. It is an interface between wishbone compatible UART transceiver, which allows communication with modem or other external devices, like another computer using a serial cable and RS232 protocol. The UART core RTL is technology independent and fully synthesizable. Architected the class based verification environment using system Verilog Verified the RTL module using System Verilog Generated functional and code coverage for the RTL verification sign-off Real Time Clock – RTL design and verification HDL: Verilog HVL: SystemVerilog EDA Tools: Modelsim, Questa – Verification Platform and ISE Implemented the Real Time Clock using Verilog HDL independently Architected the class based verification environment using SystemVerilog Verified the RTL model using SystemVerilog. Generated functional and code coverage for the RTL verification sign-off Dual Port RAM – verification HVL: System Verilog EDA Tools: Modelsim, Questa – Verification Platform and ISE Implemented the Dual Port Ram using Verilog HDL independently Architected the class based verification environment using system Verilog Verified the RTL module using System Verilog Generated functional and code coverage for the RTL verification sign-off Currently Working on. Router 1x3 – RTL design and Verification HDL: Verilog HVL: SystemVerilog EDA Tools: Modelsim, Questa -- Verification Platform and ISE Description: The router accepts data packets on a single 8-bit port called data and routes the packets to one of the three output channels, channel0, channel1 and channel2. Engineering Project: “Efficient route monitoring and suggesting mechanism using Variable Message Signboard”. Description : Intelligent traffic observing and suggesting mechanism which will be able to guide and inform about the vehicle density present at the other nearby traffic signals so that the driver can easily decide the path to be followed in case he feels that a detour might be helpful in making him reach the destination faster Tools : microcontroller, sensors, vhdl kit Implementation : Bangalore traffic management 2010-11 project. Platform : VHDL Activities: Participated in IIMB fest ‘UNMAAD 09’. Secured consolation prize in state level paper presentation conducted in SJBIT Bangalore. Actively participated as a volunteer for organizing the event -“Golden Jubilee alumni meet” in college. Senior in playing music instrument TABALA. Personal Information: Date of birth : 27 October 1988 Sex Nationality Father’s name Languages known Hobbies : : : : : Male Indian Vijayakumar.H.Joshi English,Kannada. Reading novels ,listening music, outdoor games. Permanent address : Vikram Joshi s/o Vijayakumar Joshi . #8-11-191/764 ‘SHYAMALA’ Vidyanagar Bollamandoddi-road Raichur. 584101Karnataka I do hereby declare that the information and details provided above are true and best of my knowledge. Date: 21/06/2012 Place: Bangalore. (Vikram joshi)