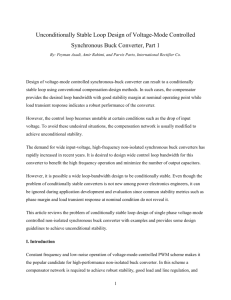

III. Unconditionally Stable Loop Design

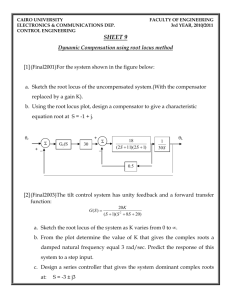

advertisement

Unconditionally Stable Loop Design of Voltage-Mode Controlled Synchronous Buck Converter, Part 3 By: Peyman Asadi, Amir Rahimi, and Parviz Parto, International Rectifier Co. III. Unconditionally Stable Loop Design In the previous section, we showed with an example that a converter with conditionally stable loop can perform well under nominal operation with good phase margin and good load transient response. However, the performance of a conditionally stable converter decays as its gain gets close to its unstable region. For example, if the input voltage of the application circuit in Figure 5 drops to 3.3V, the phase margin drops and its load transient response oscillates (Figure 9). Such a performance is unacceptable for applications with wide input range. Moreover, the converter may operate at low input voltage during start-up or shut-down. In general, application engineers avoid conditionally stable designs and even desire to guarantee the phase does not drop below certain level such as 45 before gain crossover frequency. For some conditionally stable converters, the loop bandwidth is unreasonably high and application engineers can redesign the compensation network with lower loop bandwidth to achieve both unconditional stability and desired load transient response [1]. Another option is using feedforward control scheme of IR3895 to keep the loop gain constant [2]. However, not every product in the market has this feature. The ultimate solution to achieve unconditional stability is relocating the zeros of the compensation network. For example, the location of poles and zero of Type III-B compensator (Figure 10(a)) are conventionally calculated as following [1]. FP1 0 (1) FZ1 0.5 FZ 2 (2) FZ 2 F0 1 Sinθ 1 Sinθ (3) FP 2 F0 1 Sinθ 1 Sinθ (4) 1 FP 3 0.5 FS (5) The second pole and zero of the compensator are placed to create a phase-lead by degree at the gain crossover frequency (i.e., Fo). In this example, FZ1 and FZ2 are located at 24 kHz and 48 kHz. We can place them closer to FLC to achieve unconditional stability. In the bode plot of Figure 6, the minimum phase is about -10 degree at 28 kHz. To assure the phase doesn’t drop below 45 at all operating point below gain crossover frequency, Fz1 and Fz2 in the new location should add extra 55 phase-lead at the frequency with minimum phase (Fphase_min), which is 28 kHz. Thus, the total phase-lead of compensator zeros at Fphase_min should be, Fphase_ min FZ 1 30 120 25 100 Magnitude 20 15 60 10 40 PM=34 0 Fphase_ min FZ 2 ) 130 . (6) 80 Phase 5 ) tan 1 ( 20 Phase (degree) Gain Magnitude (db) 55 tan 1 ( 0 BW=70.5kHz -5 -20 -10 -40 100 10 Frequency (kHz) (a) Frequency response at 3.3V input, phase margin is 34. (b) Output voltage response to a 0A-6A step load at 3.3V input 35 30 30 25 25 20 Gain (db) Gain (db) Fig. 9. The relative stability of Fig. 4 decays at 3.3V input 20 15 15 10 10 5 5 0 -5 0 1 10 100 1 1,000 (a) Conditionally stable design of Fig. 5 10 100 Frequency (kHz) Frequency (kHz) (b) Unconditionally stable Design Fig. 10. Desired gain of the compensator network 2 1,000 The new location of compensator zeros can be calculated as following. FZ 2 28kHz ( 4 tan ) /( 3 9 8 (tan ) 2 ) 17.8kHz (7) FZ1 0.5 FZ 2 8.89kHz (8) Furthermore, moving Fz1 and Fz2 to lower frequencies requires dropping the integrator gain of the compensator (i.e. 1/(Rf1.Cc1)) to keep the bandwidth constant. The desired gain magnitude of the compensator with conventional design (i.e., conditionally stable) and the new approach (i.e., unconditionally stable) are compared in Figure 10. Based on the new location of compensator zeros and adjusted gain, the value of resistor and capacitors are recalculated [1]. The new selected values for Rf1, Rf2, Rc1, Cc1 are 6.8 kΩ, 4.53 kΩ, 3.9 kΩ, and 3.9 nF, respectively. The value of Rf3, Cf3, and Cc2 are the same as the ones in Figure 5. The bode plot of the loop with new compensation values are shown in Figure 11. The phase margin and gain margin are 62 and 19 dB with 187 kHz bandwidth. The phase of the loop always stays over 54 at frequencies less than the gain crossover frequency, which indicates unconditional stability of the loop. The step-load transient response of the new design is shown in Figure 12. Comparing this result with the transient response from Figure 8 shows that the transient response is slower after updating compensation network. Even though the loop bandwidth is slightly higher in case of Figure 12, the peak-to-peak output voltage deviation is higher than the conditionally stable design. This behavior is due to the relatively smaller loop gain at low frequencies with new compensation values. 3 Fig. 11. Frequency Response of the IR3895 design example with unconditional stability. Fig. 12. 0A to 6A step load response of unconditionally stable loop design at 12V input Ch1:Vout, Ch4:Load Current. 4