HW_08 - University of Southern California

advertisement

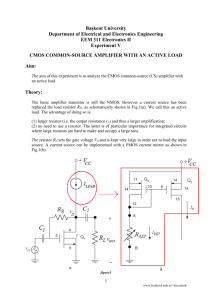

U niversity of S outhern C alifornia School Of Engineering Department Of Electrical Engineering EE 348: Homework Assignment #08 (Due 04/26/2001) Spring, 2001 Choma Problem #35: The NMOS transistors in the amplifier of Fig. (P35a) are identical except for the fact that the gate aspect ratio of the driver transistor, MD, is k–times larger than the gate aspect ratio of the load device, transistor ML. The drain-source channel resistances of both transistors are large, but they are not infinitely large. Transistor MD is saturated. Vdd ML Vo MD Rs CL Rth Vs Vos CL KthVs Vgg Vss (a). (b). Fig. (P35) (a). Reduce the small signal equivalent model of the subject amplifier to the Thévenin equivalent form abstracted in Fig. (P35b). Give “exact” and approximate expressions for the Thévenin parameters, Kth and Rth. (b). What is the time constant associated with the pole established by the load capacitance, CL? Approximate your “exact” result. (c). What is the overall voltage transfer function, Av(s) = Vos(s)/Vs(s)? Give an approximate expression for the voltage gain at zero signal frequency. (d). What are the 3–dB bandwidth and unity gain frequency of the amplifier? Approximate your “exact” results. EE 348 University of Southern California J. Choma, Jr. Problem #36: In the CMOS amplifier of Fig. (P36a), both transistors operate in their saturated domains and do not have identical small signal parameters. Moreover, their channel resistances are not infinitely large. (a). Reduce the small signal equivalent model of the subject amplifier to the Norton equivalent form abstracted in Fig. (P36b). Give “exact” and approximate expressions for the Norton parameters, Gn and Rn. (b). What is the time constant associated with the pole established by the load capacitance, CL? Approximate your “exact” result. (c). What is the overall voltage transfer function, Av(s) = Vos(s)/Vs(s)? Give an approximate expression for the voltage gain at zero signal frequency. (d). What are the 3–dB bandwidth and unity gain frequency of the amplifier? Approximate your “exact” results. Vdd MP Vbb Vo MN Rs CL Vs Vos GnVs Rn CL Vgg Vss (a). (b). Fig. (P36) Problem #37: A capacitance, CL, terminates the output port of the differential -to- single ended converter depicted in Fig. (4.26) of Lecture Supplement #4. Transistors M1 and M2 are identical, as are transistors M3 and M4, but the transistor pair, M1–M2, does not have small signal parameters identical to those of the M3–M4 pair. Assume that all transistors operate in their saturated regimes and that the common mode rejection ratio of the converter is infinitely large. (a). What is the time constant associated with the pole established by the load capacitance, CL? Approximate your “exact” result. (b). What is the overall voltage transfer function, Av(s) = Vos(s)/Vs(s)? Give an approximate Homework #08 55 Spring Semester, 2001 EE 348 University of Southern California J. Choma, Jr. expression for the voltage gain at zero signal frequency. (c). What are the 3–dB bandwidth and unity gain frequency of the amplifier? Approximate your “exact” results. (d). In order for the circuit at hand to achieve a very large common mode rejection ratio, would you advocate a long or a short channel length for transistor M5? Briefly explain your conclusion. Problem #38: The NMOS transistors in the buffer of Fig. (P38a) are identical except for the fact that the gate aspect ratio of transistor M2 is k–times smaller than the gate aspect ratio of the driver device, transistor M1. The drain-source channel resistances of both transistors are large, but they are not infinitely large. All transistors are saturated. Vdd Rs Rin M1 Rout Vs Rth Vo M2 CL Vbb Rout Vos CL KthVs Vgg Vss (a). (b). Fig. (P38) (a). Reduce the small signal equivalent model of the subject amplifier to the Thévenin equivalent form abstracted in Fig. (P38b). Give “exact” and approximate expressions for the Thévenin parameters, Kth and Rth. (b). What is the time constant associated with the pole established by the load capacitance, CL? Approximate your “exact” result. (c). What is the overall voltage transfer function, Av(s) = Vos(s)/Vs(s)? Give an approximate expression for the voltage gain at zero signal frequency. (d). What is the 3–dB bandwidth of the amplifier? Approximate your “exact” results. Why is finding the unity gain frequency of the circuit inappropriate? Problem #39: The current source, Idd, in the common gate amplifier of Fig. (P39a) is ideal in the sense that its small signal terminal resistance is infinitely large. On the other hand, Is is a signal current source. The channel resistance of the transistor, which operates in saturated mode, is large, but it is not infinitely large. Homework #08 56 Spring Semester, 2001 EE 348 University of Southern California J. Choma, Jr. (a). Reduce the small signal equivalent model of the subject amplifier to the Norton equivalent form abstracted in Fig. (P39b). Give “exact” and approximate expressions for the Norton parameters, Gn and Rn. (b). What is the time constant associated with the pole established by the load capacitance, CL? Approximate your “exact” result. (c). Give “exact” and approximate expressions for the low frequency input resistance, Rin. (d). What is the overall transimpedance function, Zv(s) = Vos(s)/Is? Give an approximate relationship for this transimpedance at zero signal frequency. (e). What are the 3–dB bandwidth and unity transimpedance gain frequency of the amplifier? Approximate your “exact” results. Vdd Idd Vo MN Rs CL Rin Vs Rout Vos Rs Is GnVs Vgg (a). Rn CL (b). Fig. (P39) Problem #40: As discussed in class, that static output -versus- input characteristic of the NMOS common source amplifier depicted in Fig. (P35a) assumes the first order form provided herewith in Fig. (P40). For analytical simplification, the indicated curve is drawn for the special case of Vss = 0. Moreover, the threshold voltage, VH, of each transistor is presumed identical, while the indicated maximum output voltage is Vomax = Vdd - VH. Homework #08 57 Spring Semester, 2001 EE 348 University of Southern California J. Choma, Jr. Vo Vomax MD Off M D Sa tu ra te d MD Ohmic Vomin 0 Vi VH Vimax Fig. (P40) (a). If λdl represents the ratio of the driver gate aspect ratio -to- the load gate aspect ratio, show that the minimum output voltage for Vss = 0 is Vomin Vdd VH 1 dl Vomax 1 dl . (b). Show that for Vss = 0, the optimum input bias voltage, Vgg, which results in maximum possible output signal swing is given by Vgg VH Vdd VH 2 dl 1 dl . (c). For Vdd = 2.2 V, Vss = 0 V, VH = 750 mV, and a small signal voltage gain magnitude of 5, evaluate Vomax, Vomin, and the optimum input biasing voltage, Vgg. Homework #08 58 Spring Semester, 2001 EE 348 University of Southern California J. Choma, Jr. U niversity of S outhern C alifornia School Of Engineering Department Of Electrical Engineering EE 348: Homework Assignment #08 (SOLUTIONS: Due 04/26/2001) Spring, 2001 Choma Problem #35: Homework #08 59 Spring Semester, 2001