Chapter 14 MOSFET DEVICE PROBLEMS version 2.3

advertisement

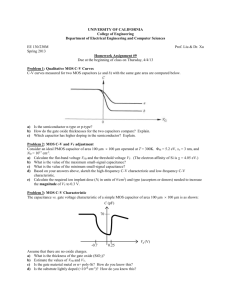

Chapter 14 MOSFET DEVICE PROBLEMS version 2.3 14-1. The plot shown is a C-V plot for an nMOSFET test device of gate dimensions W/L = 420m/4m. From the plot, determine within 5% accuracy: (a) VTH and VFB (b) COX (capacitance/area in fF/m2) and tOX. (c) CMOS(min) and (Hint: use the depletion approx to evaluate CMOS(VG(tot)) Answers: 0.714 fF/m2 , 48.3nm, 0.179 fF/m2, 0.632 V 14-2. The plot shown is a C-V plot for a pMOSFET test device of gate dimensions W/L = 420m/4m. From the plot, determine within 5% accuracy: (a) VTH and VFB (b) COX (in fF/m2) and tOX. (c) CMOS(min) and (Hint: use the depletion approx to evaluate CMOS(VG(tot)) 14.3 For an nMOS junction construct having gate oxide thickness tOX = 45 nm and substrate doping NA = 4 x 1016 #/cm3 find: (a) (b) (c) (d) Oxide capacitance COX in fF/m2 Debye length of substrate Fermi potential F Body-effect coefficient Answers: 0.77 fF/m2, 20.5 nm, 0.382V, 1.51 V 14-4 A silicon-gate nMOS transistor with TPG = +1 has tOX = 45nm and (p-type) substrate with impurity doping NSUB = 4 x 1016 #/cm3 . The oxide gate layer is afflicted with trapped charge of density 1.6 x 1010 #/cm2. Determine: (a) VFB and VTH (b) Depletion layer thickness at VGS = VTH (c) CMOS(min) 14-5. A silicon-gate pMOS transistor with TPG = -1 has tOX = 69nm and (p-type) substrate with impurity doping NSUB = 1 x 1016 #/cm3 . The oxide gate layer is afflicted with trapped charge of density 1.6 x 1010 #/cm2. Determine: (a) VFB and VTH (b) Depletion layer thickness at VGS = VTH (c) COX and CMOS(min) 14-6. For an nMOS transistor with VFB = -0.7V, B = 0.9V, COX = 0.682 fF/m2, CFBS = 2.4 fF/m2, GAMMA = 0.8 V , VGS = 6.0V and VDS = 3.0V find: (a) (b) (c) (d) (e) VTO (= zero-bias threshold) Inversion charge/area qI at the source Inversion charge/area qI at the drain Depletion charge/area QB at the source Depletion charge/area QB at the drain (Assume that VBS = 0 in determining each of these quantities) 14–7. Find the threshold voltage for a high–voltage (= thick oxide) nMOS transistor which has tox = 800 nm. Assume NB = 2 x 1015 #/cm3, VFB = –0.7 V, and B = Lindner potential = 2.1F + 2.08 VT. In your analysis identify the value of gamma. Answers: = 6.00 V , VTH0 = 4.995 V 14–8. The gate oxide of a MOS device has field strength (breakdown field) of approximately 3.5 x 106 V/cm. Determine the maximum drain voltage VD for an oxide of thickness (a) 20 nm (b) 800 nm, assuming gate voltage VG = 2 V. 14–9. The figure shown represents a cross–section of a CMOS inverter fabricated using a typical p–well CMOS process. Both the n– and p– channel inverters have a gate oxide thickness tox = 50 nm and n+ polysilicon gates. The area density of oxide fixed trapped charge is Nox = 5 x 1010 #/cm2. The n– susbstrate has a doping level ND = 2 x 1015 #/cm3 and the p-well has doping NA = 2 x 1016 #/cm3. a) Find the zero–bias threshold voltages, VTN and VTP for these two transistors from the above information. Assume B = Lindner potential = 2.1F + 2.08 VT. b) It is desired to shift the threshold voltages of the n– and p– channel transistors, as found in part (a), using an implant so that they are equal in magnitude, that is, VTN = – VTP . To simplify processing, a ’blanket’ implant is applied, with all portions of the wafer receiving the same dose. Should a boron or a phosphorus implant be applied? What implant dose is required? Figure P14–9. CMOS device cross–section, p–well fabrication protocell Answers: (a) VTN = .757V, VTP = –1.335V, (b) NI = 1.38 x 1011 #/cm2 !_ _-./_ __) 0_ 14–10. A high–voltage power MOSFET is constructed as shown. Note that this is a vertical transistor with an lightly–doped (n–) layer (ND = 5 x 1014 #/cm3) in series with the drain. If this layer is 10m thick and the breakdown voltage of Si is 3 x 105 V/cm, determine (a) the maximum reverse VDS that this transistor can withstand. (b) the series resistance of this layer for a transistor of gate dimensions 20m x 100m. Assume n = 1300cm2/Vs. Note that most of the conduction takes place below the gate. Figure 14–10 The power MOSFET: (a) cross–sections (b) ID vs VGS output characteristics, (c) ID vs VDS output characteristics.