0506710(CCF) Bandyopadhyay - NSF Nanoscale Science and

advertisement

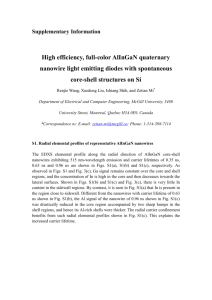

NSF Nanoscale Science and Engineering Grantees Conference, Dec 3-6, 2007 Grant # : CCF-006710 Computing with Self Assembled Quantum Dots and Nanowires NSF NIRT Grant CCF-0506710 PIs: S. Bandyopadhyay1, K. Karahaliloglu1, Jiangpin Sun2 and K. L. Wang3 1 Department of Electrical and Computer Engineering, Virginia Commonwealth University 2 Department of Electrical and Computer Engineering, University of Michigan-Ann Arbor 3 Department of Electrical Engineering, University of California, Los Angeles The objective of this research is to build a nanoelectronic neuromorphic network using self assembled arrays of quantum dots, nanowires and nanodiodes. Such a network has been shown capable of acting as an associative memory [2], Boolean logic circuits [3] and image processors [2, 4, 5]. A schematic representation of the network is shown in Fig. 1. It consists of an array of vertically conducting nanowires, each exhibiting a negative differential resistance, and each wire is resistively and capacitively coupled to its four nearest neighbors. Fig. 1: A schematic depiction of the quantum neuromorphic network (QNN). The substrate is shown as a double barrier resonant tunneling structure that is known to exhibit a negative differential resistance. Atop the substrate is an array of metallic quantum dots that serve as the circuit nodes. Each dot is charged to a value qmn by the input stimulus. Two different fabrication approaches have been undertaken at UCLA and VCU. The UCLA group has focused on realizing the computing elements with buried quantum dots fabricated with MBE. These buried dots have non-linear conduction characteristics and are resistively and capacitively coupled to their near neighbors. A schematic representation of this approach is shown in Fig. 2(a). The VCU approach has been to use chemical self assembly. Anodization of aluminum in either oxalic or sulfuric acid produces an alumina film containing a regimented array of nanopores that are either 10 nm in diameter (if produced in sulfuric acid), or 50 nm in diameter (if produced in oxalic acid). Semiconductors (CdS) are then selectively electrodeposited within the pores to create an array of vertically standing resistors in a ceramic matrix. These resistors are resistively and capacitively coupled to their nearest neighbors through the intervening alumina. We have measured the coupling resistance to be ~ 640 k and the coupling capacitor is ~ 5 aF. A cross-section TEM micrograph of nanowires produced within the pores is shown in Fig. 3. NSF Nanoscale Science and Engineering Grantees Conference, Dec 3-6, 2007 Grant # : CCF-006710 (a) (b) Fig. 2: (a) An MBE grown array of buried self assembled quantum dots to replicate the quantum neuromorphic network (QNN), (b) An atomic force micrograph of a self assembled porous ceramic matrix consisting of a hexagonal close packed array of 50nm diameter pores produced by anodizing an aluminum foil in oxalic acid. Semiconductors electrodeposited within these pores exhibit a negative differential resistance, which is the central requirement of QNN. Fig. 3: A cross-section TEM of 50-nm diameter nanowires produced within the pores of an alumina film. Micrograph courtesy of Dr. David Lockwood, NRC, Canada. The nanowires self assembled at VCU exhibit both S-type and N-type negative differential resistance (NDR) at room temperature as shown in Fig. 4 [6]. The measured characteristics are adequate for image processing functions. Using the measured data as parameters, we have simulated image processing scenarios where the each dot represents a pixel and the voltage level on the dot is proportional to the pixel brightness. An input image is converted to voltage levels on the dots and the system is allowed to relax in time. The dots interact with each other via the inter-dot coupling resistances and capacitors. Steady state is NSF Nanoscale Science and Engineering Grantees Conference, Dec 3-6, 2007 Grant # : CCF-006710 reached in fractions of a nanosecond. The steady state voltage levels correspond to the processed image. In our case, the processing corresponds to edge-enhancement-detection. The multiple NDR peaks in the right panel of Fig. 4 allow color image processing. Fig. 4: (left) S-type non-linearity in the current-voltage characteristic of fabricated nanowires (the peak-to-valley ratio at room temperature is 19:1), (right) N-type NDR with a peak-to-valley ratio of 1.5:1 at room temperature. There are multiple N-type NDR peaks. Fig. 5: (L) Edge enhancement detection, (R) The difference between black and white is blurred. This processing task requires multiple NDR peaks. References [1] For further information about this project email sbandy@vcu.edu [2] V. P. Roychowdhury, et al. , IEEE Trans. Elec. Dev., vol. 43, pp. 1688-1699 (1996). [3] V. P. Roychowdhury, et al. , Proc. IEEE, vol. 85, pp. 574-588 (1997). [4] K. Karahaliloglu, et al., IEEE Trans. Elec. Dev., vol. 50, pp. 1610-1616 (2003) [5] S. Bandyopadhyay, et al., IEE Proc. – Circuits, Devices, Syst., vol. 152, pp. 85-92 (2005). [6] V. Varfolomeev, et al., submitted to IEEE Trans. Nanotech. [7] P. Mazumder, Proceedings of IEEE NANO 2007, Hong Kong, August 2007.