TITLE OF RESEARCH PAPER:

advertisement

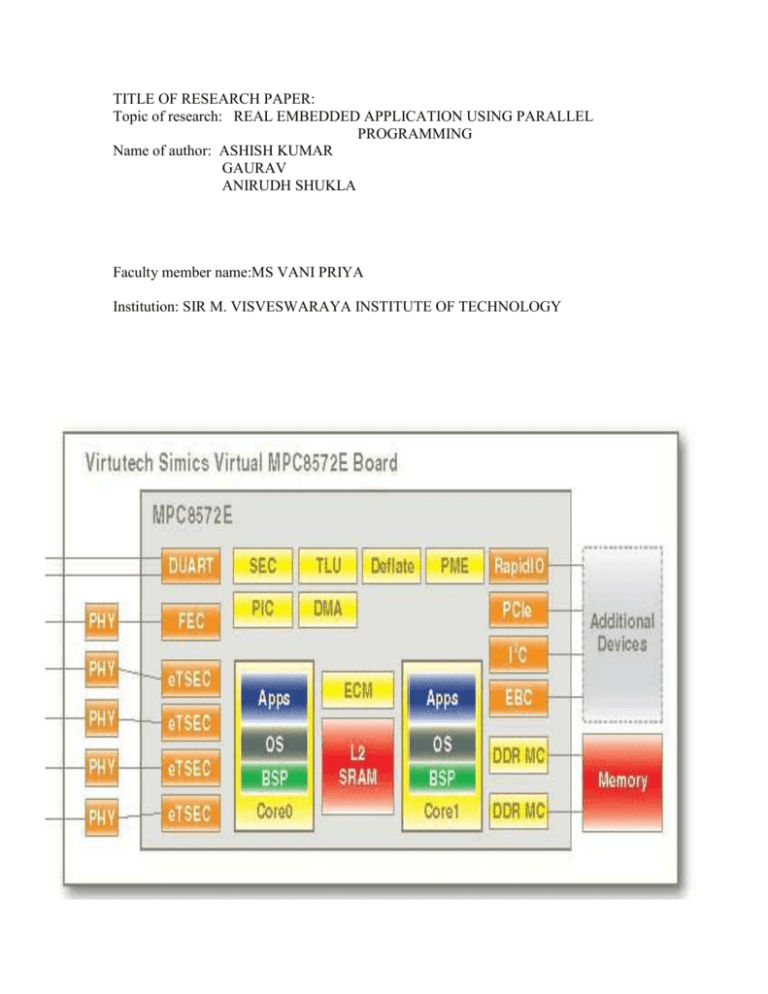

TITLE OF RESEARCH PAPER: Topic of research: REAL EMBEDDED APPLICATION USING PARALLEL PROGRAMMING Name of author: ASHISH KUMAR GAURAV ANIRUDH SHUKLA Faculty member name:MS VANI PRIYA Institution: SIR M. VISVESWARAYA INSTITUTE OF TECHNOLOGY ABSTRACT Modern telecom providers and application developers must face many challenges that make the design ofreal-time embedded telecom applications a complex task. The convergence between wired and wireless communication, the high expansion of the mobile communication and the need for seamless connectivity between different media and protocols, pushes toward the integration of multiple different functionalities and services on the same device. Multi-core hardware platforms are becoming the preferred target of current and future telecom applications because they offer the computational capability and the flexibility needed to support these functionalities. For instance, media gateways must support both network processing operations (i.e., IPv6 routing, security and encapsulation) as well as video processing (transcoding of media content, image recognition) for specific multimedia networking application scenarios such as video on demand, distance learning, video conferencing, and so on. However, they present very challenging problems to the embedded system programmer. METHODOLOGY This project aims at developing a software design methodology, supported by appropriate runtime platforms and analyses, for multi-processor embedded real-time systems. These methodologies will be developed at various software levels, ranging from compiler, middleware and operating system. However, the project will focus on compiler and OS level optimizations, with the purpose of being as much as possible transparent for the programmer. To this purpose, the compiler will be responsible of automatic scalable parallelization strategies, while the OS and middleware will be responsible of resource-aware mapping. Open source compilers and OSes will be considered to achieve this target, namely GNU tool chain (www.gnu.org) with OpenMP extension for parallel programming (www.openmp.org) running under embedded Linux OS. The considered application scenario will be composed by networking and non-networking applications for which an efficient mapping strategy into a multicore architecture will be studied. The research will focus on the problems of scalability and debugging issues. The project will be structured as parallel branches each one of them will follow a specific application context. The results obtained in the various branches will be compared in order to come up with a common application development methodology. The project will be conducted using freely available open source applications running on the Simics simulator of MPC8572 multicore platform provided by an industrial partner, namely the Network Computing System Group (NCSG) of Freescale Semiconductor Ltd that will provide also the software environment for application development on the target platform. The simulator will based on next generation network processor for media gateways. It will be obtained through an academic research program with both the simulator vendor Virtutech and Freescale. Since the simulator will be based on a dual core Freescale architecture, to assess scalability issues a suitable extension of the simulator will be developed so as to add a configurable number of cores. DISCUSSION In this project we will investigate design and implementation strategies for programming complex real-time embedded applications on multicore platforms such as the one shown in Figure 1. The investigation will be carried out on two specific application scenarios that are representative of two important classes of applications. The first application scenario concerns the design and implementation of a suite of networking protocols. The second application scenario concerns the design and implementation of multimedia streaming applications. In both cases, we will investigate how to design an application as a set of concurrent communicating modules that can potentially run in parallel on a multiprocessor architecture. In addition, the QoS parameters and the timing constraints will be specified for each module. PROBLEM STATEMENT Research challenges All the considered applications are characterized by tight real-time constraints and stringent QoS requirements. In this context, one of the major challenges for platform developers it to efficiently support these applications while ensuring scalability from 1 to N cores (from 2 cores of the current platforms to 16 or 32 cores) and to find a suitable methodology for developing scalable applications. So far, hardware accelerators have been used to improve performance of these applications. However, design of dedicated hardware is not efficient for semiconductor companies. On the other side, homogeneous architectures are easier to design and allow a faster time to market. Moreover, they are more flexible has they can handle a more heterogeneous type of workload. For this reason, one of the key question in this context is what is the level of performance achievable without using hardware acceleration. Summarizing, there is urgent need of research work aimed at establishing what is a suitable methodology to design and debug networking and multimedia applications into homogeneous multicore architectures. Research should assess limitations of current parallelization methods and tools and suggest improvements. Solutions developed in the context of general purpose Symmetric Multiprocessors (SMP) like Pthreads and OpenMP will make sense for future multicore platforms in this application context? Are these tools suitable to handle a larger number of cores? Do these tools implement a suitable debugging strategy? How can be optimized? How they can be adapted to distributed memory architectures or to hybrid architectural solutions companies are looking where localized SMP nodes are interlinked with a distributed memory architecture? KEY RESULT: The main outcomes of this project will be: i) a methodology and a set of instruments for efficiently mapping network multimedia applications on multicore targets in a scalable way; ii) an instrumented version of the OpenMP+GCC compiler targeted to efficiently support the mapping of embedded multimedia networking applications on a large number of cores on top of embedded Linux OS; iii) the implementation of two prototype applications, one for each application scenario on the multicore platform; iv) an extension of the multicore simulator to support a configurable number of cores (currently limited to two cores). CONCLUSION In this project we will address mapping of applications in homogeneous multicore architectures in SMP environments, trying to face scalability and debugging issues. However, where possible, optimization for distributed memory architectures will be considered. ACKNOWLEDGEMENT we would like to express my gratitude to all those who gave me the possibility to complete this thesis. we want to thank my institution Sir M. Visveswaraya Institute of Technology for giving me permission to commence this thesis in the first instance, to do the necessary research work and to use departmental data. we have furthermore to thank the mentor Ms Vani Priya for her full support. We would like to thank all of our team member Ashish Kumar,Gaurav Singh and Anirudh Shukla For our full motivation and determination for the project. Lastly We would like to thank our department of computer science and information science Engg. THE END