NMOS Process Flow - Boise State University

advertisement

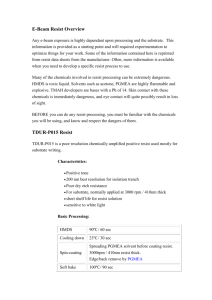

NMOS Fabrication Boise State University STEP 1: Grow Thermal Oxide Hardmask for Source and Drain Regions Objective: Grow a 5000Å layer of SiO2 on a clean, p-type Si wafer. Wafer should be doped with boron and have a resistivity of 1-10Ωcm. This oxide will be used as a hard mask so that the source and drain regions can be doped. Oxidation Process: Follow directions posted by furnace or on lab website to perform wet oxidation. o Parameters using oxidation calculator for our furnace: 1000C for 1hr 25min flowing 3sccm of O2. Measure oxide thickness with the Nanospec. Record these values so that oxide etch time can be determined. STEP 2: Photolithography Level 1 Pattern Source and Drain Regions Objective: Pattern the source and drain regions. Procedure: 1. Apply HMDS HMDS is an adhesion promoter and helps the photo resist stick to the surface of the silicon Spin at 500 RPM for 5 seconds followed by 5000 RPM for 35 seconds on Spin Coater. This is typically recipe 1 on the spin coater. 2. Apply positive photoresist (SPR-220-1.2) Immediately follow the HMDS with resist Spin at 3500RPM for 30 seconds. This is typically recipe 2 on the spin coater. Soft bake at 90 C for 1 minute to bake out liquid solvents Measure resist with NanoSpec. Should be ~1um thick. 3. Pattern Use ChemFET Mask 1. Follow contact aligner procedures posted by tool or at contact aligner webpage Expose for 2 seconds at 11.8W/cm^2 for a 1um process 4. Develop MF 26A developer for 20-25 seconds Quench in water STEP 3: Etch Oxide to Create Hardmask for Source and Drain Regions Objectives: We now have patterned resist on our wafers. We need to etch through the oxide that is not covered by resist in order to expose the silicon where the source and drain regions will be located. Procedure: 1. Hard bake Bake at 150C for 2 minutes this strengthens resist to help prevent it from being eaten away by the oxide etch 2. Etch oxide Solution: 7:1 NH3F:HF Experimental etch rate: 640A/min 3. Strip resist Acetone soak with agitation, followed by IPA and Methanol rinse STEP 4: O2 Descum Remove any residual photoresist Objectives: The source and drain regions have been etched and the resist was removed with acetone. However, there could still be small amounts of resist over the source and drain regions. To remove this, we will perform an O2 descum. Procedure: Flow 30 sccm of O2 Process Pressure 0.5 Torr RF forward power: 150W Time: 1 minute STEP 5: Dope the Source and Drain Regions Objectives: The source and drain regions have been patterned and are ready to be doped using diffusion. Theory: We will be using spin-on dielectric to apply phosphorus to the wafers. Then they will be placed in the diffusion furnace for drive in. This process can be approximated using Fick’s second law. Boise State University NMOS Process Flow 2 Procedure: 1. 10 second BOE dip to remove native oxide from S/D regions 2. Measure resistivity of wafer prior to doping a. Results: 10.6-11 ohm-cm 3. Spin on dielectric a. Static dispense ~1mL b. Spin 3000rpm for 10 seconds 4. Soft bake for 10 min at 180C on oven 5. Drive-in in diffusion furnace a. Flow 40 sccm N2 b. Flow 10 sccm O2 c. Temp: 1200C d. Time: 1hr STEP 6: Strip Oxide Regrow Field Oxide Objectives: The objective of this lab is to strip the oxide layer that was used to as a diffusion mask whey doping the source and drain regions. Then a field oxide (~5000A) needs to be grown. Oxidation Process: Follow directions posted by furnace or on lab website to perform wet oxidation. Parameters using oxidation calculator for our furnace: 1000C for 1hr 25min flowing 3sccm of O2. STEP 7: Photolithography Level 2 Pattern Gate Regions Objectives: With the field oxide grown, the next step is to pattern the gates between the source and drain regions. Procedure: 1. Apply HMDS HMDS is an adhesion promoter and helps the photo resist stick to the surface of the silicon Spin at 500 RPM for 5 seconds followed by 5000 RPM for 35 seconds on Spin Coater 2. Apply positive photoresist (SPR-220-1.2) Immediately follow the HMDS with resist Spin at 3500RPM for 30 seconds Soft bake at 90 C for 1 minute to bake out liquid solvents Resist was ~1um thick as measured with Nanospec Boise State University NMOS Process Flow 3 3. Pattern Put wafer on to contact aligner chuck For 1st level photolithography, align to wafer flat Press “contact” on contact aligner panel Expose for 2 seconds at 11.8W/cm^2 4. Develop MF 26A developer for 20-25 seconds Quench in water STEP 8: Etch Patterned Oxide Hard Bake: 2 minutes at 150C on oven Strip Oxide/Resist: BOE dip for 7min 45 sec. Etch rate is ~640A/min PR stripper at 80C for 1 min to attempt to remove resist residue O2 descum as detailed in STEP 4 STEP 9: Grow Gate Oxide Oxidation Process: Follow directions posted by furnace or on lab website to perform DRY oxidation. Parameters using oxidation calculator for our furnace: 1025C for 1 hour flowing 3sccm of O2. Should yield ~500A gate oxide. STEP 10: Photolithography Level 3 Pattern Contacts Objectives: With the field oxide grown, the next step is to pattern the gates between the source and drain regions. Procedure: 1. Apply HMDS HMDS is an adhesion promoter and helps the photo resist stick to the surface of the silicon Spin at 500 RPM for 5 seconds followed by 5000 RPM for 35 seconds on Spin Coater 2. Apply positive photoresist (SPR-220-1.2) Immediately follow the HMDS with resist Boise State University NMOS Process Flow 4 Spin at 3500RPM for 30 seconds Soft bake at 90 C for 1 minute to bake out liquid solvents Resist was ~1um thick as measured with Nanospec 3. Pattern Put wafer on to contact aligner chuck For 1st level photolithography, align to wafer flat Press “contact” on contact aligner panel Expose for 2 seconds at 11.8W/cm^2 4. Develop MF 26A developer for 20-25 seconds Quench in water STEP 11: Etch Patterned Oxide Hard Bake: 2 minutes at 150C on oven Etch Oxide/Resist: BOE dip for 7min 45 sec. Etch rate is ~640A/min PR stripper at 80C for 1 min to attempt to remove resist residue O2 descum as detailed in STEP 4 STEP 12: Deposit Metal 1 1um of Al was deposited using the Varian Sputter Tool STEP 13: Photolithography Level 4 Pattern Metal 1 Procedure: 1. Apply HMDS HMDS is an adhesion promoter and helps the photo resist stick to the surface of the silicon Spin at 500 RPM for 5 seconds followed by 5000 RPM for 35 seconds on Spin Coater 2. Apply positive photoresist (SPR-220-1.2) Immediately follow the HMDS with resist Spin at 3500RPM for 30 seconds Soft bake at 90 C for 1 minute to bake out liquid solvents Resist was ~1um thick as measured with Nanospec Boise State University NMOS Process Flow 5 3. Pattern Put wafer on to contact aligner chuck For 1st level photolithography, align to wafer flat Press “contact” on contact aligner panel Expose for 2 seconds at 11.8W/cm^2 4. Develop MF 26A developer for 20-25 seconds Quench in water STEP 14: Etch Metal Hard Bake Bake at 90C for 2 minutes Metal etch: 1.5 minutes in Al etchant at 50C Al etchant is … Boise State University NMOS Process Flow 6