Micro-jet technique in flip-chip assembly [18, 19, 20]

advertisement

![Micro-jet technique in flip-chip assembly [18, 19, 20]](http://s3.studylib.net/store/data/007445904_1-d1d5881498361f2cbc3a4161e1e48ae9-768x994.png)

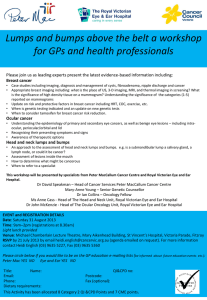

XXIV Conference of International Microelectronics and Packaging Society - Poland Chapter, Rytro 25-29 September 2000 Current Trends in Flip-Chip Bonding Technique for Multichip Modules – especially Micro-Jet Printing Barbara Bober, Andrzej Bochenek, Bronisława Olszewska-Mateja, Zbigniew Żaluk Institute of Microsystem Technology, Wrocław University of Technology ul. Z. Janiszewskiego 11-17, 50-372 Wrocław, Poland key words: multichip modules, flip-chip technique, bump, micro-jet Abstract Recent fast development in telecommunication and computer technique, where electronic equipment works on very high frequencies, forces design and manufacturing of multi-chip circuits with low transmission losses. These circuits consist of semiconductor integrated circuits in very high integration scale and multi-layer passive components. Multi-chip manufacturing applies mainly wireless flip-chip bonding, which has currently many varieties. In the paper the survey of flip-chip techniques, giving their main technological features, and the area of their applications is presented. The particular concern is going to micro-jet technique as the only method enabling in one technological process to produce multilayer passive circuits with resistive or dielectric and some optoelectronic components and solder bumps for flip-chip bonding. Advantages and drawbacks of micro-jet technology and the range of its applications are also underlined. Introduction Recently the most important direction of electronic industry development has been manufacturing of personal equipment that requires many features such as: far-gone miniaturization, high operation speed, functionality, reliability, creativity, low cost and environment friendly design. One of the key solutions fulfilling the above conditions is multichip circuits technology that applies very complex multilayer passive circuits as well as bare die semiconductor chips, in large or very large scale integration, connected into one functional module. The major advantage of multichip modules is ability to apply thick or thin film techniques for attachment of electronic integrated circuits, manufactured on silicon or gallium arsenide, or micro-mechanical components. The multichip technology cannot be realized without specific methods of interconnection, such as: modified wire bonding, tape automated bonding (TAB) and flip-chip bonding. Among these three techniques, flip-chip allows for the highest interconnect density and the lowest packaging profile. During the last decade there was unusual growth in the research and development of flip-chip technology. In comparison with traditional wire bonding and TAB, flip-chip enables obtaining shorter interconnections, lower inductance, higher frequencies, better noise control, higher density, greater number of inputs/outputs (I/O) and further miniaturisation of electronic devices. Multichip modules require substrates with very high density of conducting paths what can be realized by multilayer constructions with high resolution of interconnections. Such constructions can be made using the following technologies: multilayer laminated printed circuit boards, distinguished by the letter L (MCM-L); multilayer ceramic substrates, marked with C, produced by traditional thick film technology or by the newest technology of high or low temperature cofired ceramic substrates, HTCC and LTCC respectively; multilayer metal-dielectric thin film structures, distinguished by D (MCM-D), deposited on ceramic or silicon substrate. MCM-D technology is the most advanced. It enables to reach the highest interconnection density and transmitted signal frequencies even higher than 10 GHz. The schematic diagram of MCM-D is presented in Fig. 1. The multilayer thin-film circuit is laid on multilayer thickfilm substrate. Such a complex construction allows to combine advantages of two module types, MCM-D and MCM-C, and to produce substrates even with few dozen of levels, what significantly increases the packaging density and shortens transmission lines. Additionally, the following assembly methods are shown in Fig. 1: wire bonding, flip-chip bonding, tape-automated bonding. Fig. 1. Schematic drawing of a multichip module with connected thin- and thick-film circuits In the paper the main attention is paid to the flip-chip technology, pointing at many construction and technological solutions applied in industrial production, and at a great number of suggested techniques being under intensive investigations aiming at their application. The variety of different solutions is demonstrated in Fig. 2. Fig. 2. Block diagram of various assembly techniques in flip-chip technology Rigid bumps are usually made of Au, Ag or their alloys and also of NiAu double layer. Due to their low flexibility there is necessity to match the temperature coefficients of expansion of connected materials (the semiconductor die and the substrate). If not so, in the joint area too high thermal stresses would appear. Another sufficient method can be the application of conductive adhesives with very high flexibility for joining die bumps with pads on the substrate. Soft bumps are made from low-melting solders, commonly lead-tin alloys. Due to plastic deformation and bumps material creeping, thermal stresses disappear in the joint area. However, during the periodical and frequent temperature changes the fatigue failures of bumps can take place. Elastic bumps are usually produced as polymeric studs with metallic coating. Assuring constant pressure by applying thermally shrinking adhesives the rigid interconnection with substrate pads is reached. Due to their elasticity they are resistant to the thermal dilatations of substrates [1-Chapter 1]. There are five methods of bumps manufacturing mainly used, applying: ball thermo-ultracompression bonding, electrolytic or electroless plating, printing technology, vacuum film evaporation or sputtering, solder-jet dispensing. One of the major benefits of flip-chip technique is that all interconnections are manufactured in one go. It remarkable well speeds up the process of electronic circuits production. There are the following bonding methods applied: thermocompression, soldering, using adhesives. Further classification of flip-chip assembly techniques can be demonstrated by detailed description of various methods of bumps formation and ways of their interconnection. Exploitation of conventional ball thermocompression technique for bumps manufacturing The technical solution is based on the fact, that after the ball joint is formed on the conducting pad of a semiconductor device, the wire loop connection is not made, but wire breaking follows directly the first step of welding (Fig. 3.). Fig. 3. Conventional stud bumping In this way so-called stud bumps can be formed onto any kind of semiconductor structures, even onto those assigned for wire bonding. Die metallization made of aluminium films have not to be additionally prepared (cleaning, activating or thickening with another contact layer). The thermocompression process assisted with ultrasounds removes the aluminium oxide film and gives good contact of Au ball with Al pad, and good joint strength. Main advantage of this method is simplicity of bumps forming, leading to application of commonly used ball thermocompression bonding with no bonder modification. There is the difficulty that the gold wire breaks nonrepeatedly above the ball. The wire endings with uneven heights h (Fig. 3) make difficult the further assembly with the contact pads on the substrate. This problem can be solved in a couple of ways. The first consists of using, instead of pure gold wire, the gold wire doped with 1.52% Pd which gives better uniformity of the wire endings [1-Chapter 15, 2]. Our investigations [3] show that Pd addition significantly diminishes the recrystallization area of the wire near the ball during its melting. The wire breaks near the ball for there appears smaller zone of its softening. The stud bumps formed in the described way with short and uniform endings are particularly suitable for further assembly by thermocompression, aided at the same time with an insulating adhesive. It is based on the piercing of the thermally softened adhesive film by the bumps [1Chapter 15]. The adhesive film shrinks when setting after cooling and then the additional pressure onto the bumps appears from the substrate, what increases the reliability of obtained contact interconnections (Fig. 4). Fig. 4. Schematic process of thermocompression bonding across the isolating adhesive film It is very important to select suitable kind of adhesive which being nonhygroscopic, will not increase its volume, because increase of the adhesive volume causes disappearance of the contact between the bump and the substrate. The second way of obtaining uniform wire endings consists of electric discharge application at the moment of wire breakdown due to melting at the controlled height. The modified capillary is used containing a small sidewall electrode [1-Chapter 11] (Fig. 5). Application of laser beam for melting the strained wire at certain height gives successful results (Fig. 6). Fig. 5. Thermocompression capillary with sidewall electrode for melting the wire by electrical discharge Fig. 6. Schematic view of producing uniform endings of stud bumps by laser beam application Fig. 7. Flexible bumps attachment by fluxless soldering and using conductive adhesive The produced stud bumps with elongated heights are connected with conducting pads of a passive circuit by fluxless soldering or by using conductive adhesives (Fig. 7). The elongated stud bumps, due to their flexibility are resistant to the thermal dilatation of substrates. Another way of obtaining stud bumps with repeated heights is explained in Fig. 8 [4]. It is based on straining the wire by the capillary on the ball joint. After the ball connection is completed, the capillary is raised and the die is moved horizontally against the capillary, together with the sample holder, by the distance D of 0.51.5 times the wire diameter. In the second step of bonding, the capillary comes down and strains the wire pressing it to the ball. Next, the capillary is raised again and the wire breaks closely to the ball. In this way the uniform bumps height determined by the flattened ball level is obtained. Such stud bumps are particularly useful for assembling with anisotropic adhesives. Fig. 8. Consecutive steps of thermocompression bonding with wire straining Stud bumps manufacturing by the ball thermocompression bonding is the simplest method. However, because of the fact that each bump has to be formed separately, this technique can be used in small series production. Additionally, it can be suitable in the case, where for various reasons, semiconductor chips planned earlier to be assembled by wire bonding, have to be attached by flip-chip method. Typically, the pitch of stud bumps made of gold wire of 25 m in diameter is 250 m. It is determined by the ball dimension (3 times wire diameter) and the standard capillary size (Fig. 9a). In the paper [5] the innovation of wire welding process in the aim of decreasing significantly the pitch size of wire connections is presented. The capillary with the special shape was applied leading to the development of a new welding method called “encapsulated wire bonding” (Fig. 9b). According to the authors’ statement, using this new method, without diminishing the commonly used wire diameter (25 m), the in-line pitch of 55 m was achieved. Additionally, the strength of the ball connections was even greater than the strength of the bonds produced in the standard wire bonding process. The “encapsulated wire bonding” is going to be particularly useful for ultra fine stud bumps manufacturing and will allow for significant increase of interconnects density in flip-chip assembling. Fig. 9. Schematic view of thermocompression bonding: a) standard, b) “encapsulated” Solder bumps produced by evaporation and printing The conducting pads on semiconductor devices are made in the form of multilayer (e.g. Al+TiW+Au) that, among other functions, assures good wettability by solder. The layers of lead and tin are deposited by evaporation (usually through mechanical masks) on the bond pads. The solder content is controlled by the layer thickness. In order to increase the solder volume, the evaporated area is suitably greater than the bond pad and reached onto unwettable surface (Fig. 10a). In the next step, the chip is heated up and after melting of Pb and Sn films, blending takes place, followed by contraction of the produced alloy into spherical shape caused by surface tension forces (Fig. 10b). Fig. 10. Schematic manufacturing of soft bumps: a) evaporation of Sn, Pb layers, b) spherical bump formation by solder melting The bumps formed on the chip as described above can be connected with the passive substrate in two ways. The bumps made of low-melting solder (37/63 PbSn, Tm= 183C) are placed on the conducting substrate pads and heated up to the temperature above the melting point of the solder. The soldering process is conducted most frequently fluxlessly in a reducing atmosphere or by the method, called plasma assisted dry soldering (PADS) [6-10]. After these connections were made, the chip is lifted up in the controlled manner so that the melted solder gains hyperbolic shape and solidifies in this form (Fig. 11a). The hyperbolic shape of the joint ensures significantly its greater resistance to the thermal load fatigue than the cylindrical or barrel one. The detailed description of strains in solder bumps gives Lau in [11]. Fig. 11. Schematic view of interconnection of solder bumps with the substrate: a) by melting the bump material, b) by melting the additional solder In the case of interconnecting the silicon chip and the substrate with similar thermal expansion coefficients, the method with two solders can be applied (Fig. 11b). Then spherical bumps are made of the solder with higher melting temperature (e.g. 95/5 PbSn, T m 300 C), and the contact pads on the passive circuit are coated with the lower melting alloy (e.g. 37/63 PbSn, Tm = 183 C). The bumps do not undergo melting but are only wetted by additional solder. In both cases for the high density and precision of layers deposition the bump pitch can be 150 m. In circumstances, where the greater distance between the pads is tolerated (250400 m pitch) the solder bump forming process is realized by printing solder pastes on the passive substrate. Contact pads on the semiconductor chip are produced by evaporation of metals so as to ensure good wettability by the solder. Solder bumps produced by ball thermocompression technique The authors in [12, 13] manufactured bumps by thermo-ultracompression method applying SnSbAg solder alloy wire of 44.8 m in diameter. The electrical discharge melting of balls on the wire was conducted in Ar+H2 reducing atmosphere. The characteristic feature of this method is that the solder balls with increased hardness are rubbed by ultrasonic vibration, what makes possible to obtain the metallic connection directly with the Al pad on the chip in spite of its natural oxidation. The bumps produced in this way are transformed later by melting into spherical bumps (Fig. 12). It is worth emphasizing that this method does not require additional preparation of Al metallization. Fig. 12. Manufacturing steps of solder bumps by thermo-ultracompression method In the paper [14] the bumping technology applying the wire made of 98/2 PbSn soft solder is presented. In this case the Al metallization is covered with Ni-Au layer by electroless plating for obtaining good wettability by the solder. The thermocompression process is applied there to join initially the bump material with the contact pad. This technology for its greater complexity connected with traditional metallization process of contact pads, becomes too expensive for low quantity production. The positive side of this solution is decreased risk of the thermal strains arising in the joint for the great deformability of soft bumps and their material creeping. Generally, it is necessary to underline that the technology of wire solder bump formation gives wide flexibility in the solder content choice. The multiple solder compositions promising good weldability, wettability, suitable plasticity and environment friendly process can be applied without any complications. Usually alloys based on Pb or lead free based on Sn, In and Bi are used. The minimal bumps pitch depends on the capillary diameter and practically reaches the range of 200300 m. Solder bumps produced by plating method Electrolytic plating through photoresist masks is used to produce solder bumps on semiconductor wafers with electronic devices. Before plating the active wafer surface is metallized, usually by sputtering or evaporation (e.g. NiAu or TiWAu) to provide a current path to the individual bond pads. The plating deposits consecutively the metallic layers being constituents of the solder alloy. Next, the resist is removed and the conducting paths outside the bump areas are etched away. After that, melting of the plated layers gives spherical solder bumps. This is low cost method in the case of mass production, as all bumps, even on many wafers can be manufactured simultaneously in one plating process. On the contrary to the wire solder bumps formation, plating is more constrained in multicontent solder alloys formation because of complexity of the process increasing with any additional alloy constituent. Usually plating is reduced to two-component alloys. However, the essential advantage of the described method is obtaining the smaller bump pitch, for there the factor connected with the welding capillary does not exist. In [1-Chapter 15], the solder bumps formed by this method with 80/20 AuSn alloy reaching 20 m pitch are described. Hard bumps produced by plating method Two methods of bump formation can be distinguished: maskless, electroless plating and electroplating through photoresist masks (Fig. 13). Fig. 13. Schematic view of plated bumps manufacturing on silicon wafers: a) maskless and electroless plating, b) electroplating through photoresist masks In the first case the aluminium bond pads are activated by zincate pre-treatment, then covered with Ni and thin Au layer that prevents oxidation and ensures good wettability of bumps by the melted solder. The bumps growth during the plating process is multidirectional, so the bumps diameter is limited by their heights. The electroless Ni-Au plating is the cheapest way of bumps formation. In [1- Chapter 15] the authors consider the possibility of forming bumps with 7 m in height onto 5 m in diameter Al pads with 26 m pitch. The bumps produced in the described way can be soldered or connected with the passive circuit by a conductive adhesive. They can also be applied to assembling with anisotropic adhesives. Because of the fact that these bumps are relatively low, in the case of substrates thermal deformation, mainly shear strains arise in interconnections (Fig. 14a). To minimize these strains, it is recommended to use elastic joining materials (e.g. anisotropic adhesives with elastic particles). Fig. 14. Schematic explanation of possibility of the bond degradation due to the thermal deformation in the case of: a) low bumps, b) high bumps Another way of reducing thermal strains is underfilling the space between the die and the substrate with epoxy resin, which, in the great extent, adopts the strain and takes it off the joint. In the second method (Fig. 13b) the bumps are produced in the shape of metal posts called WIT (wire interconnect technology) by electrolytic plating through a thick photoresist mask. It is unidirectional metal deposition, so the bump diameter is not restricted by its height. In [1Chapter 13] the WIT posts produced from copper (Cu) on the silicon chip with Al pads coated with additional adhesive layer are presented. These particular WITs were approximately 10 m in diameter and 47 m tall with 30 m pitch. However, in the aim of receiving proper conditions for their soldering, 50 m pitch was applied. Such slim metal posts are characterized by pretty good elasticity what makes them more resistant to thermal deformation. Yet in the solder connection, unfavourable loads appear due to the posts bending, that causes breaking loose WIT in the soft solder (Fig. 14b). Taking this into account, the solders with increased strength and diminished plasticity should be applied there. Small dimensions of conducting pads taken up by the WIT result in reduction of the connection capacitance by an order of magnitude over any other method of chip attachment available today. Small solder volume and long distance of the solder from the active surface of the integrated circuit result in at least 3 orders of magnitude improvement with regard to particle radiation dosage on the active devices at the circuit surface. Rigid bumps cofired with the substrate The possibility of making bumps of conductive pastes dedicated for printing is considered in [15]. Multilayer glass ceramic substrates (LTCC) are placed on base plates made of special ceramic, which has small thermal expansion coefficient and is easy to crush. A plate of the same ceramic with holes spaced according to the circuit contact pads layout is placed on the top surface of the LTCC circuit. After lamination the holes are filled with a conductive paste (e.g. Ag) and then the whole structure is fired in the temperature depending on the applied glass ceramic green sheets. During the firing LTCC ceramic shrinks reasonably, even by more than 10%. This shrinkage could cause significant and difficult to control change of bump pitch, which must be compatible with contact pads of the semiconductor structures to be connected at a later stage. Such shrinkage takes place, but only in z direction, as both top and bottom ceramic base plates do not allow for shrinkage in x, y directions. Fig. 15. LTCC structure with cofired bumps before firing process After firing, base plates are crushed and their remains removed. Bumps formed in the top plate holes have the same pitch as the primary pitch of the holes. Using this method, the pitches of 500 m and 250 m were practically obtained. Research works in this area head mainly towards cheap technology of producing bumps by printing technique. Flip chip assembly using anisotropic adhesives [1] Usage of adhesives in flip chip technique is common. Conductive adhesives are used as well as dielectric underfill resins. An example of such connection is shown in Fig. 16. Fig. 16. Schematic view of classical interconnection with adhesive Application of anisotropic adhesives is the fundamentally different solution, which idea is presented in Fig. 17. Fig. 17. Schematic view of interconnection with anisotropic adhesive filled with Ag balls Flat rigid bumps are made on the passive substrate and on the semiconductor structure. Between their surfaces an anisotropic adhesive is introduced, which has dielectric properties in free state, but becomes a conductor being squeezed between bumps. This property has been achieved by filling resin with sphere-like silver particles of 10 m in diameter, covered by thin insulating layer made of plastic dielectric – Fig. 17. The isolated balls floating in resin do not conduct electric current. However, when crushed between bumps, they provide electric contact because the plastic insulation is squeezed out of their surface in the contact area. While external pressure is applied, thermal polymerisation of the resin and creation of the permanent electric contact take place. Stability of the contacts made in this way can be obtained when the resin does not extent its volume neither by thermal expansion nor by hygroscopicity. This condition is difficult to be fulfilled in practice. Fig. 18. Schematic view of interconnection with anisotropic adhesive filled with elastic balls Further improvement of this solution is application of plastic springing balls, covered first with thin silver layer and then with thin layer of plastic dielectric. The balls prepared in this way subjected to the pressure are elastically deflected and lose insulation – Fig. 18. Elastic strain ensures permanent contact even at clear increase of underfill resin volume resulting from thermal fluctuation. In order to ensure equal distances between bumps, there were additionally introduced spacer balls, made of hard dielectric, with diameters adequately smaller than elastic balls [16]. A variation of this technique consists of application of anisotropic conductive films (ASF) instead of anisotropic conductive adhesives (ACA). Properly prepared film used in the form of pad additionally simplifies assembly process [17]. In this technique good flatness of bumps surface is required. There is however the possibility of easy correction of bumps surface, e.g. golden ones, by initial squashing on flat model plates. Development of this technique and improvement of anisotropic adhesives (films) may cause that flip-chip assembly becomes exceptionally simple technological operation. This technique allows now to obtain pitches of 80100 m with elastic balls of 7-10 m in diameter. It is connected with the necessity of using quite big contacts, being multiple ball diameters in size. Only such condition ensures creation of electric contact in each junction. Micro-jet technique in flip-chip assembly [18, 19, 20] Micro-jet technique is the newest technology entering the production of VLSI electronic devices. It uses well known, especially in computers industry, ink-jet printing method. The method consists of very precise dosage of very small (picoliters) droplets of certain substance, using specialized, computer controlled jet (Fig. 19). In this way conducting paths, joining columns (vias), and insulating layers can be formed as well as bumps for flip-chip assembly on semiconductor structures, passive substrates and printed circuits. Fig. 19. Schematic view of a demand mode micro-jet printing system Very high flexibility of deposition in precisely defined places on substrates is obtained through computer control of the volume of disposed droplets (change of the volume 1 to 8 times) as well as dispensing frequency (up to 1000 droplets per second), and also precise, programmed substrate movement in x-y plane, closely connected with the dispensing programme. Research works in MicroFab Technologies, Inc. lead to improvement of “heads printing on demand” operating in temperatures up to 300 C for deposition of solders. There is also research conducted on technologies of various polymeric compositions deposition, conductive and dielectric ones, as well as other materials used in CSP and MCM electronic circuits manufacturing. Building machines in a form of a set of printing devices one can deposit sequentially consecutive layers and components of a circuit. Fig. 20 presents schematic diagram of a simplest example of such process. Complex circuits may be produced in a production line built of several printing stations. Transitions between stations can be used for operations not connected directly with printing, like e.g. thermal or UV polymerisation of deposited resin layer. In such a way very complex multilevel circuits can be produced, including such elements as: vertical columns joining levels, horizontal conducting paths, resistive tracks, insulating layers, capacitors, polymer waveguide joints, polymer microlenses, polymer elements with ferrite particles, encapsulating layers, solder bumps etc. Auxiliary materials can be deposited, like flux pastes, conductive adhesives etc. Fig. 20. CSP manufacturing method Joining columns as well as conducting paths and bumps are made of solders, but columns and paths are made of the solder with higher melting temperature than bumps, so that they do not melt during flip-chip assembly process. Solder bumps can be produced as very tall columns (25 m in diameter, 500 m in height) which allow for joining substrates not matching thermally. Resulting pitch is even smaller than 50 m. Deposition rate is high enough to consider this technique useful for mass production. Currently droplets disposing frequency above 1000 per second is being obtained, and substrate movement when “printing in fly” is 60 mm/sec. Making 400 bumps per second is no problem at all. Accuracy of components deposition reaches 10 m. There is still research conducted, heading towards improved printing efficiency and precision. Basic advantage of this technique is very high flexibility in programming of the technological process. It is reduced to another data set entry to the computer programme. This plays superb role in the case of preparing and investigation of prototype solutions. This technique can be also used for manufacturing circuits with similar, but slightly different parameters, creating their wide range without expensive modifications of technological processes. Contactless material deposition is less expensive, as neither masks nor screens are required. The process is environment friendly for there are no extra processes and chemical wastes. Conclusions Different flip-chip assembly methods were described. The main trends of flip-chip technology development were pointed out and many ways of their realization presented. None of these methods is particularly favoured. Certain application and requirements determine the choice. It is recommended to take into account such circumstances as: production volume, cost, operating conditions, complexity, and miniaturization scale. It is worth to note that information about operating conditions of an electronic circuit helps in choosing proper assembly technique ensuring good interconnection reliability. Continuous progress in electronic industry forces either further improvement of existing interconnection systems or search for completely new solutions. The paper shows how to design and manufacture interconnection systems what may help to make advances in electronics packaging and to obtain benefits in cost, performance, quality, size and weight. References J. H. Lau, (Editor),”Flip Chip Technologies”, McGrow-Hil, New York, 1995 T. Goldenberg, et al., “Ball Bumping – Procedure”, U.S. Patent 4.717.066, 1988 A. Bochenek, B. Bober, B. Olszewska-Mateja, “Evaluation of Ultrathermocompression FlipChip Bonds with Au and AuPd Wires”, XXII IMAPS – Poland Chapter Conference, pp. 103-106, 1998 A. Bochenek, M. Kramkowska, B. Olszewska-Mateja, “Montaż typu flip-chip z zastosowaniem zmodernizowanego zgrzewania termokompresyjnego”, VI Konferencja Naukowa Technologia Elektronowa, ELTE ’97,(in Polish), pp. 417-420, 1997 J. Song, A. Prabhu, I. Singh, L. Nguyen, G. Salvaduray,” Wirebond Integrity for Ultra Fine Pitch Devices”, International Symposium on Microelectronics, IMAPS ’99, pp. 388-395, 1999 G. Dishon, S. Bobbio, “Fluxless Soldering Process”, U.S. Patent 4,921,157,1990 S. Bobbio, Y. Ho, “Shared Loop and Multiple Field apparatus and Process for Plasma Processing”, U.S. Patent 4,738,761,1988 G. Dishon, S. Bobbio, N. Koopman, G. Rinne, “Plasma Assisted Fluxless Soldering”, NEPCON West Conference, 1992 N. Koopman, S.Bobbio, S. Nangalia, J. Bousaba, B. Piekarski, “Fluxless Soldering in Air and Nitrogen”, 43rd ECTC Conference, 1993 N. Koopman, S. Nangalia, C. Lizzul, S. Bobbio, J. Peterson, “Fluxless Soldering for Chip-onBoard and Surface Mount”, Surface Mount Symposium SMTA 1994, pp. 54-60, 1994 J. H. Lau, “Thermal Fatigue Life Prediction of Flip Chip Solder Joints by Fracture Mechanics Method”, Intern. J. Eng. Fracture Mech., vol. 45(5), pp. 643-654, 1993 T. Ogashiwa, H. Akimoto, H. Shigyo, Y. Murakami, A. Inoue, T. Masumoto, “Direct Solder Bump Formation on Al Pad and Its High Reliability”, Jpn. J. Appl. Phys. Part 1, vol. 31(3), pp.761-767, 1992 T. A. Scharr,R.K. Sharma, R.T. Lee, W.H. Lytle, “Wire Bumping Technology for Gold and Solder Wire Bumping on IC Devices”, 9th European Hybrid Microelectronics Conference, pp. 351-357, 1993 E. Jung, R. Aschenbrenne, E. Zakel, H. Reichl, “Flip Chip Interconnection to Organic Substrates: A Comparison between Adhesive Bonding and Soldering”, 10th European Hybrid Microelectronics Conference, pp. 44-53, 1995 M. Itagaki, N. Hase. S. Yuhaku, Y. Bessho, K. Eda, “A. Cofired Bump Bonding Technique for Chip Scale Package Fabrication Using Zero X-Y Shrinkage Low Temperature Cofired Ceramic Substrate”, Intern. J. Microcircuits and Electronic Packaging, vol. 21, No. 1, pp. 46-51, 1998 N. Shiozawa, K. Isaka, T. Ohta, “Electric properties of Anisotropic Conductive Adhesive Films”, Adhesives and Electronics ’94, VID/VDE, 1994 D. D. Chang, P. A. Crawford, J. A. Fulton, R. McBride, M. B. Schmidt, R. E. Simtski, C. P. Wong, “An Overview and Evaluation of Anisotropically Conductive Adhesive Films for Fine Pitch Electronic Assembly”, IEEE Transact. Components Hybrids, Manufact. Technol. Vol. 16(8), pp. 828-835, 1993 D. B. Wallace, D. J. Hayes, “Solder Jet Printing of Micropads and Vertical Interconnects”, SMTA’s Emerging Technology Symposium, 1997 D. B. Wallace, D. J. Hayes, “Solder Jet Technology Update”, Intern. J. Microcircuits and Electronic Packaging, vol. 21, No. 1, 1998 D. J. Hayes, D. B. Wallace, W. Royall Cox, “Micro-Jet Printig of Solder and Polymers for Multi-Chip Modules and Chip- Scale Packages”, International Conference on High Density Packaging and MCMs, pp. 242-247, 1999