d99113r1

advertisement

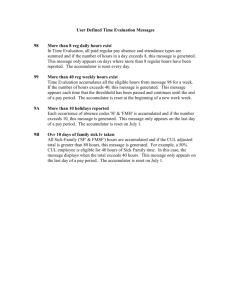

T13/D99113R1 A BETTER DEVICE RESET by Hale Landis hlandis@ibm.net 20 October 99 THE PROBLEM ATA/ATAPI has three reset functions: Hardware Reset, Software Reset and Device Reset. Some folks think the EXECUTE DEVICE DIAGNOSTICS command is a reset but it really is not even though is shares some of the same execution protocol that Software reset uses. The problem is that the Device Reset function, the DEVICE RESET command, was poorly defined, repugnant to most interface device designers and is not adequate to perform the job that it should really perform. This proposal defines a new way to initiate a Device Reset function. The primary features of this new method are: Doesn’t use the Command register. Can reset a device even when the device is not currently selected. Can reset one device or both devices at the same time. This new Device Reset will allow a host to do things that are currently difficult, such as: a) wake up a sleeping device without selecting the sleeping device or changing the current state of the other device, b) reset a device while not affecting the status of any overlapped or queued command in progress on the other device. THE PROPOSAL Bits 5 and 4 of the Device Control register are changed from reserved to the following: Bit 5 – DR1 = This bit initiates the Device Reset function for device 1. Bit 4 – DR0 = This bit initiates the Device Reset function for device 0. To initiate the Device Reset function the host sets one or both of these bits to 1 and then to 0, just as is done for the SRST bit. A device supporting this proposal will execute the Device Reset protocol as currently defined. This functionality will be mandatory for both ATA and ATAPI devices. Device Reset would continue to be the lowest priority reset. To distinguish a Device Reset initiated by these bits from a Device Reset initiated by the DEVICE RESET command (08H command code), this method will be known as a “hardware Device Reset” and the DEVICE RESET command method will be know as a “software Device Reset”. NOTE: Initiating Device Reset in both devices at the same time is NOT the same as doing a Software Reset (SRST) because Device Reset does not change the DEV bit and it does not toggle PDIAG. Note: If the host initiates a Device Reset on the device that is not currently selected the host must follow the recommendations found in clause 9.16 in order to determine when the Device Reset has been completed. DETAILS Current text: 7.9.5 Functional description This register allows a host to software reset attached devices and to enable or disable the assertion of the INTRQ signal by a selected device. When the Device Control register is written, both devices respond to the write regardless of which device is selected. When the SRST bit is set to one, both devices shall perform the software reset protocol. The device shall respond to the SRST bit when in the SLEEP mode. When the nIEN bit is set or cleared, both devices shall disable or enable assertion of the INTRQ signal. 7.9.6 Field/bit description 7 r 6 r 5 r 4 r 3 r 2 SRST 1 nIEN 0 0 Bits 7 through 3 are reserved. SRST is the host software reset bit (see 9.2). nIEN is the enable bit for the device interrupt to the host. When the nIEN bit is cleared to zero, and the device is selected, INTRQ shall be enabled through a tristate buffer and shall be asserted or negated by the device as appropriate. When the nIEN bit is set to one, or the device is not selected, the INTRQ signal shall be in a high impedance state. Bit 0 shall be cleared to zero. New text: 7.9.5 Functional description This register allows a host to device reset and software reset attached devices and to enable or disable the assertion of the INTRQ signal by a selected device. When the Device Control register is written, both devices respond to the write regardless of which device is selected. When the DR1 bit is set to one device 1 shall perform the device reset protocol. When the DR0 bit is set to one device 0 shall perform the device reset protocol. Device 0 shall ignore the DR1 bit and device 1 shall ignore the DR0 bit. The DR1 bit is ignored by device 0 when device 0 is responding for device 1 and device 1 is selected, When the SRST bit is set to one, the DR1 and DR0 shall be ignored and both devices shall perform the software reset protocol. The device shall respond to the DR1, DR0 and/or SRST bit when in the SLEEP mode. When the nIEN bit is set or cleared, both devices shall disable or enable assertion of the INTRQ signal. 7.9.6 Field/bit description 7 r 6 r 5 DR1 4 DR0 3 r 2 SRST 1 nIEN 0 0 Bits 7 through 6 are reserved. - DR1 is the host device reset bit for device 1 (see 9.11). - DR0 is the host device reset bit for device 0 (see 9.11). SRST is the host software reset bit (see 9.2). nIEN is the enable bit for the device interrupt to the host. When the nIEN bit is cleared to zero, and the device is selected, INTRQ shall be enabled through a tristate buffer and shall be asserted or negated by the device as appropriate. When the nIEN bit is set to one, or the device is not selected, the INTRQ signal shall be in a high impedance state. Bit 0 shall be cleared to zero. 7.1 Device addressing considerations Table 10: Change the text “Place new data into the Device Control register and respond to the new values of the nIEN and SRST bits.” with the text “Place new data into the Device Control register and respond to the new values of the DR0, DR1, nIEN and/or SRST bits”. Table 11: Change the text “Place new data into the Device Control register and respond to the new values of the nIEN and SRST bits.” with the text “Place new data into the Device Control register and respond to the new values of the DR0, DR1, nIEN and/or SRST bits”. Table 13: Change the text “Place new data into the Device 0 Device Control register and respond to the new values of the nIEN and SRST bits.” with the text “Place new data into the Device Control register and respond to the new values of the DR0, DR1, nIEN and/or SRST”. Table 14: Change the text “Place new data into the Device Control register SRST bit and respond only if SRST bit is 1.” with the text “Place new data into the Device Control register DR1, DR0 and SRST bits and respond only if SRST bit is 1 or if device 1 and the DR1 bit is 1 or if device 0 and the DR0 bit is 1.”. In the Table 15, change the text “Place new data into the Device Control register SRST bit and respond only if SRST bit is 1.” with the text “Place new data into the Device Control register DR1, DR0 and SRST bits and respond only if SRST bit is 1 or if device 1 and the DR1 bit is 1 or if device 0 and the DR0 bit is 1.” 8.7.8 Description Add the following text to the description of the DEVICE RESET command: The DEVICE RESET command may become obsolete in future ATA/ATAPI standards. Devices and hosts complying to this standard shall implement the DR0 and DR1 bits of the Device Control register to implement the device reset function. 9.11 Device Reset protocol Current text: This class includes: DEVICE RESET If the host asserts RESET- before the device has completed executing a DEVICE RESET command, then the device shall start executing the hardware reset protocol from the begining. If the host sets the SRST bit to one in the Device Control register before the device has completed executing a DEVICE RESET command, the device shall start executing the software reset protocol from the beginning. The host should not issue a DEVICE RESET command while a DEVICE RESET command is in progress. If the host issues a DEVICE RESET command while a DEVICE RESET command is in progress, the results are indeterminate. Figure 40 and the text following the figure describe the DEVICE RESET command protocol for the host. Figure 41 and the text following the figure describe the DEVICE RESET command protocol for the device. New text: This clause describes the protocol for processing of device reset. The host should use the DR1 or DR0 bits of the Device Control register to initiate a device reset. The host may also use the DEVICE RESET command, however, the DEVICE RESET command may become obsolete in future ATA/ATAPI standards. If the host sets SRST in the Device Control register to one before a device has completed the device reset protocol, the device shall execute the software reset protocol. If the host asserts RESET- before a device has completed the device reset protocol, then the device shall execute the hardware reset protocol from the beginning. The host should not initiate a device reset while the BSY bit is set to one in either device Status register as a result of executing the hardware or software reset protocol. The host should not initiate a device reset while a device reset is in progress. If the host initiates a device reset to a device while that device has a device reset in progress, the results are indeterminate. A device shall execute the Device Reset protocol if any of these conditions are true: - The selected device shall execute the device reset protocol, if supported by the device, when the host writes the DEVICE RESET command into the Command register - Device 0 shall execute the device reset protocol when the host writes the DR0 bit of the Device Control register to one. - Device 1 shall execute the device reset protocol when the host writes the DR1 bit of the Device Control register to one. Figure 40 and the text following the figure describe the DEVICE RESET command protocol for the host. Figure 41 and the text following the figure describe the DEVICE RESET command protocol for the device. And update the state diagrams to should the three ways a device reset can be initiated. /end/