EE5323 VLSI Design I using Cadence

Setup Your Account (VLSI Lab)

Example: Design and Simulation of an Inverter

o Create a library for your new design

o Create a new cell

o Design your circuit

Place components

Connect components

o Grid control for schematic

o Add pins

o Generate netlist files

o HSPICE simulation

o Use scope to view results

o Work with symbols

Create a new symbol

Use the symbol in other schematics

Layout of the Inverter

o Create a layout view of your cell

o Layout the components for your circuit

o Grid control for layout

o Route and add pins

o Extraction and LVS

Extract the layout

Layout Versus Schematic (LVS)

o Post-Sim

o Instantiate cells

o Edit hierarchical designs

0. Setup Your Account (VLSI Lab)

1) Copy the folder /home/class/ee5323ta/ee5323 to your home

directory using the following command:

% cp -r /home/class/ee5323ta/ee5323 ~/.

2) Now, you are ready to invoke cadence. Make sure you invoke

cadence from your cadence directory which is ~/ee5323/cds_ncsu:

% cd ~/ee5323/cds_ncsu

% icfb

In the future you should always run your Cadence under cds_ncsu

directory. This should bring up your CIW (command Interface

Window) and library Manager.

1. Example: Design and Simulation of an

Inverter

This example will help you familiarize yourself with Cadence. This

will show the most important commands and steps used when working

with schematics in Cadence. As an example, you will design a simple

inverter and simulate the delay of it.

Before starting with the design example, there are a couple things

worth mentioning:

Most of the commands in Cadence can be accessed in multiple

ways: pull-down menus, shortcut keys, buttons in toolbars, etc.

In the described example, all the commands are referenced by

their position in the pull-down menus. The shortcut keys can

be found from the pull-down menus as well. Below lists some

most frequently used shortcut keys:

q – Edit property of object

i – Create instance

w – Add wires

m – Move

c – Copy

s – Stretch

r – Rotate

z – Zoom in

Z – Zoom out

u – Undo

X – Descend edit

x – Descend read

b – Return

e – Display

The most frequently used key in Cadence is ESC. It is used to

cancel on-going commands.

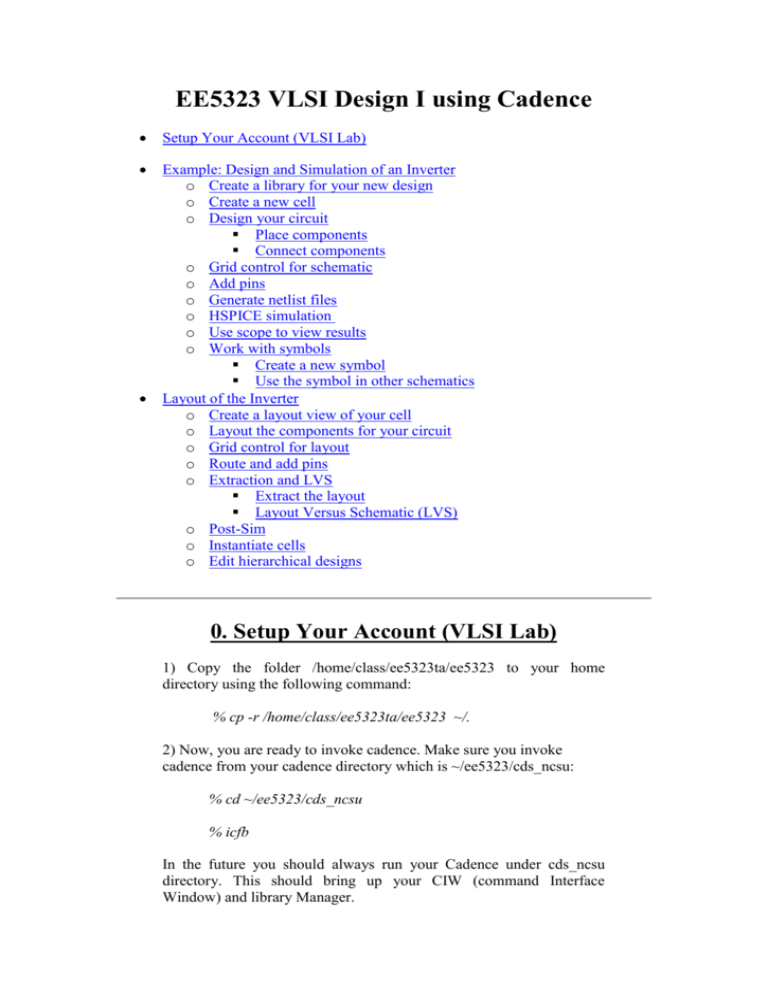

The following picture shows the schematic of an inverter, which is

ready for netlist extraction. The following section explains how to

draw it in Cadence.

1.1 Create a library for your new design

From the library manager window:

File->New->Library

Type a new name, such as TEST, click OK.

In the pop-up window, choose “Attach to an existing tech library”.

Then, choose “NCSU_TechLib_tsmc03d”). Click OK.

1.2 Create a new cell

In the Library Manager:

Highlight your new library (TEST if that is what you chose).

File->New->Cellview

Choose library TEST, cell name “inverter”, view name

“schematic”, and Open with “Schematic L”. Click OK.

Click “Always” if “Upgrade License” warning message shows

up.

A schematic window will open.

1.3 Design your circuit

1.3.1 Place components

For this inverter, you will need an nmos transistor, a pmos transistor,

power and ground nodes.

From Schematic window,

Create->Instance

Add Instance and Component Browser windows will open.

Make sure the Library in the Component Browser is set to

NCSU_Analog_Parts. Use the Component Browser window

and click on N_Transistors, then select nmos4 and place it.

Use the same procedure but click P_Transistors, select and

place pmos4, from library NCSU_Analog_Parts.

Also, from the library Basic, get the symbols for VDD and

GND (they define the net names for the power and ground

nodes).

If you make any mistake, you can always use:

Edit->Delete or

Edit->Rotate or

Edit->Move or

Edit->Stretch

To change the properties of some of the components:

Edit->Properties->Objects

Select the pmos4 transistor, and change the following

parameters:

Width: 960.0n M

Length: 240.0n M

Make sure you change the Width and Length boxes to these values, not

the Width (grid units) and Length (grid units) boxes.

NOTE: For this design kit you can only set transistor lengths and

widths in multiples of grid units (.06uM). Keep this in mind while you

are designing your circuits.

Similarly, set the dimension of the nmos transistor to:

Width: 480.0n M

Length: 240.0n M

The width and length values can also be set when you are adding the

instance in the previous step.

1.3.2 Connect components

Connect the component terminals as shown in the figure above using:

Create->Wire (narrow)

1.4 Grid control for schematic

In schematic and symbol, the mouse pointer only snaps to a certain

spacing of location. The spacing can be set by:

Options->Display

In the Grid Control panel, “Snap Spacing” controls the

resolution of mouse snap in schematic and symbol. In default,

Snap Spacing is set to 0.0625μm for schematic. You can

change the setting to a smaller value to get a more smooth

range of mouse snap.

1.5 Add pins

By adding pins, you can identify the I/O ports of the schematic. At a

later stage, you can also use pins as connection points for hierarchical

designs. To learn more about this, see the section about creating

symbols.

Create->Pin

Type the pin name, such as VIN, select the direction as "input",

and place it in the schematic. Do the same for VOUT, selecting

the direction as "output".

1.6 Generate netlist files

In the Schematic Window:

Design->Check and Save

There should be no errors. Warnings such as "Solder dot on

cross over" are okay.

Launch->ADE L

The window of Cadence Analog Design Environment will show up.

Make sure the current simulator is set to hspiceD:

Setup->Simulator/Directory/Host

Set the simulator to hspiceD.

Simulation->Netlist->Create

A new window will pop up showing the generated HSPICE netlist.

You may save this file by clicking the menu bar:

File->Save As.

Specify the full path name and file name in the Save As window.

For example, if we want save the file into a folder named

"simulation" under folder "~/ee5323/cds_ncsu", we should type

in "~/ee5323/cds_ncsu/simulation/inverter.sp". And the file

name is "inverter.sp". If you do not provide a path before file

name, the file will be saved under the folder where you start

your Cadence. To build a new folder for simulation, you can

bring up a new Xterm window and change directory into

"cds_ncsu" and make a directory by typing the command under

the Linux prompt:

%mkdir simulation

Now we have the netlist file that is ready for editing and simulating.

Under the Linux prompt, type in the following command. You can use

other text editor you are familiar with.

%emacs inverter.sp

A new window like the one below will pop up and load the

"inverter.sp" for editing.

Delete the simulation setup command except circuit netlist. The

commands you need to delete are:

.TEMP 25

.OPTION

+

ARTIST=2

+

INGOLD=2

+

MEASOUT=1

+

PARHIER=LOCAL

+

PSF=2

.END

The deleted command will be put into another file.

Now, your inverter.sp file will look like:

Save the buffer and Exit the editor.

Now use the Emacs editor again to create another HSPICE file named

“runinv.sp” for simulation as below. Both model file “model.m” and

generated circuit netlist "inverter.sp" are called from this file. The

model file "model.m" should have been copied into the folder

~/ee5323/cds_ncsu/. The “inverter.sp” file has already been saved into

the current folder in the previous step.

*test inverter

.temp 25

.options accurate

.options post=2

.lib '~/ee5323/cds_ncsu/model.m' pmos

.lib '~/ee5323/cds_ncsu/model.m' nmos

.include inverter.sp

v1 vdd! 0 2.5v

v2 vin 0 pwl 0ns 0 1ns 0 1.02ns 2.5 2ns 2.5 2.02ns 0 2.5ns 0

.op

.tran 0.01n 3ns

.end

Save the above command into “runinv.sp” and Exit the editor.

The reason for using a separate file for simulation is because

later on your circuit netlist may change, but the simulation file

can be kept the same.

1.7 HSPICE Simulation

The "runinv.sp" file includes the circuit netlist, technology models,

supply voltages, input signal timing and simulation time. The setup for

simulation is now complete. At the Linux command type in

% hspice runinv.sp

And, if you have followed all the steps above correctly, you should get

the following message.

Using: /home/vlsilab/synopsys/hspice_2007.03SP1/hspice/linux/hspice

****** hspice - Z-2007.03-SP1 32-BIT (May 25 2007)

20:53:34 09/07/2007 linux

Copyright (C) 2007 Synopsys, Inc. All Rights Reserved.

.....

.....

.....

***** job concluded

1 ****** hspice - Z-2007.03-SP1 32-BIT (May 25 2007)

20:53:34 09/07/2007 linux

******

*test inverter

****** job statistics summary tnom= 25.000 temp= 25.000

.....

.....

.....

job started at 20:53:34 09/07/2007

job ended at 20:53:34 09/07/2007

Init: hspice initialization file:

/home/vlsilab/synopsys/hspice/hspice.ini

lic: Release hspice token(s)

hspice job runinv.sp completed.

Fri Sep 7 20:53:34 CDT 2007

The important message is the “job concluded”. If the job is “aborted”,

you will have to debug the errors in your netlist. For detailed HSPICE

command and syntax, the readers are referred to the HSPICE manual

on the class webpage.

1.8 Use scope to view results

To view the results, we have to start scope. For this, at the Linux

command prompt type in

% scope

From the menu bar

File->Open->Plotfiles

In the opened window, select “HSPICE

(*.tr*,*.ac*,*.sw*,*.ft*)” for “Files of type” and then select the

"runinv.tr0" file. Clicking Open brings up the results browser

window.

In the results browser window, double click "v(vin)" and "v(vout)" to

plot the waveforms of the signals.

You can measure the propagation delay by

1) Drag the v(vout) signal into the same window as v(vin) signal;

2) Select both "vin" and "vout" signals using control key;

3) Click the second but last button on the tool bar;

4) Drag the start and end circles to the location you want to measure;

1.9 Working with symbols

If you want to use your design in other schematics, you need to create

a symbol for it. This is equivalent to the use of sub-circuits in HSPICE.

Using hierarchy in your project makes it easier to organize.

1.9.1 Create a new symbol

Save the schematic before you create its symbol:

File->Check and Save

Create->Cellview->From Cellview, click OK.

A new window will open with the symbol view. By default, the symbol

shape is a rectangle, but you can change it. Since this design is an

inverter, we will draw a triangle and put a small circle at the output. To

do this, you will want to delete the green rectangle, draw the new

shape, and move the terminals to new positions. Use Create->Shape to

draw a triangle and place a circle. There are several shapes available:

line, rectangle, circle, etc.

You will also need to change the Selection box (the red rectangle),

which defines the limits of the symbol. This can be done by stretching

the Selection box. Figure below shows an example of the inverter

symbol:

Don't forget to check and save.

1.9.2 Use the symbol in other schematics

Create a new schematic, using the instructions described in Create a

new cell. Give a name such as test_inverter.

You place this symbol in the new schematic in the same way that you

placed any other components, with:

Create->Instance

This time change the Library to your library TEST and click on

inverter. Your symbol should be here.

Now, you can define power supplies in the new schematic. If you place

new VDD and GND components, they will be implicitly connected to

the correspondent VDD and GND components that are inside the

inverter.

To move in the hierarchy, select the inverter, and then:

Edit->Hierarchy->Descend Edit

You can choose the schematic or the symbol for editing.

To return to the previous schematic, use:

Edit->Hierarchy->Return

2. Layout of the Inverter

This example will help you to create a layout for the inverter you

designed in the first example. There are many considerations to take

into account when deciding how to do a layout. This is NOT an

example on layout techniques, but more of a generalized example to

help get you familiar with Virtuoso and laying-out some basic

components.

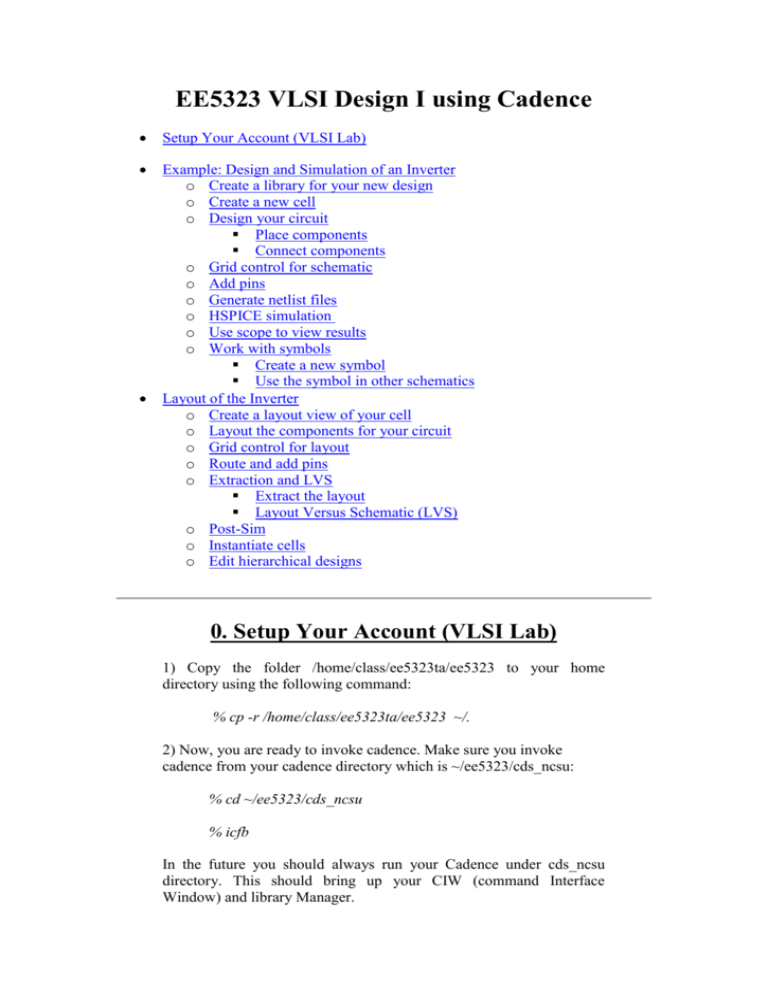

The following picture shows a layout for the inverter. The following

sections explain how to make each of the separate components in

Virtuoso.

2.1 Create a layout view of your cell

In the Library Manager:

Highlight your inverter schematic library (TEST if that is what

you chose).

Launch->Layout XL

Click OK and OK again. Click “Always” if there is any license

upgrade message.

A layout-editing and a LSW window will open up.

2.2 Layout the components for your circuit

For this inverter we will need to layout an nmos transistor and a pmos

transistor.

When laying-out MOSFETs, we actually have preset cells which we

can draw from.

From the Layout window,

Create->Instance

Browse the library name, choose your library name

(NCSU_TechLib_tsmc03d), choose nmos from the Cell, and

layout from the View. In the Create Instance window, setup the

parameters: Width and Length the same as what we have in the

schematic.

When making MOSFETs you can create a single transistor or create

fingers or create multiple transistors at once. Fingering creates

transistors which are connected in series, multipliers create transistors

which are connected in parallel. For now, leave the "multiplier" and

"fingers" unchanged at the default values of 1.

You can now place the nmos layout.

Clicking SHIFT-F will show all levels and allow you to view

all layers inside the cell you just placed (CNTRL-F will change

back to just showing the top level).

Following the same steps listed above, instantiate a pmos.

You can rotate the devices by

Edit -> Move (or just press "m")

Click on the transistor, and right click on it.

Now we need to connect together the gates.

In the LSW window change the current layer to poly (drw).

Create->Shape->Rectangle

Now draw a poly path connecting the gate of pmos to that of

the nmos.

It's always a good practice to stop and do a DRC check before placing

more components to your diagram. To do so, clicking on:

Verify->DRC...

A window that looks like the one below opens up. Set the rules

library to: NCSU_TechLib_tsmc03d. The DRC will now run,

and if everything is okay, it should finish with the message

below.

If there are errors, the message will contain statistics about which rules

were violated. To see where and why, you can use one of the following:

Verify->Markers->Explain:

Click on one of the errors (those white boundary area) in the

layout window. A text window will open with a description.

Verify->Markers->Find:

A dialog window will open. You can use the buttons Apply,

Previous and Next to go through the list of errors. If you select

the “Zoom To Markers” button, the layout window will zoom

in the corresponding error.

2.3 Grid control for layout

Similar to the schematic, the mouse pointer only snaps to a certain

spacing of location. The spacing can be set by:

Options->Display

In the Grid Control panel, the “X Snap Spacing” and “Y Snap

Spacing” control the resolution of mouse snap in layout. In

default, “X Snap Spacing” and “Y Snap Spacing” are set to

0.06μm. You should keep the default setting in your layout

because in this design kit (NCSU_TechLib_tsmc03d), DRC

rule requires the edge of the drawing (e.g. rectangle wire) lies

on a grid which is a multiple of 0.06μm. Keeping this default

setting can help you avoid the DRC rule violation.

2.4 Route and add pins

Now that we have all the components we need to make our inverter,

we can simply move them around and route the correct connections.

As mentioned earlier, this example is less focused on the techniques

used for layout, and more on how to create some general components

and get the reader familiar with using the tool. However, here are a

couple quick pointers:

When putting together your layout, place large metal rectangles

along the both sides of the diagram as your VDD and GND

rails. Try to place all of your layout within these rails. Also,

when connecting to these (or any routing connection) it is

almost always a good idea to put as many via connections as

possible. You can use the same multiple contact placement to

make this fast and neat.

Though it's not really obvious from this example, it is also good

practice to try and make your layout as symmetric as possible.

When routing large layouts it's a good idea to try and keep

track of what you are routing with. Route with poly as little as

possible since its resistance is higher than metal. It also helps to

set some general directions for different layers. For instance,

for horizontal traces use metal2, 4, for vertical traces use

metal3,5. Metal 1 can be used for both directions. This will

help keep your layout neat and organized.

First, you will need to create the supply rails and then connect together

the sources and drains to these power supply nodes.

In the LSW window, change the current layer to metal1 (drw).

Create->Shape->Rectangle

Draw two wide supply rails for VDD and GND on each side of

the diagram. Then, draw a metal1 line connecting both sources

of the transistors. Draw another metal1 line from drain of pmos

to the VDD supply rail. Now, create a similar line that connects

the drain of nmos to the GND rail.

Next, route the connections to the input node.

In the LSW window change the current layer to poly (drw).

Create->Shape->Rectangle

Draw a rectangle away from the poly line connecting the gates.

In the LSW window change the current layer to metal1 (drw).

Create->Shape->Rectangle

Draw a metal line that overlaps the previous poly line. The

overlapping area should be at least 0.24uM by 0.24uM which is

the minimum size of the contact between metal1 and poly

layers.

Place a via between the two layers. (Clicking Create->Via and

choose M1-POLY)

Next, route the connections to the output node.

In the LSW window change the current layer to metal1 (drw).

Create->Rectangle

Draw a metal line that overlaps the metal1 line connecting the

sources.

After routing all your connections for the inverter (do not forget to do

DRC often), you simply need to add pins for VIN, VOUT, VDD, and

GND.

Create->Pin

Type the Terminal Name, such as VIN (or VOUT).

Select the I/O Type, such as "input" or "output" (or inputOutput

for VDD and GND).

Check the Display Pin Name box.

Check “rectangle” for Mode.

Click the “Display Pin Name Option…” and set the layer to be

Text (dg) and the text height to be 0.5 or larger.

Simply place the pin overlapping with metal1 and place pin

label where you want them. Note the pin layer need to match

the metal layer that it is on, for example, metal1(dg).

Similarly, create pins for VDD! and GND!. Note that in schematics,

your VDD and GND were taken from library Basic. They are

considered as global variables. Therefore, a “!” has to be added in the

label on your layout to match that given from your schematic netlists.

Without “!”, the LVS will complain a mismatch in ports. If your VDD

and GND were added as pins by yourself in the schematic, you just

need to label them in layout with the same name as your schematics.

To determine whether you need “!” for your power rails, you can

check the netlists from your schematic.

Finally place body contacts on the VDD line and the GND line.

Create->Via

Find M1-N for VDD (or M1-P for GND).

After hitting ENTER, you may place it on the supply rails. Via

M1-N has to be placed within the n-well for your pmos. You

may expand the n-well to cover the M1-N via as shown in the

inverter layout example above.

You can run the DRC again to make sure no errors are seen in the

layout.

Your layout now should look similar to our layout example above.

2.5 Extraction and LVS:

2.5.1 Extract the layout:

The extraction tool identifies devices and nodes in the layout. It creates

a special view, named “extracted”, which contains this information.

Later, this view is required for netlist generation, and can be used by a

simulator or by the LVS tool.

Verify->Extract...

Again set the rules library to NCSU_TechLib_tsmc03d. If you

want to include parasitic capacitance in the extraction press the

“Set Switches” button and select “Extract_parasitic_caps”.

Press OK.

The extraction should finish with the message:

If there are any errors, you can learn more about them in the same way

described earlier for DRC errors.

To finish the extraction, you have to go to the Library Manager and

open the view “extracted” of the inverter and then use the same

procedure stated in schematic netlist extraction to create the netlist

from the extracted layout. To be more specific, you open the Analog

Environment window from the Tools menu....(click here for detail)

2.5.2 Layout Versus Schematic (LVS)

The LVS tool is used to compare the layout with the schematic,

identifying any circuit related differences that might exist between

these two views. It reports circuit nodes and device sizes. You can

invoke the LVS tool from either the window containing the layout

view or the extracted view. First we need to setup some LVS

parameters.

NCSU->Modify LVS Rules...

Set all the boxes except the Ignore FET Body Terminal.

Now we can run LVS.

Verify->LVS...

The LVS dialog window opens up.

Most of the fields should be automatically filled out. Make sure that

everything is consistent (view schematic is for schematic netlist and

view extracted is for the extracted netlist).

In the Rules File field, type “divaLVS.rul” and the rules library is

again your technology library. Make sure Rewiring, Device Fixing, and

Terminals are all selected.

Click on the Run button to start the LVS job. Wait until it finishes. A

message window will pop up on the screen when the LVS verification

is complete. To view the results of the LVS job, click on the Output

button. A text window containing the file “./LVS/si.out” will open. The

result of the comparison is stated in one of three possible sentences:

1. The net-lists match.

2. The net-lists failed to match.

3. The net-lists match logically but have mismatched parameters.

In the first case, you can go celebrate. In the second case, one or more

nodes in your layout or in your schematic have a mistake. In the third

case, all the nodes are correct, but one or more devices have the wrong

size. The output file also contains a list of devices, nodes and terminals

for the layout and for the schematic. From this list, you can find how

many errors exist, and in which view.

For both of the last two cases, it is necessary to track down the

problem. Unfortunately, this is not a straightforward procedure, but

more of a debugging process. The following are tools that are available

to assist you in this:

In the LVS window, click on the Error Display button.

Use the buttons on the top of the window (First, Next, etc) to

highlight the errors. You can select which type of error you

want to see from the bottom part of the window. Note that the

highlighted errors will appear in the “active window”. You can

make the schematic window or the extracted window active by

clicking on one of them. A window is active if the status bar at

the top is green.

In the LVS window, click on the Info button.

As an example, if you have mismatched parameters in your

layout, you can click on the Audit button in either extracted or

schematic sections.

2.6 Post-Sim

Since we have successfully matched our schematic to our layout, we

could find out how different the layout is from the schematic by

running another HSPICE simulation using the netlist extracted from

the layout. For simulation....click here for detail.

2.7 Instantiate cells

To make the layout design simpler, it is possible to define blocks

which are to be used several times in the same layout. The following

example describes how to do this for a transistor.

Design or copy one of your transistors to a separate place. Select the

whole transistor and choose:

Edit->Hierarchy->Make cell

Fill in a name for the cell, for example, `nmos_10_1', (which

stands for w=10u and l=1u, just to keep track of what it is).

You will see the cell as a red outlined box. The contents of this box are

now in a different hierarchy level, and can only be accessed with

hierarchy commands.

This cell exists now in the library manager. To place more copies in

your layout, select:

Create->Instance

Type the name of the library, cell and view, and place it with

the mouse.

You can also create arrays of cells, which can be used, for example, to

make transistors in parallel. When creating an instance, the form gives

you options to change the number of columns or rows, and the distance

between the elements.

To return one of the cells to normal layout rectangles, select the cell

and use:

Edit->Hierarchy->Flatten

2.8 Edit hierarchical designs

When you want to edit a cell, you have to navigate between different

hierarchy levels. This is done by selecting the desired cell and using:

Edit->Hierarchy->Descend Edit: Descends to cell.

Edit->Hierarchy->Edit in Place: Allows editing while looking

at the top level.

Design->Hierarchy->Return: Returns to top level.

Of course, you can also edit the cell by opening it from the library

manager.

To see all the hierarchy levels, you can use the shortcut key F. To view

only the top level, use ^f. This information can be accessed from the

menu Options->Display. In the dialog box, there is a field with the

“Start” and “Stop” display levels. To display all layers, set the stop

levels to a higher value such as 10.