arlsow1

advertisement

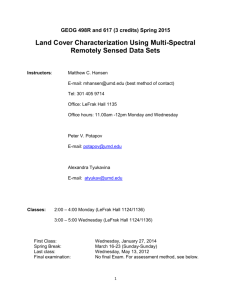

Annual Program Plan—Year One—for Physics-Based Modeling and Characterization of Wide Bandgap Semiconductor Devices Background The development of high-temperature, high-power, high-voltage devices using SiC in place of Si is very promising. However, before such devices can be successfully fielded, a number of important issues must be addressed. For example, in SiC MOSFETs, less than optimal channel mobility results from high levels of interface traps and nearinterfacial fixed oxide traps, as well as surface roughness. The threshold voltage is not optimized due to charge trapping in these states. Transient operation of these solid state switches is also affected by these traps. Time-dependent wear-out mechanisms of the gate oxide have not been determined. Physics based device modeling using numerical simulators can confirm physical models of device operation and provide insight into effects unknowable from the terminal characteristics. This information can in turn be fed to device designers and manufacturers to produce a better device. Scope of Effort This effort focuses on the physics-based modeling of wide band-gap (WBG) semiconductor electronics devices, in particular those made with silicon carbide (SiC), as well as their characterization. In general, the modeling work will be done at the University of Maryland (UMD) and the device characterization will be performed at ARL; but some modeling may be done at ARL under the guidance of Professor Goldsman, and some UMD students may perform device characterization at ARL under the guidance of ARL scientists. All WBG devices of joint interest may be characterized and modeled under this agreement. Specifically, this includes the characterization and modeling of 4H-SiC MOSFETs, both lateral test structures and power devices rated for 1,200 V and 5 A. Timeline / Deliverables The following schedule gives an estimate of the work undertaken by UMD and ARL during the course of this agreement: Year One (August 16, 2004 to August 15, 2005) 1. ARL will characterize, as a function of temperature and applied voltage, 4H-SiC lateral MOSFETs provided by Cree from SiC MOSFET fabrication runs under a separate cooperative agreement. This device characterization will include charge pumping, I-V, C-V, and conductance measurements. ARL and Cree will compare results, specifically mobility and interface trap density values, obtained from device characterization of these 4H SiC MOSFETs. In addition, ARL will perform preliminary reliability measurements on these devices, including threshold voltage stability measurements as a function of applied bias stress, time, and temperature. ARL will attempt to separate the effects due to interface trapped charge and to fixed charge in the SiC MOSFET oxide layer. ARL will provide device characterization results to UMD, including ID-VGS and ID-VDS data, extracted threshold voltage and channel mobility, and interface trap density as a function of band-gap energy. ARL will also provide device design information, including device geometry and material parameters such as doping density. 2. UMD will perform a study of low-field transport in the inversion layer channel of a 4H-SiC n-channel MOSFET. This work will emphasize the effects of quantum confinement at the SiC/SiO2 interface, whereby the two low-lying conduction bands are split into a number of subbands. Quantum effects will also be included in calculating the carrier concentrations, the scattering rates, and screening effects. The rates of scattering, due to charge trapped at interface traps and near-interfacial oxide traps, surface roughness, and acoustic phonons, will be developed for quasi-2D and will account for the screening of mobile charge carriers in the inversion layer and will be solved in a self-consistent manner. The dependence of inversion-layer carrier transport properties, such as mobility, will then be investigated as a function of both temperature and trapped charge (both at the interface and in the near-interfacial oxide region). The modeling results will be compared with data provided by ARL in Item # 1, and will then be incorporated into the 4H-SiC MOSFET device simulator at UMD. 3. UMD will begin a temperature-dependent study of high-field transport in the inversion layer channel of a 4H-SiC n-channel MOSFET using UMD’s full-band Monte-Carlo simulator. Scattering rates due to the following will be considered, including acoustic phonons, polar optical phonons, interface-trap charge, near-interfacial oxide trapped charge, and surface roughness. ARL will provide trapped charge information obtained in Item # 1, along with surface roughness information obtained from a separate ARL cooperative agreement with Cree. The output of this work, providing important information regarding the physical mechanisms affecting inversion-channel current flow and saturation will be incorporated into the 4H-SiC MOSFET device simulator at UMD. 4. UMD will begin the modeling of the 4H-SiC power DMOSFET, using the UMD 4HSiC MOSFET device simulator as a starting point. This work will require transforming the 2D MOSFET code, which is based largely on surface transport, to surface and bulk codes reflecting DMOSFET geometries. ARL will provide UMD with device design information, including device geometries, dimensions, and doping profiles, where available. 5. UMD will design Si test-structures that can be used as benchmarks for SiC chargepumping and C-V measurements performed at ARL under Item #1. The teststructures will consist mainly of various-sized MOSFETs and capacitors, and laid out using the Cadence tools set. The designs will be submitted to MOSIS for fabrication.