doc - Department of Electrical and Computer Engineering

advertisement

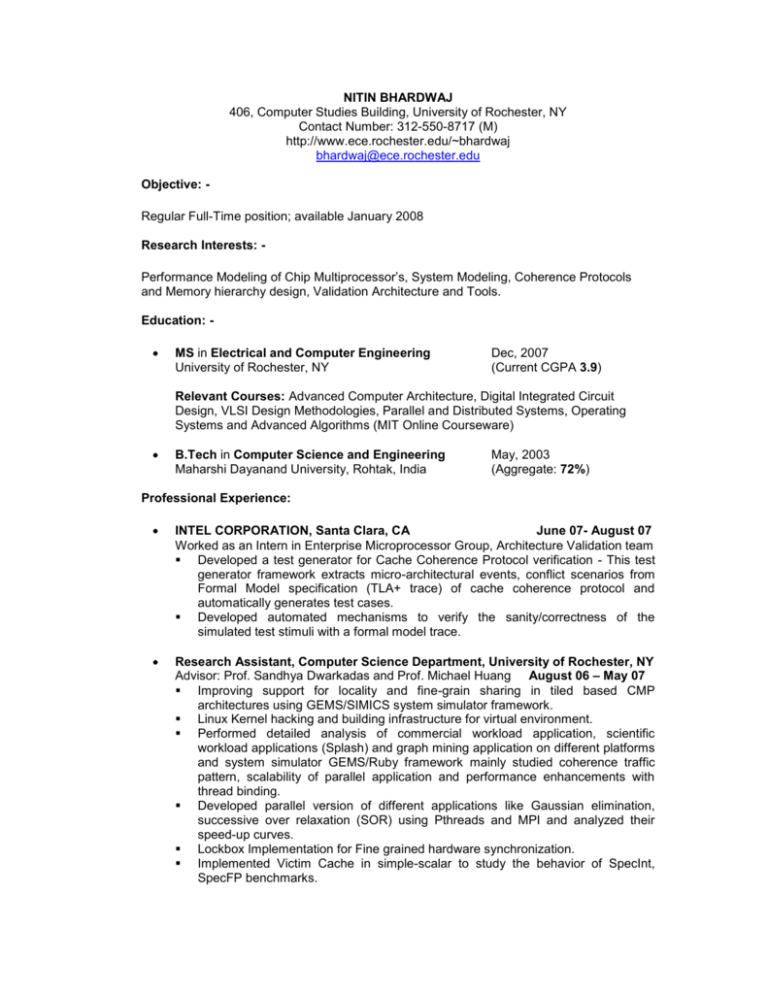

NITIN BHARDWAJ 406, Computer Studies Building, University of Rochester, NY Contact Number: 312-550-8717 (M) http://www.ece.rochester.edu/~bhardwaj bhardwaj@ece.rochester.edu Objective: Regular Full-Time position; available January 2008 Research Interests: Performance Modeling of Chip Multiprocessor’s, System Modeling, Coherence Protocols and Memory hierarchy design, Validation Architecture and Tools. Education: MS in Electrical and Computer Engineering University of Rochester, NY Dec, 2007 (Current CGPA 3.9) Relevant Courses: Advanced Computer Architecture, Digital Integrated Circuit Design, VLSI Design Methodologies, Parallel and Distributed Systems, Operating Systems and Advanced Algorithms (MIT Online Courseware) B.Tech in Computer Science and Engineering Maharshi Dayanand University, Rohtak, India May, 2003 (Aggregate: 72%) Professional Experience: INTEL CORPORATION, Santa Clara, CA June 07- August 07 Worked as an Intern in Enterprise Microprocessor Group, Architecture Validation team Developed a test generator for Cache Coherence Protocol verification - This test generator framework extracts micro-architectural events, conflict scenarios from Formal Model specification (TLA+ trace) of cache coherence protocol and automatically generates test cases. Developed automated mechanisms to verify the sanity/correctness of the simulated test stimuli with a formal model trace. Research Assistant, Computer Science Department, University of Rochester, NY Advisor: Prof. Sandhya Dwarkadas and Prof. Michael Huang August 06 – May 07 Improving support for locality and fine-grain sharing in tiled based CMP architectures using GEMS/SIMICS system simulator framework. Linux Kernel hacking and building infrastructure for virtual environment. Performed detailed analysis of commercial workload application, scientific workload applications (Splash) and graph mining application on different platforms and system simulator GEMS/Ruby framework mainly studied coherence traffic pattern, scalability of parallel application and performance enhancements with thread binding. Developed parallel version of different applications like Gaussian elimination, successive over relaxation (SOR) using Pthreads and MPI and analyzed their speed-up curves. Lockbox Implementation for Fine grained hardware synchronization. Implemented Victim Cache in simple-scalar to study the behavior of SpecInt, SpecFP benchmarks. Developed report on comparing different research proposals in the area of Cache Design: NUMA, NuRAPID, CMP-NuRAPID, Cache Design for CMT (Clustered Multithreaded), Cooperative Caching, Adaptive Selective Replication Coherence Protocol: Token Coherence, Coherence Ordering for Ring based CMP, Adaptive Protocol for Migratory Shared Data. Designed schematic and layout of 6-bit Dynamic Manchester Carry Chain Adder. INTEL CORPORATION, Bangalore, India March 2004 – July 2006 Member of Pre-Silicon unit, full-Chip and Post-Silicon system validation teams for Intel’s next generation pt-2-pt message based server product. Test plan development & execution to validate MP cache coherency, bus-cluster (logical bus connecting several on-chip processors), system configuration agent and cross product of non-coherent and coherent x-86 transactions Worked on DRIT (directed random instruction test) tool developing focused test cases to cover architectural and micro-architectural conditions. Developed libraries for interrupt handlers, generating split-line accesses, inserting delay loops, and grouping similar instructions together e.g. create a group of arithmetic, logical, fast-string, XMM etc instructions. Worked on enhancing IA32 assembly test to BFM (Behavioral Functional Model) test stream generator in Perl. Worked on driving design requirements for a SV (System Validation) test generator mainly looked at virtualization technology (VT-x) usage model validation, how to improve test tool coverage space and end result-checking strategies. Project Associate, Indian Institute of Technology, Delhi July 2003 – Feb 2004 Advisor: Prof. M. Balakrishnan and Prof. Anshul Kumar Exploring Cache Interface of LEON (SPARC arch) and interfacing local memory. Testing in-house developed FPGA Board for Virtex series of Xilinx FPGA. Assisted several under-graduate projects: MIPS Emulator, Case Study of ADMXRC FPGA Board and Floating Point Unit Integration with Leon. Skill set: Programming Languages: C, C++, IA32 Assembly, Perl, Python Hardware D Language: VHDL, VERILOG, I-HDL Simulators: System Level Simulator (SIMICS), C-SIM and IA simulator Post-Silicon debug tools: Intel H/W debug tools (ITP) VLSI Tools: Specman, Spice, Cadence Virtuoso- Layout Editor, Leonardo Spectrum, Synplify Pro, FPGA Express, Xilinx Implementation Tools, ModelSim SE 5.7c, Protel Honors: Member of Paper Review Committee of ISCAS’2007 Member of Paper Review Committee of HPCA’2008 Won Intel DRA (Department Recognition Awards) for Quality, Result Orientation and Customer Orientation several times. Citizenship Status: - F1 Student Visa -Nitin Bhardwaj