Appendix C – Example Core-Course Outcomes Worksheet (COW)

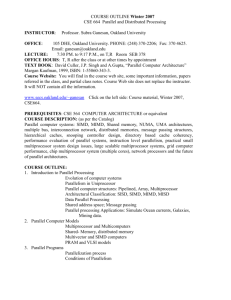

advertisement

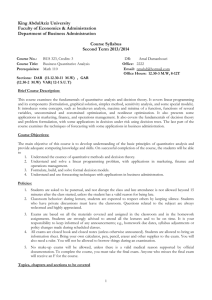

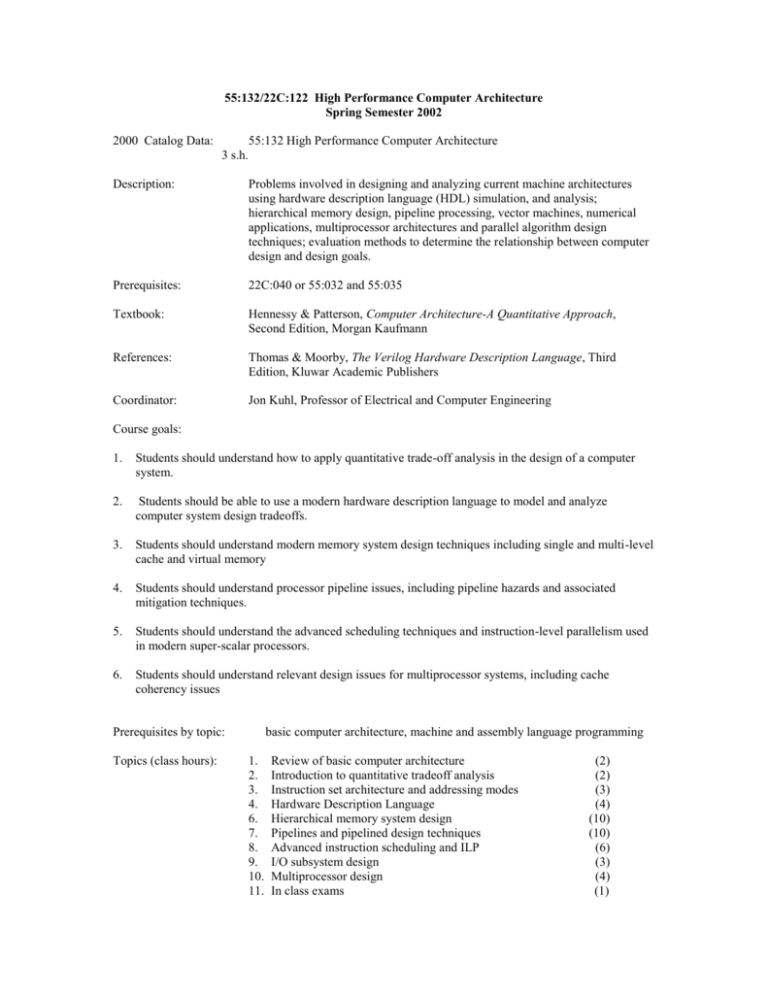

55:132/22C:122 High Performance Computer Architecture Spring Semester 2002 2000 Catalog Data: 55:132 High Performance Computer Architecture 3 s.h. Description: Problems involved in designing and analyzing current machine architectures using hardware description language (HDL) simulation, and analysis; hierarchical memory design, pipeline processing, vector machines, numerical applications, multiprocessor architectures and parallel algorithm design techniques; evaluation methods to determine the relationship between computer design and design goals. Prerequisites: 22C:040 or 55:032 and 55:035 Textbook: Hennessy & Patterson, Computer Architecture-A Quantitative Approach, Second Edition, Morgan Kaufmann References: Thomas & Moorby, The Verilog Hardware Description Language, Third Edition, Kluwar Academic Publishers Coordinator: Jon Kuhl, Professor of Electrical and Computer Engineering Course goals: 1. Students should understand how to apply quantitative trade-off analysis in the design of a computer system. 2. Students should be able to use a modern hardware description language to model and analyze computer system design tradeoffs. 3. Students should understand modern memory system design techniques including single and multi-level cache and virtual memory 4. Students should understand processor pipeline issues, including pipeline hazards and associated mitigation techniques. 5. Students should understand the advanced scheduling techniques and instruction-level parallelism used in modern super-scalar processors. 6. Students should understand relevant design issues for multiprocessor systems, including cache coherency issues Prerequisites by topic: Topics (class hours): basic computer architecture, machine and assembly language programming 1. 2. 3. 4. 6. 7. 8. 9. 10. 11. Review of basic computer architecture Introduction to quantitative tradeoff analysis Instruction set architecture and addressing modes Hardware Description Language Hierarchical memory system design Pipelines and pipelined design techniques Advanced instruction scheduling and ILP I/O subsystem design Multiprocessor design In class exams (2) (2) (3) (4) (10) (10) (6) (3) (4) (1) Total: (45) Computer Usage: 1. Hardware Description Language (Verilog) on CSS computers. Projects : 1. 2. Design and analysis of set associative cache memory system using Verilog Design and optimization of a pipelined processor using Verilog (small group project) ABET category content as estimated by faculty member who prepared this course description: Engineering science: 1.5 credits or __ percent Engineering design: 1.5 credits or __ percent Prepared by: Jon Kuhl Date: April 1, 2002 Course Outcomes Worksheet (COW) 55:132/22C:122 High Performance Computer Architecture Spring 2001-02 Course Goals Supports ABET Outcomes 1. Students should understand how to apply quantitative trade-off analysis in the design of a computer system a(●), c(●), e(●), j(●), k(●) 2. Students should be able to use a modern hardware description language to model and analyze computer system design tradeoffs. b(●), c(●), d(●), e(●), g(○), j(●), k(●) 3. Students should understand modern memory system design techniques including single and multi-level cache and virtual memory. a(●), c(●), e(●), j(●), k(●) 4. Students should understand processor pipeline issues, including pipeline hazards and associated mitigation techniques. a(●), c(●), e(●), j(●), k(●) 5. Students should understand the advanced scheduling techniques in modern super-scalar processors. c(●), e(●), i(●), j(●) 6. Students should understand relevant design issues for multiprocessor systems, including cache coherency issues. c(●), e(●), i(●), j(●) Course Activity Homework assignments and project assignments require students to apply quantitative design trade-off analyses with respect to memory system and processor design. Exams test student mastery of quantitative analysis methods Students do two significant projects that require them to model and analyze the performance of portions of a computer system architecture using the VERILOG hardware description language. At least one of these projects requires students to work in small groups, shcih often mix ECE and CS students. Students do homework assignments and projects that require them to analyze memory system design tradeoffs. Exams test mastery of quantitative techniques fo performing tradeoff analyses Students do homework assignments and projects that require them to analyze pipeline design issues. Exams test mastery of quantitative techniques for performing tradeoff analyses Case studies of modern processor architectures are presented. Exams test student mastery of concepts used in modern processors. Exams test student understanding of important issues in contemporary multiprocessor design ○ denotes moderate contribution to the outcome ● denotes substantial contribution to the outcome ASSOCIATED EASY SURVEY QUESTIONS Question No. 1 2 Course Goal 1 2 3 4 5 3 4 5 6 6 EASY Assessment Statement (soliciting 1-6 disagree-agree response, plus comm I understand how to carry out a quantitative tradeoff analysis to evaluate computer sy I am able to use a modern hardware description language to model and analyze aspec architecture. I understand design issues related to memory systems, including cache memory and v I understand pipeline design issues, including hazards and associated mitigation techn I am familiar with instruction scheduling and instruction-level parallelism techniques scalar processors I understand relevant design issues for multiprocessor systems ABET Outcomes a) – k) (Used for core-course assessments) Engineering graduates will have the following attributes: (a) an ability to apply knowledge of mathematics, science, and engineering; (b) an ability to design and conduct experiments as well as to analyze and interpret data; (c) an ability to design a system, component, or process to meet desired needs; (d) an ability to function on multidisciplinary teams; (e) an ability to identify, formulate, and solve engineering problems; (f) an understanding of professional and ethical responsibility; (g) an ability to communicate effectively in oral (o), written (w), and graphical (g) forms; (h) the broad education necessary to understand the impact of engineering solutions in a global and societal context; (i) a recognition of the need for and an ability to engage in lifelong learning; (j) a knowledge of contemporary issues; (k) an ability to use the techniques, skills, and modern engineering tools necessary for successful engineering practice;