FS1.0 - University of Portland

advertisement

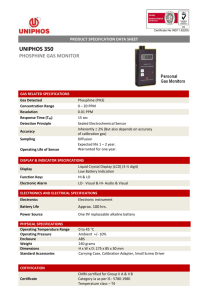

University of Portland School of Engineering 5000 N. Willamette Blvd. Portland, OR 97203-5798 Phone 503 943 7314 Fax 503 943 7316 Functional Specifications Project Pit Roach: A B2Logic to L-Edit Translator Contributors: Zachary Heath Daman Oberoi John Chezem Approvals Name Dr. Osterberg Date Name Date Dr. Lillevik Insert checkmark (√) next to name when approved. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH REV. 1.0 PAGE II Revision History Rev. 0.9 1.0 Date 09/22/03 10/29/03 UNIVERSITY OF PORTLAND Author Team Pit Roach Team Pit Roach Reason for Changes Initial draft Suggested during approval meeting SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH REV. 1.0 PAGE III Table of Contents Summary.…………………………………………………………………………………1 Introduction.……………………………………………………………………………...2 Background………………………………………………………………………………3 Requirements…………………………………………………………………………….4 Overview.…………………………………………………………………………………………………4 Software Specifications………………………………………………………………………………….4 Input Specifications………………………………………………………………………………………5 Output Specifications…………………………………………………………………………………….5 Bonus Feature Specifications…………………………………………………………………………...5 Conclusions………………………………………………………………………………6 UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH REV. 1.0 PAGE IV List of Figures Figure 1. B2Logic Sample Circuit ...................................................................................................................3 Figure 2. Block Diagram of Pit Roach Project ……………………………………………………………….4 UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH REV. 1.0 PAGE V List of Tables Table 1. Software Specifications …………………………………………………………………………….4 Table 2. Input Specifications ………………………………………………………………………………...5 Table 3. Output Specifications .……………………………………………………………………………...5 Table 4. Bonus Feature Specifications ...…………………………………………………………………...5 UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH Chapter REV. 1.0 PAGE 1 Summary 1 Our product, B2Logic to L-Edit Translator (BLT), will fill a current void at the University of Portland by significantly increasing the speed and ease of the integrated circuit (IC) layout process. The program will take the names of the B2Logic netlist and the desired output file as inputs. BLT will parse the B2Logic netlist and format the output file accordingly. This newly created .tpr file can then be used as input to the L-Edit Auto Place and Route function to automatically create the IC layout. BLT will eliminate the need for hand-writing .tpr files, which is an error-prone and tedious process. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH Chapter REV. 1.0 PAGE 2 Introduction 2 This document is the user’s perspective of the B2Logic L-Edit Translator (BLT). This functional specification was written for the developers, advisors, and industry representative involved in this project. The developers will use this document to start preparing designs. The advisors and industry representative will use this to get a better understanding of what will be accomplished by the BLT project. This document will describe the functional behavior of BLT from the user’s perspective. It will not include any source code, details on how to operate the program, nor an explanation of how the program performs the translation. This document will simply provide a general overview of what the product will do once it is completed. The remainder of this document includes a brief background on both B2Logic and L-Edit. This section serves as an explanation for the motive behind the creation of BLT. Next, the requirements of the project are listed, and a block diagram is included for clarification. The document ends with a conclusion restating the purpose and final product expected from this project. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH Chapter REV. 1.0 PAGE 3 Background 3 Project BLT is a translating program that will take the netlist (a .EDF file) from B2Logic and convert it to a Tanner .tpr file. This will enable students creating a VLSI chip to go directly from a high-level circuit schematic to the VLSI chip design layout with little work in between. Currently, University of Portland students designing VLSI chips have to hand-write the Tanner .tpr file after extensively testing their circuits in B2Logic. It is extremely easy to make a simple mistake during this process due to the length, complexity, and accuracy required in the .tpr file for Tanner’s Auto Place and Route function. Although Tanner’s full suite includes a B2Logic to L-EDIT translator, the University of Portland has elected to postpone purchase of this program due to its expense. B2Logic is a high-level circuit schematic tool that allows the user to ‘drag and drop’ logic gates to form complex digital circuits. The figure below shows a screenshot of a sample circuit in B2Logic. Figure 1. B2Logic Sample Circuit B2Logic outputs a netlist file that is unique to each circuit design. This will allow easy identification and parsing of the specific parts and connections used in each design. The netlist will then be run through BLT, and a Tanner .tpr file will be produced. L-Edit is a software program that allows a user to lay out an integrated circuit in silicon. This process can be done by hand, but is more commonly accomplished by the Auto Place and Route function. This feature requires a properly formatted .tpr file as input. A .tpr file is the text equivalent of a complete VLSI Layout. The completion of BLT will have two primary benefits: 1) It will fill the current void between B2Logic and L-Edit for students at the University of Portland and make chip design a much simpler process. 2) It will give the University of Portland a valuable piece of software for very little cost. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATIONS PROJECT PIT ROACH Chapter REV. 1.0 PAGE 4 Requirements 4 Overview Project BLT is a translating program that will take the netlist (a .EDF file) from B2Logic and convert it to a Tanner .tpr file. This will enable students creating a VLSI chip to go directly from a high-level circuit schematic directly to the VLSI chip design layout with little or no work in between. The user will have to export the netlist file from B2Logic to a .EDF file. Then BLT will need to be opened, and the names of the netlist file and the desired .tpr file will have to be given as input. After running the program, a .tpr file will be produced, which will then need to be given as input to L-EDIT’s Auto Place and Route feature. Figure 2. Block Diagram of BLT Product Software Specifications System Software Table 1. Software Specifications contains a list of the system software versions to be used. Table 1. Software Specifications UNIVERSITY OF PORTLAND Requirement Value B2Logic Version BLT.LIB (B2Logic Library) Perl Windows L-Edit Unix L-Edit 3.0.15a N/A 5.x 8.41 6.02 SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATION PROJECT PIT ROACH REV. 1.0 PAGE 5 Input Specifications Inputs Table 2. Input Specifications contains a list of the inputs required by BLT. Table 2. Input Specifications Requirement B2Logic Netlist Name Output File Name Output Specifications Outputs Table 3. Output Specifications contains a list of the outputs from BLT. Table 3. Input Specifications Requirement .tpr File Bonus Feature Specifications Bonus Features Table 4. Bonus Feature Specifications contains a list of features that will be implemented only if time allows. Table 4. Bonus Feature Specifications Requirement Unix Command Line Executable Graphical User Interface Expanded Library (BLT.LIB) Integrated One-Step Process Ability to Handle L-Edit Macros UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH FUNCTIONAL SPECIFICATION PROJECT PIT ROACH Chapter REV. 1.0 PAGE 6 Conclusions 5 BLT will greatly simplify the process of chip design using the current technology at the University of Portland. Presently, students can design and simulate digital circuits in B2Logic. L-Edit allows students to design chip layouts via the Auto Place and Route function. However, there is a gap between designing the circuit in B2Logic and creating the chip layout in L-Edit. BLT will resolve this issue, enabling students to represent their designs in a high-level circuit diagram and translate the schematic directly to a chip layout. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: ZACH HEATH