Strothmann_Tom_2

advertisement

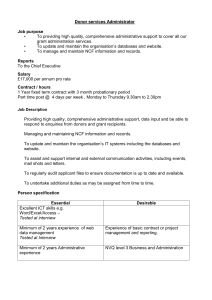

Methods for Assembly of TSV Products Tom Strothmann Kulicke & Soffa Industries 1005 Virginia Drive Fort Washington, PA, USA tstrothmann@kns.com BACKGROUND Via-middle TSV processes are enabling high volume production of applications using stacked die. The applications range from the memory stacks in production today to future mobile applications where memory will be stacked on application processors to reduce power and improve performance. Stacked die memory packages offer significantly better performance with reduced power due to the shorter routing length and lower line loss in the design. [1] Thermocompression bonding is the only viable choice for assembly of these 3D products to ensure repeatable bond line thickness and consistent metallurgy in the bump structure; however, there are significant challenges in the implementation of this technology due to several factors. This paper reviews the options for stacked TSV die assembly using Thermo-compression Bonding (TCB) and the approaches used for cost reduction. ASSEMBLY CHALLENGES FOR THIN SILICON WITH TSV The first challenge is the thin silicon itself with TSV structures and a thickness of 50 microns or less. The die is fragile and typically warped due to the residual stress of the dielectrics, RDL and UBM. This is warpage is inherent in the Mid-End of Line (MEOL) process flow that is used to reveal the TSV structures. The MEOL process flow is shown in Table 1. FEOL Fab Process MEOL BEOL Cu Pillar Via Etch Isolation Metal Fill Pad/RDL DRIE (via middle) Dielectric & Seed Dep Cu Plate & CMP Dielectric & Metal Pad Temp Bond Front-side bumping Bond to Carrier Dicing TC Bonding Figure 2: Representative Die Bowing (not to scale) 40m A 50um thick 9x9mm die with TSV’s can bow by as much as 40m Figure 1: MEOL Process Flow Front-End temporary adhesive to protect the Cu pillars, and the wafer is thinned to thickness that is typically targeted at 50m. This process reveals the filled vias that were created at the start of the fabrication process. Following via reveal, PECVD dielectrics, Under Bump Metal (UBM) and optional redistribution layers are applied to the backside of the wafer while it is still held by the temporary carrier. Once the backside processes are complete, the thinned wafer is directly transferred to dicing tape and the temporary carrier is removed. In many cases stealth dicing is used for dicing the very thin die. The thinned wafers on the dicing tape film frame are typically presented to the TCB process with the Cu pillars face up, although it is possible to use a tape and reel feed for the system if needed. As the silicon is thinned to 50 microns during the via reveal process and the backside dielectrics and UBM are applied, the imbalanced stress from the dielectrics and metals on the front of the wafer as compared to the newly formed dielectrics and patterning on the back of the wafer will cause warpage of the thinned silicon wafer.[2] After dicing this stress remains, causing bowing of the die that can be as much as 40 microns in a die size that is 9x9mm. Representative die bow is shown in Figure 2. Via Reveal & UBM Grind, CMP, Passivate & UBM Debond De-bond from Carrier Final Assembly (assembly) The MEOL process flow creates partial vias in the silicon wafer during the fabrication process. [1] The vias are typically formed to a depth of 60-75um and filled with Cu. The full thickness wafer is provided to the MEOL process to form Cu pillar bumps on the active side of the die. The wafer is then bonded to a temporary carrier using a thick A well-controlled stacked die process will have consistent Bond Line Thickness (BLT) and Solder Line Thickness (SLT) as is shown in Figure 3. The BLT and the SLT must be carefully controlled to provide the consistent metallurgy at each of the joints that is required for a reliable interconnect. If the bondline thickness is too high, the solder in the joints can neck and reduce the cross-sectional area of the joint, potentially affecting reliability. If the bondline thickness is too low Cu pillar bumps at fine pitch can be shorted together by solder squeeze-out. The consistency of the BLT is also important if Capillary Underfill is to be used after the bonding process. Consistent bond line thickness enables better control of that downstream process. To achieve the desired BLT and SLT, the die must be held flat during the TC bonding local reflow process. TC Bonders are able to achieve this by vacuum clamping the warped die onto a flat heated bond head surface throughout the bonding cycle with a structure represented by Figure 4. Figure 3: TSV Stacked Die Demonstrating BLT and SLT SLT BLT Figure 4: TC Bondhead with Flat Die TC Bond Head 50um thick die with TSV’s TCB stacked die processes using capillary underfill have a small process window based in the characteristic warpage seen in the thin die. A single die can be bonded “flat” by using the vacuum clamping of the bondhead, and the process can be optimized for time, temperature and throughput requirements. The next die in the stack does not have the same latitude for adjustment. Heat will rapidly be conducted through the thin silicon and Cu pillars of the die being bonded into the die below. During the reflow of the Cu pillars onto the UBM, it is possible to remelt the lower die. If the lower die remelts, it is no longer held flat and it can begin to relax toward its original warped shape. Since the top die is still held flat, this can create unexpected variation in the bondline thickness of the new die and inconsistent bondline thickness throughout the stack. There is no easy way to avert this variation with the TCB process. One option is to allow some variation and curvature in the bonded die. Once the die is bonded it will not fully revert to the warpage seen in the bare die state. If warpage due to stress is consistent throughout a wafer, a consistent bondline thickness with slight curvature can be tolerated. The special requirement for this process option comes with the top die. In order to maintain a consistent BLT the vacuum must be released while the solder is molten. This vacuum release at high temperature allows the top die to conform to the lower die in the stack. If a TC CUF process is desired for stacked die production, particular care should be given to balancing stress created in the backside via reveal and passivation processes to ensure the die bow is minimized. The amount of bow in the final assembly with a TC CUF process will vary based on upstream process variation. Two types of stacked memory products are currently assembled using TCB. High Bandwidth Memory (HBM) products are assembled using interposers to enable very high-density routing to the HBM stack. This product uses chip-to-wafer (C2W) TC bonders. Hybrid Memory Cube (HMC) modules used in high-performance computing can be assembled on laminate with chip-to-substrate (C2S) TC bonders. HBM and HMC currently drive the highest demand for stacked die TCB. THE CHALLENGE FOR UNDERFILLS The second challenge in stacked die assembly is with the underfill used for the assembly. TC bonding followed by capillary underfill is an established technology, but there is process variation in bondline thickness as previously discussed. Capillary underfill of single die is a very mature technology, but capillary underfill of a die stack becomes increasingly difficult as the number of die in the stack increases. Effective, void free capillary underfill techniques and materials used for single die may be adequate for short die stacks, but they are unlikely to enable stacks of 8, 16 or 32 die. The use of wafer applied underfill makes the TCB process more capable but it adds expense and requires a material set that is still being optimized. Process options for underfill use in TCB process are shown in the Table 1. [3] Throughput numbers shown are for a dual head system placing a single die. Stacked die throughput numbers will be lower. Table 1: Options for Underfill Process Paste Underfill NCP Film Underfill NCF Dip Flux Capillary Underfill Substrate Flux Capillary Underfill Advantages Die is underfilled during TCB Mature process Future 1500 UPH Suitable for die stacking Die is underfilled during TCB Less chance for tool contamination than paste Future 2000 UPH Suitable for die stacking No chance of tool contamination Very short bonding process times Low forces for high bump counts Future 1500 UPH Very fast – very small bond head temp changes per cycle Future 3000 UPH Disadvantages Unsuitable for die stacking Potential tool contamination Void-free underfill requires dwell Longer bond times to ensure curing Void-free underfill requires dwell Large temperature changes required Films still in development Cooling to <80C at fluxing station Requires flux cleaning Requires post-bond CUF More stress on bonds before CUF Cooling to <100C at fluxing station Unsuitable for die stacking Requires flux cleaning Requires post-bond CUF More stress on bonds before CUF Fluxing processes still in development Non–Conductive Paste (NCP) is commonly used as an underfill for many TCB processes and is a well-established technology. The logistics required to dispense a new layer of NCP on the top of each bonded die would limit machine throughput and substantially add to the cost of the process. In addition to this limitation, NCP applied to a very thin die has a tendency to squeeze out and potentially contaminate the bond head. For these reasons, NCP is not used for stacked die applications. Non-Conductive Film (NCF), also known as wafer applied underfill, is vacuum laminated to the die surface prior to dicing. Since the film is applied in wafer form, it is highly suitable for use in stacked die processes. NCF is used in volume production today although the development of new NCF materials continues. Development of new films is challenging because of the diverse requirements placed on them. The film must be stable during the die pick operation, become nearly liquid without curing during the temperature ramp, and cure very quickly at a temperature below the melting point of the solder. It should also contain a high percentage of filler particles to reduce the expansion coefficient, yet still have some transparency to ensure alignment marks are not obscured. A fluxing agent must be included in the NCF that is aggressive enough to remove oxides on the solder and Cu surfaces, yet mild enough to avoid subsequent metal corrosion. These formulation issues have mostly been solved by the suppliers, but the other problem with NCF materials in the past has been limited throughput due to wide temperature excursions required by the bondhead when handling die coated with the film. The NCF film has historically been limited to a die transfer temperature of no more than 80oC to avoid issues associated with the film becoming tacky and susceptible to handling damage. New handling techniques have been developed to resolve this issue and NCF can now be transferred at temperatures up to 150 oC. With this improvement, NCF is poised to become one of the highest throughput options available for TCB processes. NCF also has the significant benefit of locking the bondline thickness during the TC bonding process. This means a “flat die” process can be used and the TC bonding process can be optimized for BLT and SLT independent of the position in the die stack and the potential to remelt the lower die. This NCF capability enables a much wider process window with better process capability. Accurate control of force before and during the bonding process is critical as is the capability to switch the recipe between force and position mode during the process. Force control is important for bonding using NCF underfill because depending on die size and pillar count, forces approaching 300N may be required for some layers during the bonding process. TC NCF processes are in use for production today. Substrate flux with capillary underfill can provide a very effective high throughput solution for bonded die on laminate. It avoids the process of dipping each die into flux prior to bonding and the temperature excursions to cool the bond prior to flux dipping are not required. It is however not possible to pre-flux stacked die so it is not an option for a stacked die process. Substrate flux processes also require the use of capillary underfill. Thermocompression processes with capillary underfill (TC CUF) are a viable choice for stacked die production and these techniques are in use today. Throughput is limited because the flux dip, die transport, alignment and seek, must all be done below about 100oC to avoid evaporation of the flux and premature flux activation. This results in a wider range of temperature during the cycle. The process window for a capable TC CUF process is smaller and capillary underfill of taller die stacks is more difficult, but the underfill material set is well-know and the process is used in high volume production. PROCESS COST FOR STACKED DIE PROCESSES The final challenge for stacked die processes is the overall cost of the process as compared to alternative assembly options. The benefits of the technology are well known with respect to reduced power and improved performance, but there are limits to market acceptance if the price is too high. Optimizing the TCB process to achieve high throughput with a well controlled and high yielding process is critical to reduce cost. The cost of TCB must be competitive with alternative assembly technologies and this can only be achieved if the throughput and yield of the process is high. Throughput of the TCB stacked die process is the single most important factor related to cost. [3] Higher throughput provides a lower cost per unit and defers the capital cost of the equipment. Reviewing the throughput numbers for the available TCB processes shown in Table 1 reveal a planned UPH of 2000 for the TC NCF process and 1500 for the TC CUF process on a dual head TCB system. The NCF process has advantages in that it supports a more capable process for the thin stacked die while achieving higher speed. Additional improvements are potentially possible with NCF through the use of a collective bonding process, wherein the die are initially tacked in place and the TC bond and NCF cure is done as the final die is bonded. Figure 5 shows the concept of collective bonding. In a die by die process, each die is fully bonded and the NCF is cured. In a collective bonding process each middle die is just tacked in place and the final bond and NCF cure is not done until the top die is placed. Figure 5: NCF Collective Bonding Process Die By Die TCB Process Memory Die Base Die Collective Bonding TCB Process Collective Die Tack Die Base Die Figure 6: Scope Trace of Collective Bonding Z axis drop about 50um Figure 6 shows the machine scope trace for the top die on a collective bonding stack, with the Z-axis stepping down as each lower layer melts. A collective bonding process has the potential to increase throughput by 25% and further lower the cost of an NCF process. Yield is critical in achieving a cost effective process for stacked die. The loss of a single die in an assembled stack scraps all the die in that stack. Accordingly the process must have excellent process control and capability. The thickness of the die with through-silicon vias (TSVs) can be 50µm or less, so equipment must be designed to handle and bond thin die without inducing mechanical damage. Yield can be ensured by implementing an inspection of the die after pick and prior to placement. Die cracks or chip outs detected before placement prevent unnecessary yield loss and provide an early alert for potential mechanical issues in the process. Current TCB equipment has also implemented exceptional process control methods to ensure any process deviation is detected quickly and product risk is controlled. Communication with upstream and downstream processes ensures effective integration of the TC bonding process to the overall process flow. Data integration, wherein the equipment uses full data logging capability and traceability for all die back to the silicon source wafer is critical for yield enhancement activities. Recent advances in TCB equipment offer solutions for each of these factors for both chip-to-substrate (C2S) and chip-to-wafer (C2W) bonders. The cost of die stacking is difficult to compare with other technologies since it enables a level of performance through 3D assembly that is not otherwise possible with conventional assembly techniques. The more fundamental question is has the technology reached a price point that gains market acceptance for the improved performance? The answer to this question would appear to be yes, based on recent product announcements. AMD and Nvidia have announced the use of HBM in their next-generation graphics modules. Intel recently announced that its Xenon Phi processor “Knights Landing” will use the Micron HMC stacked DRAM. These products entered production before the recent advances in NCF processes. Enabling the additional cost reduction possible with high speed NCF processes will further lower the cost and expand the market penetration of stacked die assembled with TCB. CONCLUSIONS Two methods for TCB assembly of stacked die have been reviewed and both are in volume production today. The TC CUF process is a viable option, but the assembly is subject to upstream process variation that drives variation in die bowing. The use of capillary underfill also becomes more challenging as die stack height increases. NCF processes are inherently more stable and suitable for die stacking since they enable a “flat die” process; however there is substantial variation in the formulation between NCF suppliers. The NCF must be carefully evaluated to ensure the desired reliability performance is achieved. Over time, NCF is expected to become the default material set for die stacking. High-volume use of thermocompression bonding (TCB) in semiconductor assembly processes has started and known benefits of the technology, such as reduced form factor and higher speed with reduced power are being realized. The production use of stacked die TC Bonding has increased now that the process is ramping for the production of stacked memory products. Both the hybrid memory cube (HMC) and high-bandwidth memory (HBM) are using TCB in the assembly process. Thermocompression assembly enables this next-generation of fine-pitch, 2.5D and 3D assembly technologies. Memory products are driving the commercial volume in the technology, using TSV technology and thin die stacks ranging from 4 to 16 layers in height. Thin die, BLT/SLT control, underfill development and throughput are important factors supporting the continued high volume adoption of TCB. Advanced TC bonding equipment and new advanced materials are an integral part of the solutions that have enabled commercially viable 3D technologies. REFERENCES 1. Duk Ju Na, et al., “TSV MEOL (Mid End of Line) and Packaging Technology of Mobile 3D-IC Stacking”, 64th Electronic Components & Technology Conference, 2014 2. DoHyeong Kim, et al., “Optimization and Challenges on TSV MEOL Integration”, 64th Electronic Components & Technology Conference, 2014 3. Horst Clauberg, et al., “High Productivity Thermocompression Flip Chip Bonding”, 65th Electronic Components & Technology Conference, 2015