SPIMQuickRef - Sierra Nevada College

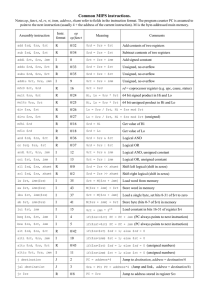

advertisement

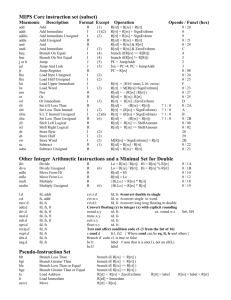

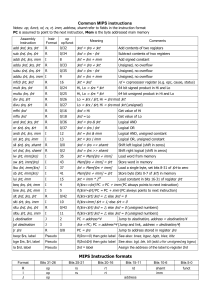

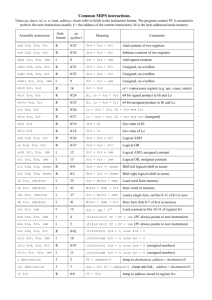

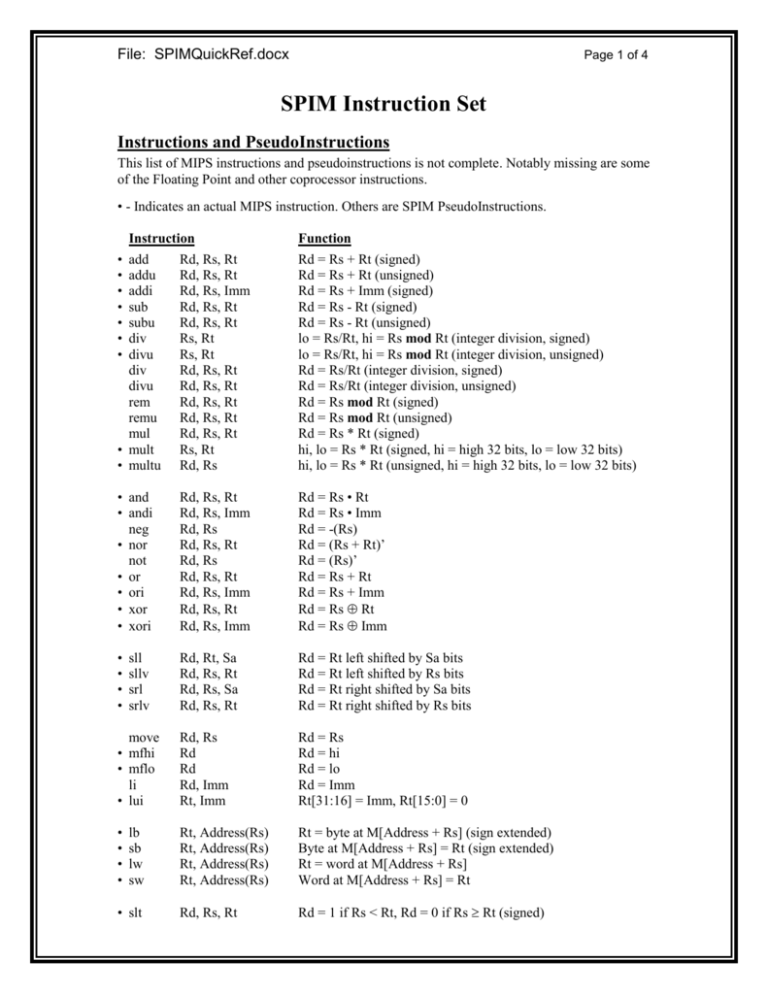

File: SPIMQuickRef.docx Page 1 of 4 SPIM Instruction Set Instructions and PseudoInstructions This list of MIPS instructions and pseudoinstructions is not complete. Notably missing are some of the Floating Point and other coprocessor instructions. • - Indicates an actual MIPS instruction. Others are SPIM PseudoInstructions. • • • • • • • • • Instruction add Rd, Rs, Rt addu Rd, Rs, Rt addi Rd, Rs, Imm sub Rd, Rs, Rt subu Rd, Rs, Rt div Rs, Rt divu Rs, Rt div Rd, Rs, Rt divu Rd, Rs, Rt rem Rd, Rs, Rt remu Rd, Rs, Rt mul Rd, Rs, Rt mult Rs, Rt multu Rd, Rs Function Rd = Rs + Rt (signed) Rd = Rs + Rt (unsigned) Rd = Rs + Imm (signed) Rd = Rs - Rt (signed) Rd = Rs - Rt (unsigned) lo = Rs/Rt, hi = Rs mod Rt (integer division, signed) lo = Rs/Rt, hi = Rs mod Rt (integer division, unsigned) Rd = Rs/Rt (integer division, signed) Rd = Rs/Rt (integer division, unsigned) Rd = Rs mod Rt (signed) Rd = Rs mod Rt (unsigned) Rd = Rs * Rt (signed) hi, lo = Rs * Rt (signed, hi = high 32 bits, lo = low 32 bits) hi, lo = Rs * Rt (unsigned, hi = high 32 bits, lo = low 32 bits) • and • andi neg • nor not • or • ori • xor • xori Rd, Rs, Rt Rd, Rs, Imm Rd, Rs Rd, Rs, Rt Rd, Rs Rd, Rs, Rt Rd, Rs, Imm Rd, Rs, Rt Rd, Rs, Imm Rd = Rs • Rt Rd = Rs • Imm Rd = -(Rs) Rd = (Rs + Rt)’ Rd = (Rs)’ Rd = Rs + Rt Rd = Rs + Imm Rd = Rs Rt Rd = Rs Imm • • • • Rd, Rt, Sa Rd, Rs, Rt Rd, Rs, Sa Rd, Rs, Rt Rd = Rt left shifted by Sa bits Rd = Rt left shifted by Rs bits Rd = Rt right shifted by Sa bits Rd = Rt right shifted by Rs bits move • mfhi • mflo li • lui Rd, Rs Rd Rd Rd, Imm Rt, Imm Rd = Rs Rd = hi Rd = lo Rd = Imm Rt[31:16] = Imm, Rt[15:0] = 0 • • • • Rt, Address(Rs) Rt, Address(Rs) Rt, Address(Rs) Rt, Address(Rs) Rt = byte at M[Address + Rs] (sign extended) Byte at M[Address + Rs] = Rt (sign extended) Rt = word at M[Address + Rs] Word at M[Address + Rs] = Rt Rd, Rs, Rt Rd = 1 if Rs < Rt, Rd = 0 if Rs Rt (signed) sll sllv srl srlv lb sb lw sw • slt File: SPIMQuickRef.docx Page 2 of 4 • slti • sltu Rd, Rs, Imm Rd, Rs, Rt Rd = 1 if Rs < Imm, Rd = 0 if Rs Imm (signed) Rd = 1 if Rs < Rt, Rd = 0 if Rs Rt (unsigned) • beq beqz bge • bgez • bgezal bgt bgtu • bgtz ble bleu • blez • bgezal • bltzal blt bltu • bltz • bne bnez Rs, Rt, Label Rs, Label Rs, Rt, Label Rs, Label Rs, Label Rs, Rt, Label Rs, Rt, Label Rs, Label Rs, Rt, Label Rs, Rt, Label Rs, Label Rs, Label Rs, Label Rs, Rt, Label Rs, Rt, Label Rs, Label Rs, Rt, Label Rs, Label Branch to Label if Rs = Rt Branch to Label if Rs = 0 Branch to Label if Rs Rt (signed) Branch to Label if Rs 0 (signed) Branch to Label and Link if Rs Rt (signed) Branch to Label if Rs > Rt (signed) Branch to Label if Rs > Rt (unsigned) Branch to Label if Rs > 0 (signed) Branch to Label if Rs Rt (signed) Branch to Label if Rs Rt (unsigned) Branch to Label if Rs 0 (signed) Branch to Label and Link if Rs 0 (signed) Branch to Label and Link if Rs < 0 (signed) Branch to Label if Rs < Rt (signed) Branch to Label if Rs < Rt (unsigned) Branch to Label if Rs < 0 (signed) Branch to Label if Rs Rt Branch to Label if Rs 0 • • • • Label Label Rs Label Jump to Label unconditionally Jump to Label and link unconditionally Jump to location in Rs unconditionally Jump to location in Rs and link unconditionally j jal jr jalr System I/O Services: syscall Service Code in $v0 Print Integer 1 Print Float 2 Print Double 3 Print String 4 Read Integer 5 Read Float 6 Read Double 7 Read String 8 Sbrk Exit 9 10 Argument(s) $a0 = number to be printed $f12 = number to be printed $f12 = number to be printed $a0 = address of string in memory Result(s) number returned in $v0 number returned in $f0 number returned in $f0 $a0 = address of input buffer in memory $a1 = length of buffer (n) $a0 = amount address in $v0 File: SPIMQuickRef.docx Page 3 of 4 Registers By convention, many MIPS registers have special purpose uses. To help clarify this, SPIM defines aliases for each register that represent its purpose. The following table lists these aliases and the commonly accepted uses for the registers. Register zero at v0 v1 a0 a1 a2 a3 t0 t1 t2 t3 t4 t5 t6 t7 s0 s1 s2 s3 s4 s5 s6 s7 t8 t9 k0 k1 gp sp fp ra Decimal 0 1 2 3 4 5 6 7 Number 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 Hex 0 1 2 3 4 5 6 7 Usage Constant 0 Reserved for the assembler Used for return values from function calls. Used to pass arguments to procedures and functions. Temporary (Caller-saved, need not be saved by called procedure) Saved temporary (Callee-saved, called procedure must save and restore) Temporary (Caller-saved, need not be saved by called procedure) Reserved for OS kernel Pointer to global area Stack pointer Frame pointer Return address for function calls. Octal 0 1 2 3 4 5 6 7 Binary 0000 0001 0010 0011 0100 0101 0110 0111 Decimal 8 9 10 11 12 13 14 15 Hex 8 9 A B C D E F Octal 10 11 12 13 14 15 16 17 Binary 1000 1001 1010 1011 1100 1101 1110 1111 File: SPIMQuickRef.docx Page 4 of 4 Floating Point Instructions and PseudoInstructions The MIPS floating point coprocessor is coprocessor number 1. It operates on single precision (32-bit) and double precision (64-bit) floating point numbers. This coprocessor has its own registers, numbered $f0-$f31. Even numbered registers are used for double precision operations. • - Indicates an actual MIPS instruction. Others are SPIM pseudo instructions. Instruction • abs.d FRdest, FRsrc • abs.s FRdest, FRsrc Function FRdest = | FRsrc | FRdest = | FRsrc | • add.d • add.s FRdest, FRsrc1, FRsrc2 FRdest, FRsrc1, FRsrc2 FRdest = FRsrc1 + FRsrc2 FRdest = FRsrc1 + FRsrc2 • c.eq.d • c.eq.s FRsrc1, FRsrc2 FRsrc1, FRsrc2 Set flag on FRsrc1 = FRsrc2 Set flag on FRsrc1 = FRsrc2 • c.le.d • c.le.s FRsrc1, FRsrc2 FRsrc1, FRsrc2 Set flag on FRsrc1 FRsrc2 Set flag on FRsrc1 FRsrc2 • c.lt.d • c.lt.s FRsrc1, FRsrc2 FRsrc1, FRsrc2 Set flag on FRsrc1 < FRsrc2 Set flag on FRsrc1 < FRsrc2 • cvt.d.s FRdest, FRsrc • cvt.d.w FRdest, FRsrc Double ← Single Double ← Integer • cvt.s.d FRdest, FRsrc • cvt.s.w FRdest, FRsrc Single ← Double Single ← Integer • cvt.w.d FRdest, FRsrc • cvt.w.s FRdest, FRsrc Integer ← Double Integer ← Single • div.d • div.s FRdest, FRsrc1, FRsrc2 FRdest, FRsrc1, FRsrc2 FRdest = FRsrc1 / FRsrc2 FRdest = FRsrc1 / FRsrc2 FRdest, address FRdest, address FRdest = address FRdest = address • mov.d • mov.s FRdest, FRsrc FRdest, FRsrc FRdest = FRsrc FRdest = FRsrc • mul.d • mul.s FRdest, FRsrc1, FRsrc2 FRdest, FRsrc1, FRsrc2 FRdest = FRsrc1 * FRsrc2 FRdest = FRsrc1 * FRsrc2 • neg.d • neg.s FRdest, FRsrc FRdest, FRsrc FRdest = - FRsrc FRdest = - FRsrc FRdest, address FRdest, address address ← FRdest address ← FRdest • sub.d • sub.s FRdest, FRsrc1, FRsrc2 FRdest, FRsrc1, FRsrc2 FRdest = FRsrc1 – FRsrc2 FRdest = FRsrc1 – FRsrc2 • bc1t • bc1f Label Label Branch conditional; if flag is True; to Label Branch conditional; if flag is False; to Label (1 denotes coprocessor 1, the floating point coprocessor) • mfc1 • mtc1 Rdest, FPsrc Rsrc, FPdest Move contents of register FRsrc to CPU register Rdest Move contents of CPU register Rsrc to register FPdest l.d l.s s.d s.s