MIPS Instruction Set Reference (Subset)

advertisement

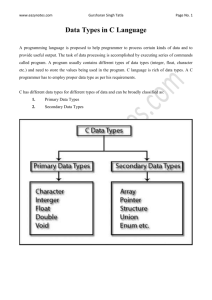

MIPS Core instruction set (subset)

Mnemonic

add

addi

addiu

addu

and

andi

beq

bne

j or b

jal

jr

lbu

lhu

lui

lw

nor

or

ori

slt

slti

sltiu

sltu

sll

srl

sb

sh

sw

su

subu

Description

Format Except

Add

Add Immediate

Add Immediate Unsigned

Add Unsigned

And

And Immediate

Branch On Equal

Branch On Not Equal

Jump

Jump And Link

Jump Register

Load Byte Unsigned

Load Half Unsigned

Load Upper Immediate

Load Word

Nor

Or

Or Immediate

Set (if) Less Than

Set Less Than Immed

S.L.T Immed Unsigned

Set Less Than Unsigned

Shift Left Logical

Shift Right Logical

Store Byte

Store Half

Store Word

Subtract

Subtract Unsigned

R

I

I

R

R

I

I

I

J

J

R

I

I

I

I

R

R

I

R

I

I

R

R

R

I

I

I

R

R

(1)

(1)(2)

(2)

(3)

(4)

(4)

(5)

(5)

Operation

Opcode / Funct (hex)

R[rd] = R[rs] + R[rt]

R[rt] = R[rs] + SignExtImm

R[rt] = R[rs] + SignExImm

R[rd] = R[rs] + R[rt]

R[rd] = R[rs] & R[rt]

R[rd] = R[rs] & ZeroExtImm

branch if(R[rs] == R[Rt])

branch if(R[rs] != R[Rt])

PC = JumpAddr

$ra = PC+4; PC = JumpAddr

PC = R[rs]

(2)

(2)

(2)

(3)

(2)

(2)(6)

(6)

(2)

(2)

(2)

(1)

R[rt] = {H16: imm, L16: zeros}

R[rt] = M[R[rs]+SignExtImm]

R[rd] = ~ (R[rs] | R[rt] )

R[rd] = R[rs] | R[rt]

R[rt] = R[rs] | ZeroExtImm

R[rd] =

(R[rs] < R[rt])

R[rt] = (R[rs] < SignExtImm)

R[rt] = (R[rs] < SignExtImm)

R[rd] =

(R[rs] < R[rt])

R[rd] = R[rs] << ShiftAmount

R[rd] = R[rs] >> ShiftAmount

?1:0

?1:0

?1:0

?1:0

M[R[rs] + SignExtImm] = R[rt]

R[rd] = R[rs] - R[rt]

R[rd] = R[rs] + R[rt]

0 / 20

8

9

0 / 21

0 / 24

C

4

5

2

3

0 / 08

0 / 24

0 / 25

F

0 / 23

0 / 27

0 / 25

D

0 / 2A

A

B

0 / 2B

0 / 00

0 / 02

28

29

2B

0 / 22

0 / 23

Other Integer Arithmetic Instructions and a Minimal Set for Double

div

divu

mfhi

mflo

mult

multu

Divide

Divide Unsigned

Move From Hi

Move From Lo

Multiply

Multiply Unsigned

R

R

R

R

R

R

l.d

s.d

mov.d

add.d

div.d

mul.d

sub.d

sqrt.d

recip.d

rsqrt.d

abs.d

neg.d

fd, addr

fs, addr

fd, fs

fd, fs, ft

fd, fs, ft

fd, fs, ft

fd, fs, ft

fd, fs

fd, fs

fd, fs

fd, fs

fd, fs

cvt.s.d

fd, fs #convert double to single

cvt.w.s

fd, rs #convert single to word

cvt.d.l

fd, fs #convert long long floating to double

Convert floating (y) to integer (x) with explicit rounding

round.x.y

rd, fs

ex. round.w.s

$r6, $f4

trunc.x.y

rd, fs

ceil.x.y

rd, fs

floor.x.y

rd, fs

Test and affect condition code c1 (3 from the list of 16)

c.cond.d

fs1, fs2 { Where cond can be eq, lt, le and others }

Branch if code c1 is true or false

bc1t

label # note that is a one(1), not an ell(L)

bc1f

label

(6)

(6)

Lo = R[rs] / R[rt]; Hi = R[rs] % R[rt]

Lo = R[rs] / R[rt]; Hi = R[rs] % R[rt]

R[rd] = Hi

R[rd] = Lo

{Hi,Lo} = R[rs] * R[rt]

{Hi,Lo} = R[rs] * R[rt]

0 / 1A

0 / 1B

0 / 10

0 / 12

0 / 18

0 / 19

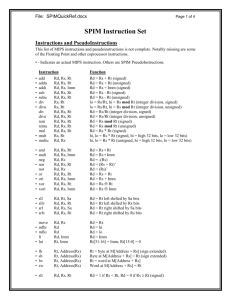

Pseudo-Instruction Set

blt

bgt

ble

bge

la

li

move

Branch Less Than

Branch Greater Than

Branch Less Than or Equal

Branch Greater Than or Equal

Load Address

Load Immediate

Move

branch if( R[rs] < R[rt] )

branch if( R[rs] > R[rt] )

branch if( R[rs] <= R[rt] )

branch if( R[rs] >= R[rt] )

R[rt] = R[rs] + ZeroExtImm

R[rd] = immedate

R[rt] = R[rs]

R[rt] = label

R[rs] = label + R[rt]

Exceptions

(Code: H16 highest order 16 bits, L2: lowest order 2 bits)

(1)

May cause overflow Exception

(2)

SignExtImm = 16 copies of sign bit [15] + imm16

(3)

ZeroExtImm = zeros16 + imm16

(4)

BranchAddr = 14 copies of sign bit + addr16 + zeros2

(5)

JumpAddr = Copy of top 4 bits of PC + jumpAddr26 + zeros2

(6)

Operands considered unsigned (not 2’s complement)

Note: The assembler can generate appropriate translations in situations where a 32 bit address or an immediate longer than 16

bits must be assembled. As a result, many apparent instructions are assembled as groups of pseudo-instructions, and some

pseudo-instructions can be assembled several different ways depending upon the addressing modes needed. For example:

lw $t2, label

add $t1, 0x12345

sw $t3, label($t4)

la $t4, array($s3)

li $t0, 0x12345

beq aLabelTooFar

Assembler directives (subset)

.align

.float

.asciiz

.globl

.byte

.half

.data

.lab

.double

.mask

.dword

.section

General Register Assignments

Name Numbers

$zero

$at

$v0-$v1

$a0-$a3

$t0-$t7

$s0-$s7

$t8-$t9

$k0-$k1

$gp

$sp

$fp

$ra

0

1

2-3

4-7

8-15

16-23

24-25

26-27

28

29

30

31

Use

.end

.text

.ent

.word

.extern

Floating Assignments

Preserved

The constant value 0

Assembler Temporary

Function Results

Function Arguments

Temporaries

Saved Temporaries

Temporaries

Reserved for O.S. Kernel

Global Pointer

Stack Pointer

Frame Pointer

Return Address

N.A.

No

No

No

No

Yes

No

No

Yes

Yes

Yes

Yes

$f0,$f2

$f4 - $f10

$f12, f14

$f16,$f18

$f20 - $f30

$fv0,$fv1

$ft0 - $ft3

$fa0,$fa1

$ft4,$ft5

$fs0 - $fs5

function return

temporaries

function args

more temps

saved regs

SPIM Exception Handler Services

Service

Code in $v0

Print Integer

Print Float

Print Double

Print String

Read Integer

Read Float

Read Double

Read String

1

2

3

4

5

6

7

8

Allocate Memory

Exit

9

10

Argument

Returned Value

$a0 == integer

$f12 == float

$f12 = double

$a0 == string address

$a0 == buffer address

$a1 == buffer length

$a0 == number of bytes

$v0 integer

$f0 float

$f0 double

(null terminated string is placed in buffer)

$v0 address

Basic Instruction Formats

R

I

J

(Remember, rd is rightmost here but leftmost in the instruction.)

opcode6 + rs5 + rt5 + rd5 + shamt5 + funct6

ex. addu $rd, $rs, $rt

opcode6 + rs5 + rt5 + immediate16

beq $rs, $rt, label ori $rd, $rs, 0xff

opcode6 + address26

j

loop

IEEE 754 Floating Point Single and Double Precision Formats (normalized values only)

All normalized values assume a 1 to the left of the binary point. Only the “fraction” is stored.

Sign1 + Exponent8 + Fraction23

(Exp bias 127)

(An exponent all zeros or all ones

Sign1 + Exponent11 + Fraction52

(Exp bias 1023)

signals a special value.)