COMPUTER ORGANIZATION UNIT-3 Micro operations and Register

advertisement

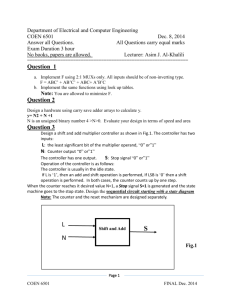

COMPUTER ORGANIZATION UNIT-3 Micro operations and Register Transfer Language: • Micro-operations are the basis for most sequential digital systems a. Movement of data from one register, memory location, or I/O device to another b. Modify stored values c. Perform arithmetic or logical functions d. Modify a stored value By performing a sequence of micro-operations to move and modify data, a sequential digital system performs a larger task Used to design a system – More efficient than using digital logic – Used to verify that the logic of the design is correct – Can be translated into the final hardware design of the system – The design looks something like a computer program written in a high level language – Can be input into a circuit analysis and design (CAD) program to simulate the behavior of the circuit under all conditions Fig:Implenentations of the micro operation x->y using(a)direct connection(b)Bus connection Fig:Implementation of the data transfer α: X Y IF α THEN X Y is written in RTL as α: X Y Fig:Implementation of Data Transfer α: X Y, Y Z To improve system performance do two or more transfers simultaneously Fig:Implementation of Data Transfer α: X Y, Z Y Can write to more than one place at a time, but cannot send to the same location for more than one place α: X Y, Z Y is OK α: X Y, X Z is not OK Fig: Three implementations of data transfers α: X 0 and β: X 1 Move a constant value into a register (a)Using a multiplexer to select data input (b)Using β as the data input ©Using the CLR signal What happens if α and β are both 1? 1. Need hardware to ensure that will not happen or 2. Make sure they have mutual exclusion using one of the following three α β’: X 0 α:X0 α β’: X 0 β:X1 α’ β :X 1 α’ β : X 1 Fig:Implementation of four-bit Data Transfer α: X Y Accessing single bits or subset of bits of multi-bit register • α: X(3-1) Y(2-0) • β: X3 X2 • : X(3-0) X(2-0),X3 or X(2-0,3) Arithmetic and logical micro-operations Transferring data between memory and registers • • To transfer between register AC and memory, first move address into address register and then perform transfer – AR 55 – M[AR] AC or AC M[AR] If decide AR is always the address register – M AC and AC M can be used without referring to AR Using RTL to Specify Digital Systems: Consider Dflipflop shown in below fig.Its function can be expressed by RTL statement LD:Q->D (a) With out clear input (b) With clear input Fig:Data paths of the system to implement the RTL code using direct connect Fig:Complete design of the system to implement the RTL code using direct connections Fig:Implementation using bus with tri-state buffers Advantage of bus over direct connect: Bus system can be partitioned and their sections designed separately; task of buffer is not to pass the value of M on to the bus so it can be read in by register R, rather, its task is to place the contents of M on to the bus so that it can be read by whatever register should read it in. Fig:Complete design of the system to implement the RTL code using a bus and multiplexer More Complex Digital Systems and RTL: Modulo 6 counter: S0 S1 S2 S3 S4 S5 S0 … State Diagram for Modulo 6 Counter RTL code for the counter: (S0 + S1 + S3 + S3 + S4)U: V V + 1, C 0 S5U + S6 + S7: V 0, C 1 + on left of : is OR, on right of : is arithmetic add Fig:Implementation of RTL code for Modulo 6 counter using a register Fig:Implementation of RTL code for Modulo 6 counter using a counter TOLL BOOTH CONTROLLER: A toll booth controller has two external sensors. State diagram for toll booth controller State value assignments for the toll booth controller RTL code for the toll booth controller, excluding output RTL code for the toll booth controller outputs Complete RTL code for toll booth controller VHDL-VHSIC Hardware Description Language: VHDL Syntax VHDL design with high level of abstraction VHDL design with low level of abstraction VHDL design code has three primary sectors Library declaration Entity section Architecture section VHDL file to implement the modulo 6 counter using a high level of abstraction: Logic diagram for modulo 6 counter based on VHDL in next slide VHDL file to implement the modulo 6 counter using a low level abstraction: