12 - EEWeb

advertisement

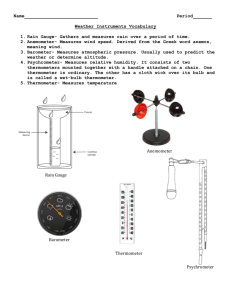

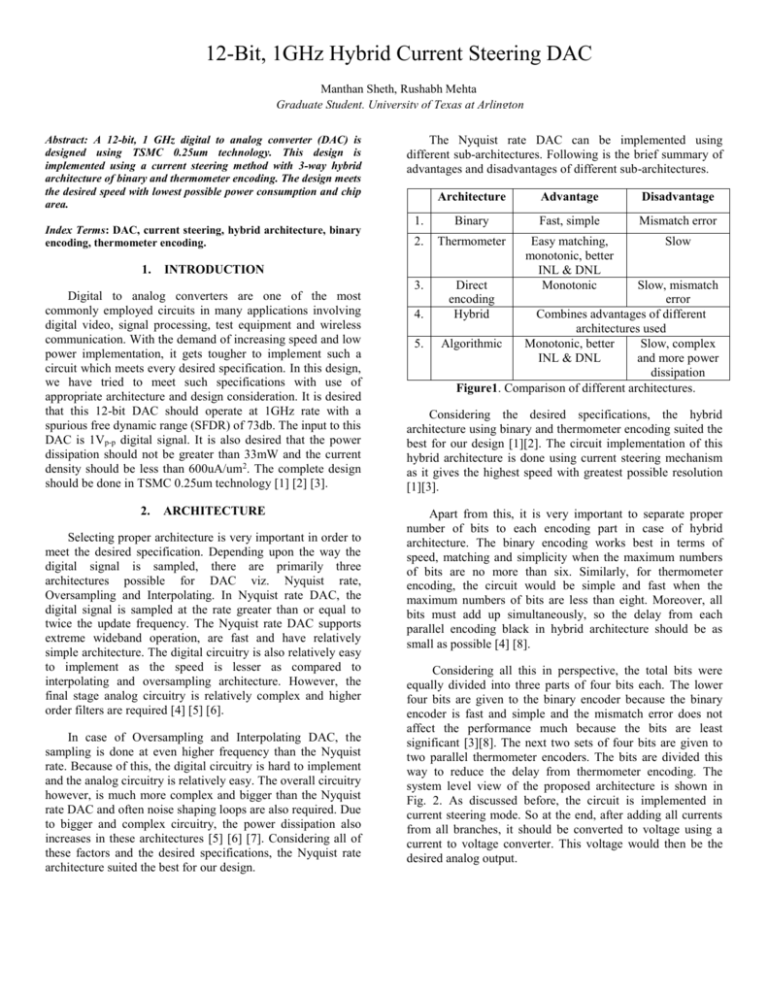

12-Bit, 1GHz Hybrid Current Steering DAC 1 Manthan Sheth, Rushabh Mehta Graduate Student, University of Texas at Arlington Abstract: A 12-bit, 1 GHz digital to analog converter (DAC) is designed using TSMC 0.25um technology. This design is implemented using a current steering method with 3-way hybrid architecture of binary and thermometer encoding. The design meets the desired speed with lowest possible power consumption and chip area. Index Terms: DAC, current steering, hybrid architecture, binary encoding, thermometer encoding. 1. Architecture Advantage Disadvantage 1. Binary Fast, simple Mismatch error 2. Thermometer Slow 3. Direct encoding Hybrid Easy matching, monotonic, better INL & DNL Monotonic INTRODUCTION Digital to analog converters are one of the most commonly employed circuits in many applications involving digital video, signal processing, test equipment and wireless communication. With the demand of increasing speed and low power implementation, it gets tougher to implement such a circuit which meets every desired specification. In this design, we have tried to meet such specifications with use of appropriate architecture and design consideration. It is desired that this 12-bit DAC should operate at 1GHz rate with a spurious free dynamic range (SFDR) of 73db. The input to this DAC is 1Vp-p digital signal. It is also desired that the power dissipation should not be greater than 33mW and the current density should be less than 600uA/um2. The complete design should be done in TSMC 0.25um technology [1] [2] [3]. 2. The Nyquist rate DAC can be implemented using different sub-architectures. Following is the brief summary of advantages and disadvantages of different sub-architectures. ARCHITECTURE Selecting proper architecture is very important in order to meet the desired specification. Depending upon the way the digital signal is sampled, there are primarily three architectures possible for DAC viz. Nyquist rate, Oversampling and Interpolating. In Nyquist rate DAC, the digital signal is sampled at the rate greater than or equal to twice the update frequency. The Nyquist rate DAC supports extreme wideband operation, are fast and have relatively simple architecture. The digital circuitry is also relatively easy to implement as the speed is lesser as compared to interpolating and oversampling architecture. However, the final stage analog circuitry is relatively complex and higher order filters are required [4] [5] [6]. In case of Oversampling and Interpolating DAC, the sampling is done at even higher frequency than the Nyquist rate. Because of this, the digital circuitry is hard to implement and the analog circuitry is relatively easy. The overall circuitry however, is much more complex and bigger than the Nyquist rate DAC and often noise shaping loops are also required. Due to bigger and complex circuitry, the power dissipation also increases in these architectures [5] [6] [7]. Considering all of these factors and the desired specifications, the Nyquist rate architecture suited the best for our design. 4. 5. Slow, mismatch error Combines advantages of different architectures used Algorithmic Monotonic, better Slow, complex INL & DNL and more power dissipation Figure1. Comparison of different architectures. Considering the desired specifications, the hybrid architecture using binary and thermometer encoding suited the best for our design [1][2]. The circuit implementation of this hybrid architecture is done using current steering mechanism as it gives the highest speed with greatest possible resolution [1][3]. Apart from this, it is very important to separate proper number of bits to each encoding part in case of hybrid architecture. The binary encoding works best in terms of speed, matching and simplicity when the maximum numbers of bits are no more than six. Similarly, for thermometer encoding, the circuit would be simple and fast when the maximum numbers of bits are less than eight. Moreover, all bits must add up simultaneously, so the delay from each parallel encoding black in hybrid architecture should be as small as possible [4] [8]. Considering all this in perspective, the total bits were equally divided into three parts of four bits each. The lower four bits are given to the binary encoder because the binary encoder is fast and simple and the mismatch error does not affect the performance much because the bits are least significant [3][8]. The next two sets of four bits are given to two parallel thermometer encoders. The bits are divided this way to reduce the delay from thermometer encoding. The system level view of the proposed architecture is shown in Fig. 2. As discussed before, the circuit is implemented in current steering mode. So at the end, after adding all currents from all branches, it should be converted to voltage using a current to voltage converter. This voltage would then be the desired analog output. 2 Figure 2. Hybrid Architecture of 12-bit DAC 3. BINARY ENCODER DESIGN The least significant four bits are given to the binary encoder. Depending on the logic at these four bits, the amount of current from this branch would change. For this design, the total maximum current has been set to 1mA. This means when all 12 bits are logic high, then total current after addition from all branches should equal 1mA. As per this calculation, the maximum current that can flow from binary encoding branch equals ~3.84uA. Now since the encoding is binary weighted, a unit current source of ~256nA is required. Figure 4. Layout of unit current source for binary encoder Figure 5. Output from unit current source Figure 3. Unit current source for binary encoder This unit current source corresponds to current output when the least significant bit is high. For the 2 nd, 3rd and 4th bit, the current would be 2, 4 and 8 times of the unit current respectively. Fig. 3 and 4 shows the circuit and layout for unit current source. Figure 5 shows the output from the unit current source which is approximately 246nA. Figure 5 shows the total output from binary encoding section when all 4 bits are logic high. This current is approximately 3.67uA. 3 D1 D0 Y0 Y1 Y2 Y3 0 0 1 0 0 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 1 1 Y0 = VDD Y1= A1+A0 Y2= A1 Y3= A1.A0 Figure 8. Truth table for control signals Figure 6. Maximum output from binary encoder stage 4. THERMOMETER ENCODER DESIGN There are two thermometer encoding sections in this design. The design of both of the encoders would be almost similar except the value of the unit current sources. As per the 1mA requirement of total current, the value of current from the center branch would be ~57.6uA while from the top branch it would be ~938.56uA. The thermometer encoder would employ 15 unit current sources. Figure 9. Thermometer encoder control signal circuit Figure 7. Thermometer encoder The decoding circuit for rows and columns of the 2-D array of current sources is illustrated in Fig. 7, 8 and 9. Depending on the input bits D0 and D1, the control signals Y0-Y3 would change and this is illustrated with a truth table in Fig. 8. Figure 10. Layout of control signal circuit 4 Figure 11. Output of control signals Y1, Y2 and Y3 depending on the input bits D0 and D1. Figure 13. Layout of unit current source for 1st thermometer encoder Fig. 10 shows the layout of the control signal circuit, while Fig. 11 shows the output of the control signals for the specific set of inputs indicated in the figure. As discussed before, there are two sets of thermometer encoders connected in parallel and both of them have different values of unit current sources connected in the array. For the first encoder, the value of the unit current source comes out to be 57.6uA/15= 3.84uA. The circuit for this unit current source is shown in Fig. 12 and the layout is shown in Fig. 13. Fig. 14 shows the array of 15 current sources connected together to form current source array for 1st thermometer encoder. The maximum current output after addition comes out to be 55.7uA and this is shown in Fig. 15. Figure 14. Array of 15 unit current source for 1 st thermometer encoder Figure 12. Unit current source for 1st thermometer encoder. Figure 15. Maximum output from 1st thermometer encoder 5 In 2nd thermometer encoder, the control signal circuit and the current source array is exactly similar to the 1st stage. The only thing which changes is the value of the unit current source which now becomes 938.56uA/15= 62.5uA. Fig. 15 shows the circuit for getting this current and Fig. 16 shows the layout. Figure 18. Current source array for 2nd encoder Figure 16. Unit current source for 2nd thermometer encoder Figure 19. Maximum output from 2nd current source array 5. Figure 17. Layout for unit current source of 2nd encoder Fig. 18 shows the layout for the current source array of 2nd thermometer encoder. The maximum output is shown in Fig. 19 which is around ~932uA. I-V CONVERTER DESIGN After the currents from the three parallel branches add up, the current has to be converted into voltage. This can be done using a current to voltage converter which is essentially a current mirror with a PMOS load. The circuit for this is shown in Fig. 20. As the current changes from 0 to 1mA, the voltage swing changes from 2.5V to 0.7V in the simulation which is shown in Fig. 21. However simulation with the extracted layout model gives the swing of 2.5 V to 120mV. This swing can further be improved by placing a level inverter/shifter at the output of I-V converter. 6 Figure 20. I-V converter circuit Figure 22. DAC circuit schematic Figure 21. Response of I-V converter 6. SIMULATION RESULT Fig. 22 shows the circuit diagram of the whole DAC assembled together and Fig. 23 shows the entire layout. The layout matches exactly with the schematic and the result after parasitic extraction matches almost with the schematic simulation. The results from some arbitrary digital signals are shown in Fig. 24 and 25. It can be concluded from these results that the circuit can operate at 1GHz speed but there are some glitch problems. For this, an anti-glitch filter at the output stage would be required. Moreover, the analog output swing can be improved using an inverter/ level shifter circuit. Figure 23. DAC circuit layout 7 Figure 24. Simulation result when input data bits (D0-D11) are all same and as indicated in the figure in first frame Figure 25. Differences in circuit simulation and extracted layout model simulation for some arbitrary input digital signal 8 7. CONCLUSION AND FUTURE WORK The simulation results shows that the DAC operates at a fairly good speed but at speeds around 1GHZ, glitch problems increase and the output becomes distorted. This can be improved by using a de-glitch filter at the output stage. Moreover, the output swing can be increased by using an analog voltage inverter can a level shifter. The power dissipation was not calculated but the circuit can be optimized further more to reduce the static and dynamic power losses. The design seems to work well and if further optimized and rigorously simulated and verified, it might work at 1GHz speed with low power dissipation and lowest on-chip area. 8. REFERENCES [1] Maruthi Chandrasekhar Bh, Dr. Sudeb Dasgupta “A 1.2 Volt, 90nm, 16-bit Three Way Segmented Digital to Analog Converter (DAC) for Low Power Applications,” 10th International Symposium on Quality Electronic Design, ISBN 978-1-4244-2953-0/09, pp.447 - 450 , 2009. [2] Yannan Ren, Fule Li, Chun Zhang, Zhihua Wang, “A 400MS/s 10-bit Current-steering D/A Converter,” Institute of Microelectronics of Tsinghua University, Beijing, China, ISBN 978-4244-4888-3/09,pp.533 – 536, 2009. [3] Tan G.H., Surpajo B.S., Wagiran R., Sidek R., “The Design of 8-bit CMOS Digital To Analog Converter,” ICSE2000 Proceedings,pp.231 - 234, Nov. 2000. [4] Paolo Crippa, Claudio Turchetti, Massimo Conti, “A Statistical Methodology for the Design of High-Performance CMOS Current-Steering Digital-to-Analog Converters,” IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol.21, No.4, pp.377 - 394, April 2002. [5] B. Razavi, “ Design of Analog CMOS Integrated Circuits”, McGraw-Hill, ISBN 0-07-238032-2. [6] B. Razavi, “ Principles of Data Conversion System Design”, IEEE press, ISBN- 0-7803-1093-4. [7] M. Gusttavsson, “CMOS Data Converters for Communication”, Kluwer Academic press, ISBN- 0-79237780-X. [8] P Allen. et al., CMOS Analog Circuit Design”, Oxword, ISBN- 0-19-51164-5.