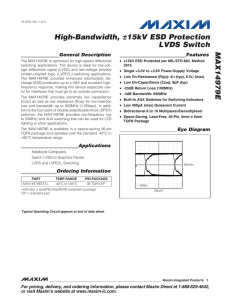

UNUSED LVDS INPUT TERMINATION

advertisement

UNUSED LVDS INPUT TERMINATION In case of one set data bus is not needed (i.e. Channel A/B DAB[15:0]P/N port or Channel C/D DCD[15:0]P/N), the non-active, unused pins can be left unconnected (floating) or connected to a nominal, differential LVDS active HIGH or active LOW voltage. The choice of LVDS connections to the unused LVDS ports will not affect the operations of LVDS receiver, digital functions such as mixers, NCO, and QMC, and analog output stage. However, if the system designer wishes to implement the following features in the end system, the designer may need to connect the unused ports to a known logic value: 1. During system prototyping stage, the designer may perform timing analysis and data transfer error checking on the LVDS ports using the DAC34H84’s data pattern checker functionality. 2. The DAC34H84 has parity check feature to ensure continuous validity monitoring of data transfer. For the case such as 32-bit parity, the mode requires known logic values on the unused LVDS ports. The following example allows the termination of the unused LVDS ports to a known logic HIGH value. As shown in Figure TBD, The design involves the connection to the DIGVDD rail and one RSET resistor to bias the positive terminals of unused LVDS ports to be 1.2V and negative terminals of unused LVDS ports to 1.0V. The design keeps the minimum common mode input voltage of the LVDS input to be above 1.0V, and keeps the differential LVDS voltage to be 200mV. Since the design expects the differential voltage on the unused ports to be static, the differential LVDS voltage can be as low as 100mV to maintain a logic HIGH. Refer to Electrical Characteristic – Digital Specifications Table for detail of LVDS Input requirements. DIGVDD (1.2V Nominal) LVDS P Terminals (Parallel by M) REQ or ZT/M LVDS N Terminals (Parallel by M) RSET · M Unused LVDS Ports Connected in Parallel. · Keep Positive Terminals at 1.2V. · Keep Static Differential Voltages above 100mV. Figure TBD. Unused LVDS Ports Connected to Static Logic High Differential Voltage. 1. Connect the positive terminals of unused LVDS ports in parallel to DIGVDD supply at 1.2V nominal. For instance, connect DAB[15:0] positive pins together to DIGVDD. 2. Connect the negative terminals of unused LVDS ports in parallel to a RSET resistor to ground. 3. The REQ value is the equivalent, parallel resistance of the on-chip termination for all the unused LVDS ports. In byte wide data interface format, eight ports were unused, therefore, the REQ is eight parallel ZT. Worst case ZT value of 135ohm is used in the design to account for the lowest possible current IEQ and the worst case common mode on the negative LVDS terminals. Another analysis will be performed with ZT value of 85ohm for worst case differential LVDS voltages. 4. With Ohm’s Law, the following equation describes the relationship between RSET and REQ. 𝑅𝑆𝐸𝑇 1.0 = 𝑅𝑆𝐸𝑇 + 𝑅𝐸𝑄 1.2 𝑅𝑆𝐸𝑇 = 4.988𝑅𝐸𝑄 5. With REQ of 16 parallel, 135ohm ZT (or 8.4375ohm equivalent), RSET is 42.2ohm with standard 1% resistor value. IEQ is approximately 23.6mA. The expected voltage at negative terminals of LVDS ports is approximately 1.0V. The differential LVDS voltage is 200mV. 6. With same RSET of 42.2ohm, if the REQ has dropped to 16 parallel, 85ohm ZT (or 5.3125ohm equivalent), IEQ is approximately 25.3mA. The expected voltage at negative terminals of LVDS port is approximately 1.06V. The differential LVDS voltage is 138mV. As long as the static LVDS differential voltage is above 100mV, the LVDS port will register a logic HIGH value for the data. Depending on the DAC34H84 functionality required, additional unused LVDS ports such as ISTRP/N, SYNCP/N, or PARITYP/N can also be left unconnected (floating) or connected to a nominal, differential LVDS active HIGH or active LOW voltage. The usage of these ports depends mainly on the FIFO synchronization settings and parity checking settings. The unused ISTRP/N, SYNCP/N, or PARITYP/N ports can be connected in parallel with the unused LVDS data port with adjustments to the RSET resistor value.