ENGR 1310 Laboratory #3 (all groups meet 1:00 01

advertisement

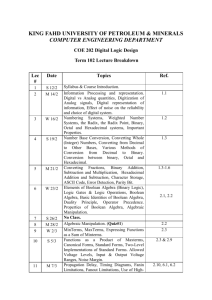

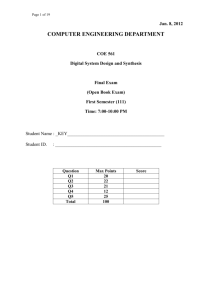

EGR 1301 Lab 3 EGR 1301: Introduction to Engineering Lab 3: Binary Adder and SR Flip-flop Objective To expose the student to digital electronics by constructing and testing a binary full adder and an SR flip-flop. Introduction Binary Adder A binary full adder is a digital circuit that performs the addition of multiple (in this case three) binary numbers. Each of the three inputs, A, B, and C, represent a one-bit binary number: either 0 or 1. That is, our circuit will add three binary numbers, A+B+C (plus sign here represents binary addition, not “OR”), each of which may be either 0 or 1. Since this sum can be as high as 3, a two-bit output is required. The four possible output values are given in Table 1 below along with their decimal equivalents. Table 1. Two-digit Binary. Number of 1’s on Inputs 0 1 2 3 Decimal Sum 0 1 2 3 Binary Sum 00 01 10 11 MSB 0 0 1 1 LSB 0 1 0 1 The abbreviation LSB stands for the least significant bit of the sum, and MSB stands for the most significant bit of the sum. Designing an adder circuit is beyond the scope of this lab; however, without a great deal of difficulty, we can verify that a given circuit does, in fact, produce the required output by filling in the appropriate truth table. SR Flip-flop An SR flip-flop is a digital logic circuit which allows a binary value to be stored. This idea (although not an SR flip-flop) is the basis for all computer memory (i.e. RAM). “S” stands for “Set” and “R” stands for “Reset.” These two inputs allow one to “set” (make a 1) or “reset” (make a 0) the output. As with the adder, we will verify the truth table for a single SR flip-flop. 2/9/2016 3:49 PM Page 1 of 6 EGR 1301 Lab 3 Integrated Circuits Before building these circuits, you need to know a little about integrated circuits (often called IC’s or “chips”). Each chip has a divot and/or half-circle etched in the top which designates which end is “up” or pin #1. See Figure 1. Divot which designates pin #1 (pin under arrow) Half-circle which designates “up” Figure 1. IC chip showing divot and half-circle. When placing an IC on a breadboard (the white area on your Boe-Bot), the chip should straddle the large break in the board. This allows each of the chip’s pins to be in separate rows of the breadboard (recall that all five holes in a row of the breadboard are connected together). You will need Lastly, IC’s are numbered according to their function. An IC that contains four two-input NAND gates is called a 7400. The number that’s actually printed on the chip may contain more characters than that, however. For instance, a DM74LS00N is a 7400 chip where the DM, LS, and N specify other properties (that you do not need to worry about at this point). Another example is the SN74LS86N. This is a 7486, or quad, two-input XOR chip. The last chip we will use is the 7402, which contains four two-input NOR gates. Warning! Pay careful attention to how you place and wire the chips on your breadboard. Incorrectly connecting chips can destroy them! Procedure Binary Adder In hardware, 1’s and 0’s are represented with voltages. There are several ways to express these: 1 = HIGH = +5 V = Vdd = “on” 0 = LOW = 0 V = Vss = “off” Since you do not have enough switches/buttons included with your Boe-Bot, you will simply use wires to act as switches. Thus, an input of 1 means plugging that wire into Vdd. Warning! Inputs should only be connected to either Vdd or Vss, not both. Figure 3 is a wiring diagram that shows how to implement the full adder schematic shown in Figure 2. Notice that the half-circle is included in the diagram so that you can orient the IC’s correctly. Use 2/9/2016 3:49 PM Page 2 of 6 EGR 1301 Lab 3 the 7400 and 7486 integrated circuits to build this circuit on your Boe-Bot and fill in the truth table in Table 2. After completing the truth table, demonstrate the proper operation of your circuit to your instructor. Circuit Demonstrated Successfully:________________ Table 2. Truth table for a full adder. A 0 0 0 0 1 1 1 1 Input B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Output Binary Sum Decimal Sum MSB LSB X Y Z V W Figure 2. Full adder circuit schematic. 2/9/2016 3:49 PM Page 3 of 6 EGR 1301 Lab 3 Vdd 7400 W Z E V MSB 470 F + Vdd Vss Vdd Vss A 7486 B X Vss D Vdd Vss C Y LSB 470 + Vss Vss Figure 3. Full adder wiring diagram. 2/9/2016 3:49 PM Page 4 of 6 EGR 1301 Lab 3 SR Flip-flop Since the SR flip-flop has two binary inputs, there are four input combinations: 00, 01, 10, and 11. BUT, the output also depends on the initial state of the output (Q1(t)). A couple of notes about the inputs: 00 means neither input is “on,” in which case we don’t want to change the current output. 01 and 10 are “reset” and “set,” respectively. 11 is a case where the output enters an undesired state, which would be avoided in an actual application. Here, you will still verify that that is the behavior. The best way to analyze this circuit is to start with S and Q1(t) applied to gate Y, which yields Q2(t+1). Now, use Q2(t+1) and R applied to gate X to get Q1(t+1). If Q1(t+1) equals Q1(t), you’re finished; the circuit is in a “stable” state. If not, repeat the same process (start with S and Q1 …). Similarly to the adder, use the 7402 integrated circuit and wiring diagram in Figure 5 to implement the circuit for an SR flip-flop shown in Figure 4. Complete the truth table in Table 3 and demonstrate your circuit to your instructor. Circuit Demonstrated Successfully:________________ Table 3. Truth table for an SR flip-flop. Input S R 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Initial State Q1(t) 0 1 0 1 0 1 0 1 Output Q1(t+1) Q2(t+1) R Q1 X S Q2 Y Figure 4. SR flip-flop circuit schematic. 2/9/2016 3:49 PM Page 5 of 6 EGR 1301 Lab 3 Figure 5. SR flip-flop wiring diagram. 2/9/2016 3:49 PM Page 6 of 6