A 2.4/5.8 GHz Subthreshold Mixer for Ultra Low-Voltage Low

advertisement

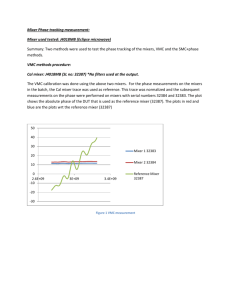

A 2.4/5.8 GHz Subthreshold Mixer for Ultra Low-Voltage LowPower Applications Zahra GHANE FASHTALI* Mahrokh MAGHSOODI Department of Electrical Engineering, University of Guilan, Rasht, Iran *Corresponding Author: E-mail: zahra.ghane1986@gmail.com Abstract This paper describes a 2.4/5.8 GHz CMOS down-conversion mixer for ISM band applications. The subthreshold operation of MOS transistors is used to achieve an ultra low supply voltage and low power consumption. In order to decrease the stacked transistors, the RF and LO stages of the mixer are merged together so that the RF and LO signals are applied to the source and gate of the devices. The proposed mixer was implemented by using a TSMC 0.18-µm CMOS process. The simulation results show a high conversion gain of 12.4/10.2 dB, a DSB noise figure of 11.3/19.6 dB and an IIP3 of -5/-1 dBm for RF frequency of 2.4/5.8 GHz and the circuit draws only 14.5 µA from a 0.5 V. Since the power consumption of the mixer is only 7.25 µW, it makes the mixer suitable for low-voltage and low-power applications. Keywords: ISM- band, low-power,low-voltage, mixer, subthreshold 1. INTRODUCTION Recently, wireless communication has developed the demand for low-cost and low-power RF circuits which can support multi-band operation in a single chip, such as the IEEE 802.11 a/b/g wireless local area network (WLAN) dual-band system. Conventional design strategies have adopted different single-band transceiver circuits in parallel for different frequency bands [1]. One of the key component in the RX chain of wireless devices is the down-conversion mixer. A frequently used active mixer topology is the so called Gilbert-cell mixer incorporating a RF transconductance stage, a switching stage and a load stage. This circuit topology is preferred to passive circuits due the offered conversion gain, which relaxes the gain and noise requirements on the preceding LAN and the following IF stage, respectively. Although good performance can be achieved, the Gilbert-cell mixer usually suffers from large power dissipation and the need for high supply voltages [2]. Therefore, designing a low power dissipating mixer which is operating with a low LO source power will result in an immense power consumption reduction of the RF transceiver [3]. Recently, a few low-voltage and low-power operation topologies using CMOS technologies have been proposed in [4-9] for radio frequency (RF) mixer circuits. Inductor-capacitor (LC) tanks are used to achieve low-power operation in [4], but in CMOS technology, Q-value of the spiral inductor is relatively low, and the inductor occupies a lot of chip space. A transformer-based architecture is adopted to reduce dc power consumption in [5], but the 3-dB bandwidth is quite narrow because of the bandwidth limitation of the transformer. In order to achieve a low-voltage operation, a cascode method can be applied to the mixer core design, which used the PMOS transistor stacking on the NMOS transistor [6], but the dc supply voltage is still 1.8 V. In [7-9], MOS transistor is used as a four-terminal device so that RF and LO signals are applied to the gate and bulk while the mixing product is produced from the drain, this kind of mixer can be operating on a low supply voltage, 1 but it is difficult to predict the mixer performance due to the lack of suitable model for the transistor in such working mode. In addition, for this bulk injection technique at least a twin-well technology is required. In this paper, the RF and LO stages are merged together to avoid the stacked structure that used in conventional Gilbert-cell mixer and the subthreshold operation of the MOS transistors are used to design the proposed mixer. The design concept is that the RF and LO signals are applied to the source and gate respectively, and the IF signal is extracted from the drain. So, the required bias will be smaller than the threshold voltage of the devices, and then results in the low-voltage and low-power operation. In addition, the proposed mixer is suitable for dual-band frequencies, with centre frequencies in 2.4 GHz and 5.8 GHz. Also, to the best of our knowledge, this work demonstrates the highest figure-of-merit (FOM) among the previously reported CMOS mixers. In addition, so far the dc supply voltage hasn’t scaled down to threshold voltage in any mixer design. The subthreshold operation of the MOS transistors is described in Section II. Section III describes the mixer core and working principles of the mixer. Section IV shows the simulation results of the proposed mixer. Finally, conclusion is stated in section V. 2. SUBTHRESHOLD OPERATION OF MOSFET TRANSISTORS In the actual MOSFET, drain current is not zero for all values of VGS below VTH. Even negative values of Veff , occurring as VGS approaches VTH , may lead to drain current that is no longer negligible for wide channel devices . In this case, the drain current of the MOSFET transistors may be notable, because of the large width of the devices. This current is referred to as subthreshold current. The subthreshold region exists for values of VGS less than VTH when positive drain current flows. In this case, the diffusion current is the principle current of the channel. This region that includes subthreshold conduction is referred to as the weak-inversion region [10]. The approximate relation between drain current and gate-to-source voltage in the weak-inversion region is given by [11] 𝐼𝐷 = 𝑊 𝐼 𝑒 𝐿 𝐷0 𝑞𝑉𝐺𝑆 /𝑛𝑘𝑇 . (1) where n and ID0 can be extracted from experimental data [10]. Since, the subthreshold operation of the MOS transistor is used to design the proposed mixer, an overview of the MOS operation in this region is explained in the following of the paper. Assume, we have two transistors which one of them is biased in strong-inversion region (M1) and the other one is biased in the subthreshold region (M2). Obviously, in these two operations, the gm of transistors M1 and M2 are not equal. gm1 and gm2 can be computed by using the following formulas. 𝑔𝑚1 = √2𝜇𝑛 𝐶𝑜𝑥 𝐼 𝑔𝑚2 = 𝑛𝑉𝐷 . 𝑇 𝑊 𝐼 . 𝐿 𝐷 (2) (3) That VT is the thermal voltage and typically n is between 1 and 2. Therefore, if we want to have two transistors with equal drain current, that one of them operates in strong-inversion region and the other is biased in the subthreshold region, the W value of the transistor that operates in the subthreshold must be much more than the W value of the transistor that operates in strong-inversion region. To have a better 2 understanding of this topic, I-V curve of two transistors, while M1 is biased in strong inversion region and M2 is biased in the subthreshold, as given in [12], shown in Fig. 1. From the above figure it can be seen that, at the drain current of 10-4 A, VGS1 = 0.6 V > VTH and VGS2 = 0.4 V < VTH .Despite, the drain current similarity of two transistors, gm2 > gm1 because of W2 >> W1. Thus, by increasing the W value of the transistors in the subthreshold region, an operation as strong-inversion can be achieved. In fact, increasing the width of the transistors has advantages and disadvantages and since, the relationship between the width and the 1/f noise is reversed, so this results in the 1/f noise reduction. Equation (4) shows that the input referred 1/f noise is inversely proportional to the transistor width. 2 𝑉1/𝑓 = 𝐾𝑓 𝑊𝑒𝑓𝑓 ∙𝐿𝑒𝑓𝑓 ∙𝐶𝑜𝑥 ∙𝑓 (4) Kf is the 1/f noise coefficient that depend on the process, Weff is the effective width, Leff is the effective length, and Cox is the gate oxide capacitance per unit area. In addition, an increase in the transistor width will lead to the increase of parasitic capacitances, and then since, f=1/2πRC it is difficult to achieve high frequency operation in RFIC circuits design. However, in order to achieve high gm that results in the gain and linearity improvement, gm increasing is inevitable. In the past, in analog circuit design, circuits have been biased in the subthreshold region in order to achieve high values of gm for low current operation [13]. However, this idea is used only in a few RF circuit design owing to the nonlinear I-V characteristics of the transistor subthreshold, which decline the overall performance of the circuit. On the other hand, to achieve desirable performance we have to increase the width of the transistors, hence the layout considerations of the devices must be taken into account. 3. MIXER STRUCTURE AND PERFORMANCE ANALYSIS The circuit schematic of the proposed mixer is shown in Fig. 2. PMOS transistors M1-M4 make the transconductance and switch stages that merged together. In this circuit the RF and LO signals are applied to the source and gate of the devices, while the IF output signal is produced from the drain. In order to achieve a low-voltage and low-power performance, these devices are biased in the weak-inversion region and operate in the subthreshold condition. NMOS transistors M5 and M6 are used as active loads, and make the load stage of the introduced mixer. To access the desirable performance, these transistors are biased in the moderate-inversion region. To make mixer loads, we have to choose among resistors, LC circuit or transistors. The use of LC circuit is not an integrable solution. The use of transistors as active loads gets higher gain than resistors [14], for equivalent power consumption. Moreover, this will allow even higher gain without using up too much voltage headroom and allows for smaller on chip space requirements as compared to a resistor. Transistors M7-M10 make the bias circuit of the proposed mixer, and to significantly reduce the power consumption, the bias circuit consumes very little power. In order to design the presented mixer, a few of devices are used, this results in a significant reduction in the supply voltage as well as power consumption Moreover, despite having the mixer circuit structure quite simple, yet it shows a good performance. Notice that, since the supply voltage of the circuit is equal to the threshold voltage, hence we can’t bias the circuit transistors in the saturation region and we have to bias them in the weak or moderate inversion regions. To determine the W sizes of the transistors, we can’t use the gm and ID formulas in the saturation 3 region. In fact, the ID and gm formulas in the saturation region are not usable for computing the W sizes of transistors when they are biased in the weak-inversion region. So simulation is the best way to obtain the amount of W. In fact, by plotting the conversion gain against the W, we can specify the W that leads to the maximum conversion gain. For example, the conversion gain against the width of the transistors M1M4 (W1-4) is plotted in Fig. 3 which shows that the maximum conversion gain is occurred in W1-4 of 220 µm. Fig. 4 shows the simulated conversion gain as a function of the width of transistors M5 and M6 (W5,6), which exhibits that the maximum conversion gain can be achieved when W5,6 is equal to 110 µm. As can be seen from Fig. 3 and Fig. 4, the W values of the transistors to access optimum performance are relatively high that due to the subthreshold operation of these transistors. Because, when the transistors are biased in the weak-inversion region, they must be wide, otherwise, we can’t achieve to a desirable performance. In all transistor devices L is constantly equal to 0.18-µm. To find the required voltage to bias the transistors M1-M4 (VG1-4), the conversion gain as a function of the VG1-4 is plotted in Fig. 5. As it can be see, the conversion gain reaches the highest value for VG1-4 = 200 mV. Since, the supply voltage of the circuit is equal to the threshold voltage, thus, the required voltage to bias the transistors M5 and M6 to operate them in the moderate-inversion is equal to the supply voltage, because: VB= VGS5,6 = VTH0 + Vod5,6 ≥ 0.5 V (5) Thus, even if Vod5,6 (Vod is the overdrive voltage) is equal to zero, VB will be greater than VDD. So VB is equal to VDD. As Fig. 2 shows, the diode-connected transistors (transistors M7-M10) are used to design the bias circuit of the proposed mixer. 4. SIMULATION RESULTS The proposed down-conversion mixer has been simulated in ADS with the TSMC 0.18-µm CMOS process. Simulation results for two different frequency bands are given, and a comparison is made between them. The conversion gains against LO power for 2.4 GHz and 5.8 GHz RF frequencies are plotted in Fig. 6, and Fig. 7, respectively, which shows a conversion gain of 12.4 dB in 2.4 GHz and 10.2 dB in 5.8 GHz, with an LO power of 0 dBm. The third-order intermodulations at 2.4 GHz and 5.8 GHz are plotted in Fig. 8 and Fig. 9, respectively, which feature an input third-order intercept point (IIP3) of -5 dBm at 2.4 GHz and -1 dBm at 5.8 GHz, and an input 1 dB compression point (IP1dB) of – 19 dBm in 2.4 GHz and -13 dBm in 5.8 GHz RF frequency. The single-sideband (SSB) noise figures and double-sideband (DSB) noise figures against LO power from -5 dBm to 20 dBm for 2.4 GHz and 5.8 GHz RF frequencies are plotted in Fig. 10 and Fig. 11, respectively where the IF frequency is fixed at 100 MHz. The DSB NF in 2.4 GHz and 5.8 GHz are 11.3 dB and 19.6 dB, respectively. The conversion gains against RF frequency for 2.4 GHz and 5.8 GHz are plotted in Fig. 12 and Fig. 13, respectively, the conversion gain in 2.4 GHz is 12 dB, and in 5.8 GHz is 9.8 dB. With comparing the simulation results it can be understood that with the same simulation parameters, the conversion gain in 2.4 GHz is higher than 5.8 GHz, but the linearity in 5.8 GHz is better than 2.4 GHz. Since the relationship between the conversion gain and linearity is reversed, this deduction is 4 completely true. Moreover, the noise figure in 5.8 GHz RF frequency is worse than 2.4 GHz, and since the relationship between the conversion gain and noise is straight, the mixer performance is completely acceptable. The optimum dc supply voltage (VDD) is only 0.5 V with a drain current of 14.5 µA. This mixer is suitable for ISM band applications with the centre frequencies at 2.4 GHz and 5.8 GHz. Current solutions exploit the worldwide license-free 2.4 GHz frequency band. Unfortunately, many applications nearly overcrowd this band such as high-power microwave ovens, cordless phones, Bluetooth and HomeRF applications, WLAN, game pads, etc. As a consequence, significant RF interference is present within the 2.4 GHz band [15]. Recently, wireless LAN system have been developed for the C-band (4~ 8 GHz) frequency. Proposals for wireless data system in the C-band range such as 5.8 GHz (Wireless LAN for U.S.A) and 5.2 GHz (Hyper LAN for Europe) have been submitted [16]. The license-free 5.8 GHz frequency band provides wider spectrum frequency. Furthermore, investigations are showed that 5 GHz applications in narrow surroundings can provide better performance than 2.4 GHz applications as the shorter wave length propagate farther. In addition, 5.8 GHz system nearly always will be operated at higher data rates than 2.4 GHz systems in form of bandwidth [17]. Mixer performance and behaviour in this two frequency bands is described and comparisons between values obtained from simulations carried out at two frequencies. Table1 shows the summary of chosen parameters to simulate the designed mixer in ADS. In order to evaluate the performance of the proposed mixer, the performance summaries of the previously reported CMOS mixers and this work are summarized in Table 2. The mixer’s figure-of-merit (FOM) can be expressed as [18] 10𝐶𝐺/20 × 10(𝐼𝐼𝑃3−10)/20 ). 10𝑁𝐹/10 × 𝑃 𝐹𝑂𝑀 = 10 log ( (6) where G and NF represent the conversion gain and noise figure in dB. The dc power consumption (P) and IIP3 are expressed in W and dBm, respectively. As can be observed, this work demonstrates the highest FOM of 37 dB in 2.4 GHz and 36.4 dB in 5.8 GHz RF frequency and the lowest supply voltage of 0.5 V and the lowest power consumption of 7.25 µW among all the CMOS mixers. Moreover, the supply voltage and dc power consumption of the proposed mixer is compatible with a 65-nm CMOS technology. 5. CONCLUSION An ultra low-voltage and low-power mixer using the TSMC 0.18-µm CMOS technology is presented in this paper. To substantially reduce the supply voltage and dc power consumption while other performance characteristics are maintained, the RF and LO stages in the proposed mixer are merged together, and subthreshold operation of MOS transistors is used. The supply voltage of this circuit is only 0.5 V and the dc power consumption is only 7.25 µW. Moreover, the proposed mixer is very suitable for 2.4 GHz and 5.8 GHz ISM band applications. REFERENCES [1] B. Bakkaloglu, P. Fontaine, A. N. Mohieldin, S. Peng, S. J. Fang, and F.Dülger, “A 1.5-V multi-mode quadband RF receiver for GSM/EDGE/CDMA2K in 90-nm digital CMOS process,” IEEE J. Solid- State Circuits , vol. 41, no. 5, pp. 1149–1159, May 2006. 5 [2] S.K. Hample, O. Schmitz, M. Tibebout, I. Rolfes, “Low-Voltage, Inductorless Folded Down-Conversion Mixer in 65 nm CMOS for UWB Applications” IEEE Radio Frequency Integrated Circuits Symposium, pp. 119-122, 2009. [3] H. S. Kang, S. G. Lee, B. G. Choi and C. S. Park, “A New Switching Technique for Low Power Mixer with Body Terminal,” IEEE, pp. 439-441, 2007. [4] C.-C. Tang, W.-S. Lu, L.-D.Van, and W.-S. Feng, “A 2.4-GHz CMOS down-conversion doubly balanced mixer with low supply voltage,” in Proc, IEEE Int. Symp. Circuits Syst. (ISCAS), May 2001, vol. 4, pp 794– 797. [5] C. Hermann, M. Tiebout, and H. Klar, “A 0.6-V 1.6-mW trans-former-based 2.5-GHz downconversion mixer with + 5.4-dB gain and -2.8 dBm IIP3 in 0.13-µm CMOS,” IEEE Trans. Microw. TheoryTech, vol. 53, no. 2, pp. 488–495, Feb. 2005. [6] L. Liu and Z. Wang, “Analysis and design of a low-voltage RF CMOS mixer,” IEEE Trans. Circuits Syst. II, vol. 53, no. 3, pp. 212–216, Mar.2006. [7] K.-H. Liang, H.-Y. Chang, and Y.-J. Chan, “A 0.5–7.5 GHz ultralow-voltage low-power mixer using bulkinjection method by 0.18-µm CMOS technology,” IEEE Microw. Wireless Compon. Lett. , vol. 17,no. 5, pp. 367–369, May. 2007. [8] C. Kienmayer, M. Tiebout, W. Simburger, and A . L .Scholtz, “A low power low–voltage NMOS bulk-mixer with 20 GHz bandwidth in 90nm CMOS ,” Proceedings of the IEEE Int. Symp. Circuits Syst, vol. 4, pp. 385– 388, May 2004. [9] D. Van Vorst and S. Mirabbasi, “Low-voltage bulk-driven mixer with on-chip balun,” IEEE International Symposium on Circuits and Systems, pp.456-459, May 2008. [10] D. J. Comer and D. T. Comer, “Operation of Analog MOS Circuits in the Weak or Moderate Inversion Region,” IEEE Trans.Education,VOL. 47, NO. 4, pp. 430-435, Nov.2004. [11] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, “Analysis and Design of Analog Integrated Circuits,” 4th ed. New York: Wiley, 2001, ch. 1. [12] M. J. Deen, R. Murji, A. Fakhr, N. Jafferali and W.L. Ngan, “Low-power CMOS integrated circuits for radio frequency applications,” IEE Proc.-Circuits Devices Syst., Vol. 152, No.5, pp. 509- 522,Oct 2005. [13] Lamb, K.G., San hez, S.J., and Holman, W.T., “A low noise operational amplifier design using subthreshold operation,”. 1997 Proc. of the 40th Midwest Symp. Circuits and Systems, Aug. 1997, Vol. 1, pp. 35–38 [14] Vincent Geffroy “RF mixers using standard digital CMOS 0.35µm process: IMS2001/RFIC2001 Technical Sessions, May 2001. [15] B. Alexander, and F. Smith, “WiFi (IEEE802.11b) and 2.4 GHz Wireless Telephone System”, White Paper, Cisco System., May 2001. [16] U. Lott, “Low DC power monolithic low noise amplifier for wireless application at 5 GHz,” IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium, pp. 81-84 (1998). [17] A. R. Othman et al., “ Single stage RF amplifier at 5.8 GHz ISM band with IEEE 802.11 a standard,” 2007 Asia-pacific-conference on applied electromagnetics proceedings, December 2007. [18] V. Vidojkovic, J. V. D. Tang, A. Leeuwenburgh, and A. H. M. V. Roer-mund, “A low-voltage foldedswitching mixer in 0.18-µm CMOS,” IEEE J. Solid-State Circuits, vol. 40, no. 6, pp. 1259 –1264, Jun. 2005. 6 Table 1. Summary of chosen parameters to simulate the proposed mixer in ADS Parameter VDD DC Power Consumption LO Frequency LO Power LO Input Impedance RF Frequency RF Power RF Input Impedance Value 0.5 V 7.25 µW 2.3/5.7 GHz 0 dBm 50 Ω 2.4/5.8 GHz -30 dBm 50 Ω IF Output Frequency 100 MHz 7 Table 2. Summary of the recently published low-power mixers and this work Ref. CMOS Technology (µm) RF frequency (GHz) SSB NF (dB) Gain (dB) IIP3 (dBm) IP1dB (dBm) [3] [5] [7] [8] This work This work 0.18 0.13 0.18 0.18 0.18 0.18 2.4 2.1- 3 0.5- 7.5 5.8 2.4 5.8 11 18 -15.2 14.8 5.4 -2.8 -12.5 15 5.7 -5.7 -16 28 3.4 11 0.9 13.3 12.4 -5 -19 14.6 10.2 -1 -13 Pdiss(µW) 500 1600 480 1000 7.25 7.25 VDD(V) FOM (dB) 1.8 23.2 0.6 9. 5 0.77 13.2 1 4. 2 0.5 37 0.5 36.4 8 Fig. 1. [12]. I-V curves of transistor 1 and transistor 2. 9 Fig. 2. Circuit schematic of the proposed mixer. 10 Fig. 3. Simulated conversion gain against W1-4. 11 Fig. 4. Simulated conversion gain against W5,6. 12 Fig. 5. Simulated conversion gain against VG1-4. 13 Fig.6. Conversion gain against LO power in 2.4 GHz. 14 Fig.7. Conversion gain against LO power in 5.8 GHz. 15 Fig. 8. IF output power against RF input power to determine IP1dB and IIP3 in 2.4 GHz. 16 Fig. 9. IF output power against RF input power to determine IP1dB and IIP3 in 5.8 GHz. 17 Fig. 10. Simulated noise figure against LO power in 2.4 GHz RF frequency. 18 Fig. 11. Simulated noise figure against LO power in 5.8 GHz RF frequency. 19 Fig. 12. Conversion gain against RF frequency in 2.4 GHz. 20 Fig. 13. Conversion gain against RF frequency in 5.8 GHz. 21