Sample3

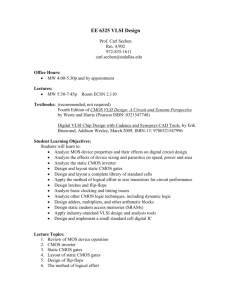

OBJECTIVE:

Seeking a position in CMOS IC Characterization

EDUCATION :

●

MSEE, CMOS design/VLSI, 2006

San Jose State University, GPA: 3.6/4.0

●

BSEE, Wireless Communications, 1998

Tehran University, GPA: 3.7/4.0

PROJECTS :

EXPERIENCE :

●

CMOS ALU design; designed a high speed, one GHZ, Four bit ALU, using CLA (carry look ahead) technique, schematics, simulations and layout, using Cadence software, DRC and

LVS.

●

CMOS PLL design; designed a high speed PLL, including Op Amps, Switches, Phase detector, Loop Filter and VCO.

●

CMOS Delta Sigma ADC design ; designed a high speed, one GHZ delta sigma ADC, including Modulator, Integrator and Comparator. Simulation using Cadence.

●

CMOS Pipeline ADC design; designed a high speed pipe line ADC using Op Amps, switches, Sample and hold, DAC. Schematics, Simulations and layout, using Cadence.

STEC Inc 2006 to present

Irvine, CA

Validation Engineer

●

Wrote an "IO meter” C++ code to measure the read and write performance of the Flash drive and secondary hard drives.

●

Wrote a BFC (Bit Flip Checker) C++ program to read two files as inputs and compare them and shows the number of differences.

●

Designed a File Generator project using C++ to get a number from user as input and generates a Random file with size of that number.

●

Failure analysis of compact flash cards down to the component level.

●

Interfaced with design engineering to resolve production and field issues.

TRIMBLE Navigation, 2004 to 2006

Sunnyvale, CA

Hardware Engineer

●

Designed an ARM7 based controller platform for controlling GPS radio systems.

●

Wrote C++ codes for ARM7 controller platform display

●

Designed ESD protection circuit for protection of GPIO and data buss

●

Complete Layout of the system using DXP and ALTIUM designer, including DRC and other

Error check methods.

●

Design and layout of the high speed traces using APCAD and other signal integrity simulation tools for High speed/RF trace layout

●

Test and characterization of Radio systems using Com Monitor, Analyzer and other RF equipments

SMART MODULAR Tech 2002 to 2004

Fremont CA

Characterization Engineer

●

Evaluation, test and characterization of the memory modules

●

Qualification and characterization of PLLs, Registers and DRAMs

●

Performed IBIS Simulations using Cadence SPECCTRA Quest tool for verification of electrical behavior of the logic components and Memories.

● Characterizing of the DIMMs, Clock Recovery and signal integrity

TELEPOINT Inc

Los Angeles, CA

2000 to 2002

Firmware Engineer

●

Assembly coding for Motorola 8051 Micro controller, programming and debugging.

●

Used ORCAD and PROTEL for Schematic drawings and PCB layouts

●

Troubleshot systems using Power-Meter, Oscilloscope and Multi Meters.

●

Performed board level design, simulation and PCB layout.

GD Aviation center 1998 to 1999

Tehran, Iran

Hardware Engineer

●

Designed a DF (Direction Finder) project using 8 bit ADC

● Wrote assembly codes for Motorola 8051 Micro controller to track aircraft’s positioning via communication dish antenna.