vlsi 90s

advertisement

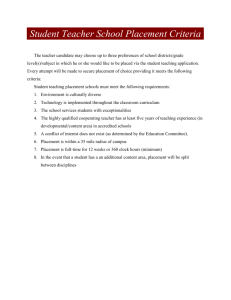

Chip Technology, Manufacturing and Design TECH – GENERAL ................................................................................................................................ 4 电工 ..................................................................................................................................................... 4 电路 ..................................................................................................................................................... 4 晶体管.................................................................................................................................................. 5 场效应管(MOS 管) ......................................................................................................................... 5 逻辑器件.............................................................................................................................................. 6 芯片 ..................................................................................................................................................... 6 集成电路............................................................................................................................................ 10 微处理器............................................................................................................................................ 11 MICROCONTROLLERS ............................................................................................................................... 11 处理器总线架构 ................................................................................................................................ 11 微电子技术........................................................................................................................................ 12 MATHEMATICS ................................................................................................................................ 14 PHYSICO-MATHEMATICAL MODELING......................................................................................................... 14 NUMERICAL SIMULATION ......................................................................................................................... 14 OPTIMAL DESIGN .................................................................................................................................... 15 编程语言 ......................................................................................................................................... 18 RESEARCH AND DEVELOPMENT ....................................................................................................... 20 PHYSICO-MATHEMATICAL MODELING......................................................................................................... 20 NUMERICAL SIMULATION ......................................................................................................................... 21 DESIGNS ........................................................................................................................................... 22 GENERAL ............................................................................................................................................... 22 DESIGN PROCESS OVERVIEW ...................................................................................................................... 22 DESIGN METHODOLOGIES ................................................................................................................. 24 DESIGN CONTENTS .................................................................................................................................. 25 ASIC/SOC DESIGN ................................................................................................................................. 27 SYSTEM SPECIFICATION ............................................................................................................................ 27 Specification ................................................................................................................................... 27 ARCHITECTURAL / BEHAVIORAL DESIGN....................................................................................................... 28 FUNCTIONAL DESIGN ............................................................................................................................... 29 LOGIC DESIGN ........................................................................................................................................ 29 Register Transfer Level (microarchitecture, block) ........................................................................ 29 Logic Simulation/ Synthesis ........................................................................................................... 30 CIRCUIT DESIGN ...................................................................................................................................... 31 PHYSICAL DESIGN .................................................................................................................................... 32 Flat design ...................................................................................................................................... 32 System partitioning ........................................................................................................................ 32 Floorplanning ................................................................................................................................. 33 Layout (placement and routing) .................................................................................................... 34 Global Placement / Detailed Placement ................................................................................................. 34 Routing in VLSI Design ............................................................................................................................... 37 Global Routing ...................................................................................................................................... 39 Detailed Routing ................................................................................................................................... 40 Maze routing ........................................................................................................................................ 42 Over the cell routing ............................................................................................................................. 42 Clock routing......................................................................................................................................... 42 TIMING OPTIMIZATION / CLOCKTREE GENERATION / CYCLE TIME AND SLACK OPTIMIZATION FOR VLSI–CHIPS / TIMING(PT-SI) ....................................................................................................................................... 43 IN-DESIGN SIGNOFF EXTRACTION(3D) ......................................................................................................... 45 POWER(PNA) ........................................................................................................................................ 45 THERMAL ANALYSES ................................................................................................................................. 45 SIGNAL INTEGRITY(SI) .............................................................................................................................. 45 CROSSTALK............................................................................................................................................. 45 MVSIM ................................................................................................................................................. 45 MVRC.................................................................................................................................................. 45 DFT ..................................................................................................................................................... 45 DFM .................................................................................................................................................... 45 ANTENNA DIODE ..................................................................................................................................... 45 DRC ..................................................................................................................................................... 45 LVS ACROSS ENTIRE CHIP .......................................................................................................................... 45 DESIGN AND SILICON VERIFICATION IC 验证 FORMAL VERIFICATION ................................................................ 46 IC MASK GENERATION PROCESS.................................................................................................................. 48 IC mask generation ........................................................................................................................ 49 Mask Compaction .......................................................................................................................... 49 FINAL CHECKS /版图控制 ...................................................................................................................... 49 DESIGN SOFTWARE EDA .......................................................................................................................... 50 EDA 仿真工具 – general ............................................................................................................... 50 综合工具 ....................................................................................................................................... 51 Virtual Platforms in System-on-Chip Design .................................................................................. 51 ASIC 的 EDA 工具 .......................................................................................................................... 52 DFT 工具 ........................................................................................................................................ 52 FPGA 平台 ..................................................................................................................................... 52 logic synthesis tools ....................................................................................................................... 52 The Research Institute for Discrete Mathematics of the University of Bonn ............................................ 53 数字芯片物理设计工具 ............................................................................................................... 53 形式验证工具 ............................................................................................................................... 54 物理验证工具 ............................................................................................................................... 54 时序验证工具 ............................................................................................................................... 54 版图设计工具软件 ....................................................................................................................... 54 通用设计工艺库 ........................................................................................................................... 54 VLSI CAD Conferences .................................................................................................................... 55 VLSI CAD Journals........................................................................................................................... 55 VLSI CAD Organizations ................................................................................................................. 55 PRODUCTION / FABRICATION TECHNOLOGY CAD (TCAD) ................................................................ 58 PACKAGING ..................................................................................................................................... 60 PACKAGE PHYSICAL DESIGN ...................................................................................................................... 60 PACKAGE MODELING ............................................................................................................................... 62 PACKAGE SIMULATION ............................................................................................................................. 62 TESTING ........................................................................................................................................... 63 SIMULATION .................................................................................................................................... 63 Tech – General 电工 电工 电工技术 电工原理 principles of electric engineering 电路 电路 Electrical circuit 模拟电路 analog electronics 数字电路 Digital circuit 电子电路 Electronic circuit 电路技术 电路设计 Circuit Design Digital Circuit Design 晶体管 晶体管 transistor 场效应管(MOS 管) Metal-Oxide-Semiconductor (MOS) Devices: 绝缘栅型场效应管(MOS 管) CMOS CMOS 电路制造的工艺流程,如:N 阱区光刻、N 阱离子注入、Si3N4 层淀积等; 场效应晶体管 MOSFET CMOS/BICMOS/BCD 基本器件结构 BIPOLAR Bipolar Transistors: BICMOS bipolar power junction transistors (BJTs) Junction Field Effective Transistor (JFET): 结型场效应管 IGFET insulated-gate field-effect transistor MISFET metal–insulator–semiconductor FET 增强型 PMOS、NMOS 耗尽型 PMOS、NMOS MOSFET transistors Discrete power MOSFETs 逻辑器件 通用可编程逻辑器件 Field Programmable Gate Arrays (FPGAs) Programmable Logic Devices (PLDs) LPGA (Laser Programmable Gate Array) 芯片 芯片 国内有多少芯片设计企业 Chips 芯片技术 Chip technology 电脑芯片 Computer chips 微芯片 Microchip digital signal-processing chips digital signal-processors media processors 移动芯片 基带及射频芯片 多频多模芯片 六模基带芯片 多模基带芯片 64 位 ARMv8 指令集的芯片 应用处理芯片 多核应用处理芯片 多集成单芯片 芯片设计 Chip design Chip designer Chip foundry Chip manufacturer 量子芯片 砷化镓量子芯片 量子芯片技术 D-Wave 处理器 Quantum chip quantum computing chip quantum relay chip integrated optical circuit on lithium niobate 量子计算 量子计算机 quantum computing Google quantum computer quantum communication quantum cryptography quantum information technology. Atom Chips 光子芯片 Google 1 硅光子芯片 硅基光子芯片 纳米线激光电脑芯片 Photonic Chip programmable quantum photonic chip CMOS Integrated Silicon Nanophotonics 用光束制造可擦写的电脑芯片的技术 能够用一束光重写并且改变电路图形,能够制造不同的电路以适应不同的需求 碳纳米管芯片 Plasmonics surface plasmon-polaritons (SPPs) 石墨烯芯片 铟芯片 砷芯片 镓芯片 自旋电子芯片 电子的自旋 自旋电子电路 interconnect solution: carbon nanotubes 生物芯片 基因芯片 DNA 芯片 相变存储技术 @@@@@@@@@@@@@@@@@@@@@@@@@ 集成电路 集成电路 IC SSI MSI 大规模集成电路 Large scale integration LSI 超大规模集成电路 Very large scale integration VLSI ULSI – Ultra Large Scale Integration WSI – Wafer Scale Integration ASIC – Application-Specific IC 集成电路设计 IC design 集成电路 IP 技术 集成电路的主要工艺技术,如:热扩散掺杂、离子注入、化学气相淀积、光刻、金属 化等; 集成电路的常用测试方法,如:设计错误测试、功能测试、圆片测试等; 集成电路的封装工艺及要求,如封装对散热性能的影响; 微处理器 微处理器 Microprocessor multi-core processors chip multi processors (CMP) The terms CPU, microprocessor (μP) and MPU (microprocessor unit) Harvard architecture Thumb® instruction set based on Thumb-2 technology MultiChip Modules (MCMs) Microcontrollers Microcontrollers MCU 环境 microcontroller unit (MCU) 处理器总线架构 Harvard Architecture Princeton Architecture SOC 总线架构 专用 PSoC(可编程片上系统) multiprocessor system-on-chip (MPSoC) silicon-on-insulator (SOI) System-in-Package (SiP) technology Networks-On-Chip (NoCs) nanoscale silicon photonic integrated circuitry photonic network-on-chip architecture Multiple Network-On-Chip Design ASIC 逻辑综合、DFT 等 ASIC 流程 ESL 解决方案 ASSP AMBA 总线 AMBA AHB/AXI 总线协议 Advanced Microprocessor Bus Architecture (AMBA) Advanced Extensible Interface (AXI) Arm,mips x86,atom 其中一种 CPU 架构 arm 体系 MIPS 微电子技术 微电子技术 Mathematics Physico-Mathematical Modeling Microscopic models Boltzmann-Poisson Wigner-Poisson model Macroscopic models energy transport hydrodynamic drift diffusion (DD) model Numerical Simulation black box optimization tools nonlinear least squares methods optimization theory optimal control of partial differential equations specially designed optimization algorithms Optimal Design Linear Algebra Discrete Mathematics Boolean algebra linear programming Integer Programming mixed integer programming Mixed Integer Linear Programming Dynamic programming Combinatorial optimization Combinatorial Optimization Combinatorial Optimization in VLSI Design Combinatorial analysis Chip technology has been chosen, logic design exists: �Global placement �Local placement �Global (homotopic) routing �Local routing �Layer assignment & via minimization Ordered binary decision diagram Switching function Multi-Objective Optimisation Local Search Metaheuristics Discrete Optimization Problems (DOP) greedy heuristic The NearestNeighborheuristic Linear Integer Program MixedIntegerPrograms –MIP Pure Integer Programs –IP, PIP 0-1 programs Algebraic combinatorics Graph theory and computer chip design graph theoretical modeling and analysis hypergraphs, graph partitioning, graph drawing, graph and geometric thickness, tree width, grid graphs, planar embeddings, and geometric graph theory netlist layout Steiner trees The (weighted) Steiner Tree Problem The Steiner Tree Packing Problem Szemer´edi Regularity Lemma Counting Lemma 3-graph Regularity Method k-uniform hypergraphs extremal graph theory Dijkstra Design and Analysis of Algorithms algorithmic computer science algorithms for linear and convex optimization Network flow algorithms Genetic Algorithm for VLSI Design GA for VLSI Design, Layout and Test automation- partitioning-automatic placement, routing technology, Mapping for FPGA- Automatic test generation- Partitioning algorithm Taxonomy-Multi way Partitioning. Advanced Algorithms in Genetic Algorithm Hybrid genetic – genetic encoding-local improvement-WDFR-Comparison of CasStandard cell placement-GASP algorithm-unified algorithm. differential equations �Compactification �logic simulation �runtime simulation submodular functions and matroids network flows and connectivity approximation algorithms and mathematical programming computational geometry and polyhedral combinatorics polyhedral techniques polyhedral combinatorics complexity theory probability theory NP Conpleteness 编程语言 Arm 汇编 dsp 编程 HDL VHDL VeriLog Unified Modeling Language(UML) Rosetta 语言 Research and Development Physico-Mathematical Modeling Numerical Simulation Designs General Math for Chips Math and Chips Math and Chips design Math and Chips industry Chip Mathematics Design process overview RTL Description Logic Synthesis Global Placement Timing Optimization Clocktree Generation Detailed Placement Global Routing Detailed Routing Final Checks Production VLSI Design Cycle (contd.) 1. System specification 2. Functional design 3. Logic design 4. Circuit design 5. Physical design Converts a circuit description into a geometric description. This description is used for fabrication of the chip. Basic steps in the physical design cycle: Partitioning Floorplanning and placement Routing Compaction 6. Design verification 7. Fabrication 8. Packaging, testing, and debugging The Process of VLSI Design Consists of many different representations/Abstractions of the system (chip) that is being designed. System Level Design Architecture / Algorithm Level Design Digital System Level Design Logical Level Design Electrical Level Design Layout Level Design Semiconductor Level Design (possibly more) 电路设计 器件物理 工艺技术 材料制备 自动测试 封装 组装 芯片设计需要经过大致的几个阶段: 前期准备阶段(对于标准的理论研究、芯片实现的算法研究、计算机仿真、 FPGA 验 证)、 芯片设计和生产阶段(布图、布线、芯片工艺设计、芯片流片、芯片评估和测试)、 芯片验证和产品推出阶段(通过在各种类型整机上对芯片进行充分验证)。 编译 前仿真 后仿真 综合 约束 静态时序分析 形式验证等 常用的工具有 Synopsys 的 VCS,DFT,PC,Mentor 的 modelsim,Cadence 的 Synplify 等等。 EDA 工具 FPGA 验证阶段 DESIGN METHODOLOGIES Full Custom Design Direct control of layout and device parameters Longer design time but faster operation more dense Standard Cell Design Easier to implement Limited cell library selections Gate Array or Programmable Logic Array Design Fastest design turn around Reduced Performance Field Programmable Gate Array FPGA Circuit integration through lattice hyperterms distributive lattices Design Contents 芯片解决方案和参考设计 SOC 芯片的参考设计,从规划到设计到量产验证的过程 SoC 芯片完整设计流程,从规划到设计到量产验证; SoC 芯片的总线架构/memory 架构/时钟树/电源域的设计与仿真 SoC 芯片的总线架构/memory 架构/时钟树/电源域设计与仿真 CPU 内核架构设计/ARM CPU core 集成与优化/memory 优化相关项目经验 多核并行处理/ASMP/SMP/多核异构计算/并行编译相关项目经验 GPU 架构设计/游戏引擎优化 芯片系统建模(ESL)或系统带宽分析 芯片前端(综合,STA) 后端(floorplan,CTS)流程 反馈架构 设计优化 芯片量产低功耗和性能优化 外设子系统及其常用接口设计,比如 USB,EMMC,SDIO,SPI,I2C,URAT; Full-custom ASIC Cell-based ASIC Gate array Programmable logic Field programmable gate array (FPGA) Programmable logic device (PLD, PLA, PAL, ...) Complex PLD (CPLD) SoC, SoPC System-on-Package (SoP) or System-in-Package (SiP) System-on-a-Programmable Chip (SOPC) IC Design product definition design, layout, evaluation, release production ASIC/SOC Design RTL design & integration, functional verification, synthesis(DCT) and formal verification, FPGA emulation and design for testability. Place & route: design planning, placement and optimization, clock tree synthesis, routing, DFM, Clock Reconvergence Pessimism Removal(CRPR), power optimization and low-power flow with UPF. Signoff with PrimeTime SI, StarRC, On-Chip Variation (OCV), MCMM, MVSIM, MVRC, formal verification, DFT, ANT, DRC & LVS. and also offer aggressive development schedules by reducing time to market – and time to profit for our customer needs. Package design:package interface simulation, thermal analysis. Asynchronous Techniques for System-on-Chip Design System Specification Specification Specification and High-Level Design Functional Design Behavioral Functional (architecture) Prelayout Simulation Hardware Description Languages Verilog, VHDL PROCESS SELECTION System modeling The concepts in the designer’s mind are captured as a set of computational operations and data dependencies subject to constraints on timing, chip area, etc. Architectural / Behavioral Design Behavioral VHDL VHDL, C Verilog HDL Synthesis: Top-Down Design Requirements Analysis System Partitioning Behavioral/Functional Specification Behavioral/Functional Verification Synthesis & Optimization Gate Level Verification Functional Design Functional Design. The resources that can implement the system’s operations are identified, and the operations are scheduled. As a result, the control logic and datapath interconnections are also identified. Functional design is also called highlevel synthesis. Logic Design Logic synthesis. The high-level specification is transformed into an interconnection of gate-level boolean primitives — nand, xor, etc. The circuit components that can best realize the functions derived in functional design are assembled. Circuit delay and power consumption are considered at this step. The output description of the interconnection between different gate-level primitives is usually called a netlist. Register Transfer Level (microarchitecture, block) RTL Level Design RTL Description rtl 设计 RTL 级 Gate 级 Logic Simulation/ Synthesis Logic Synthesis Logic Synthesis High-Level Synthesis (HLS) Simulation Logic Design Netlist apply a recently-developed algebraic concept and a combinatorial scheme for logic synthesis. Recent developments in lattice theory, and particularly the concepts of lattice hyperterms and lattice hyperidentities give a new perspective to the optimization of logic circuits. to find an equivalent hypercircuit combinatorial optimization and integer programming reliability theory Circuit Design Physical Design Physical design. The actual spatial layout of circuit components on the chip is determined. The objectives during this step usually include total wirelength, maximum signal propogation time (“performance”), etc. Physical design can be further divided into steps including partitioning, floorplanning, placement, and routing Evolutionary Algorithms for the physical design of VLSI circuits Multiscale Optimization in VLSI Physical Design Automation Flat design System partitioning Flow-based partitioning netlist Min-cut Partitioning circuit partitioning five components of netlist layout partitioning the netlist, leveraging the hierarchy, identifying congestion, measuring congestion, and automating small configurations. Netlist partitioning The process of converting a netlist into the physical design of a chip is traditionally broken into three phases: floorplanning, in which the very large and “special” functional elements are assigned locations in the chip area; placement, in which the remaining functional elements are assigned locations in the chip; and wiring or routing, in which the interconnect wires are assigned locations. Kernighan-Lin (KL) Algorithm Floorplanning The floorplanning stage ensures that (1) every chip module is assigned a shape and a location, so as to facilitate gate placement, and (2) every pin that has an external connection is assigned a location, so that internal and external nets can be routed. Floorplanning also decides the IO structure, aspect ratio of the design. Floorplan models can be classified in two categories: a) slicing floorplans and b) nonslicing floorplans. Hierarchical Floorplanning: Bottom-up clustering Top Down Placement Floorplan Optimization Floorplan Sizing: Minimum-area floorplan: Cluster Growth: Linear ordering: Layout (placement and routing) Global Placement / Detailed Placement Detailed Placement global placement algorithm Lagrange multipliers Global Placement Timing Optimization SIMPLIFIED PLACEMENT PROBLEM QUADRATIC ASSIGNMENT PROBLEM quadratic placement and multisection conjugate gradient method with incomplete Cholesky pre-conditioning HITCHCOCK TRANSPORTATION PROBLEM Macro placement uses minimum cost flow, branch-and-bound, and greedy techniques. PLACEMENT LEGALIZATION PROBLEM net model bb steiner mst clique star Quadratic Assignment Problem Placement methods can be classified roughly into three categories: recursive minimum cut placement, analytical placement and local search methods. Manhattan distance Global Placement Placement approaches in practice simulated annealing: start with any placement and try to improve it (mostly used in the 80s) min-cut: successive bisection, with simple exchange heuristics (mostly used in the 90s) analytical placement: minimize either linear or quadratic netlength estimate, then work towards disjointness (dominant strategy today) slack, Lagrange multipliers minimum cost flow problem Quadratic placement (QP) local search Global Placement by successive partitioning Remove overlaps by successive quadrisection Fractional relaxation: Hitchcock (transportation) problem Successive shortest path algorithm quadratic, partitioning based placement algorithm simulated-annealing quadratic or force-directed min-cut nonlinear programming PROUD: A SEA-OF-GATES PLACEMENT ALGORITHM GENERIC GLOBAL PLACEMENT AND FLOORPLANNING (KRAFTWERK) FASTPLACE: EFFICIENT ANALYTICAL PLACEMENT USING CELL SHIFTING, ITERATIVE LOCAL REFINEMENT AND A HYBRID NET MODEL Recent advances in placement algorithms include (i) high-performance wirelengthdriven placement, (ii) mixed-sized placement (i.e., simultaneous placement of both cells and macros), (iii) routability-driven placement, (iv) timing- and power-driven placement, as well as (v) the integration of global placement into physical synthesis. VLSI Placement by Quadratic Programming and Slicing Optimization new placement method based on simultaneous quadratic programming combined with improved partitioning schemes and exhaustive slicing optimization seaof-gates design systems min-cut placement procedure for sea-of-gates circuits macrocell circuit standard cell circuits weighted estimated wiring length Manhattan-metric minimum spanning trees simulated annealing Analytical placement netlength linear and quadratic netlength straight-line embeddings of planar graphs combine algorithms for minimizing netlength with recursive partitioning wirelength shortest rectilinear Steiner tree connecting the pins multisection netlists Linear Placement 2D Placement Placement and Routing with Standard Cells Placement Objective Functions Routing in VLSI Design The Routing Problem Apply after placement Input: Netlist Timing budget for, typically, critical nets Locations of blocks and locations of pins Output: Geometric layouts of all nets Objective: Minimize the total wire length, the number of vias, or just completing all connections without increasing the chip area. Each net meets its timing budget. fully automatic routing of densely packed boards is a goal difficult to achieve. Even showing the existence of a feasible routing is NP-complete routing global routing detailed routing integer linear programming formulation approximation algorithms for min-max resource-sharing problems block problems and virtual layer method sequential routing maze runner buffering, repeater-tree topologies, floorplanning Final Checks Production network flows, min-cost flows, multi-commodity flows, Multicommodity flow formulation shortest path, Steiner-Tree design, Steiner tree problems Steiner tree packing clustering, facility location, min-max resource sharing, matching, quadratic optimization. Undirected partitioning formulation Interconnect Synthesis simultaneous routing Over The Cells (OTC) routing Hierarchical routing sequential routing Tile Expansion Shortest Path router XRouter "net ordering" "rip-up & re-route" techniques wire sizing and spacing Signal integrity Elmore delay technique Global Routing Global routing is divided into 3 phases: 1. Region definition 2. Region assignment 3. Pin assignment to routing regions Multicommodity Flow Algorithms fractional multi-commodity flows Combinatorial fully polynomial approximation schemes Min-max resource sharing contract regions of approximately 50x50 tracks to a single vertex compute capacities of edges between adjacent regions pack Steiner trees with respect to these edge capacities global optimization of objective functions Steiner tree yields detailed routing area for each net Detailed routing computes the detailed wires in these areas by a very fast goal-riented interval-labeling variant of Dijkstra’s algorithm (Peyer, Rautenbach, Vygen [2009]) Global routing: classical problem formulation Instance: a global routing (grid) graph with edge capacities a set of nets, each consisting of a set of vertices (terminals) Task: find a Steiner tree for each net such that the edge capacities are respected, and (weighted) netlength is minimum. sequential routing Maze Runner heuristic concurrent routing integer programming multi-commodity network flow problem Detailed Routing In the detailed routing problem our task is to interconnect certain given subsets (or nets) of the pins (or terminals) of these devices by wires. To sum it up from a graph-theoretical viewpoint, the detailed routing problem consists of finding vertex-disjoint Steiner-trees (trees with a given terminal vertex set) in a 3-dimensional rectangular grid. Sequential routing integer programming formulation called Integer Programming Based Approach parallel routing parallel multi-threaded collision-aware global router based on Maze Routing Algorithm using a heuristic collision-prevention approach. Parallel VLSI Detailed Routing Parallelization of VLSI routing algorithms prim’s algorithm Channel routing Full-chip routing Multilevel Full-Chip Routing switchbox routing in the Manhattan model single active layer routing problem maze routing VLSI Maze routing using GPGPU General-Purpose computing on Graphics Processing Units (GPGPU) line probe routing left-edge routing greedy channel scanning multilayer router called NEMO Hierarchical Routing Dogleg Channel Router Over-the-Cell Routing Maze searching Line searching Routing Grid Models Grid-based model: A grid is super-imposed on the routing region Wires follow paths along the grid lines Pitch: distance between two gridded lines Most commonly used Gridlessmodel: Any model that does not follow this “gridded” approach Routing Layer Models Unreserved layer model Any net segment is allowed to be placed in any layer Reserved layer model Certain type of segments are restricted to particular layer(s) Maze routing Given: A planar rectangular grid graph. Two points S and T on the graph. Obstacles modeled as blocked vertices. Objective: Find the shortest path connecting S and T. This technique can be used in global or detailed routing (switchbox) problems. Over the cell routing Clock routing Timing Optimization / Clocktree Generation / Cycle Time and Slack Optimization for VLSI–Chips / timing(PT-SI) Clocktree Generation clock-tree design, clock tree design clock tree synthesis clock skew scheduling optimizing the clock skews clock period optimization timing, timing optimization fanout tree design gate sizing timing graph arrival time at input of the chip arrival time at output of the chip arrival time at register of the chip netlist a netlist is a hypergraph on the set of pins, such that each pin is in exactly two hyperedges (a gate and a signal), together with the delay information. hypergraph partitioning optimal netlist partitioning is unfeasible graph and hypergraph partitioning algorithms such as METIS and hMETIS graph regularity lemma clock schedule optimal arrival times for clock signals cycle time data paths and clocktree paths. test for negative circuits in a digraph as a subroutine direct combinatorial algorithm timing analysis transparent latches. slack balancing problem routing detours process variations manufacturing skew critical paths optimum slack distribution fixed clock arrival times slack on clocktree paths simultaneous optimization of slacks on all data paths and clocktree paths network optimization algorithms parametric shortest paths linear programming binary search the algorithm of Young, Tarjan and Orlin ================================== l1-metric is the right metric for wire length to find disjoint sets of wires for all nets - vertex disjoint Steiner trees the bounding box model BB net models : STEINER MST CLIQUE STAR in-design signoff extraction(3D) power(PNA) thermal analyses signal Integrity(SI) crosstalk Mvsim MVRC DFT DFM antenna diode DRC LVS across entire chip Design and Silicon Verification IC 验证 formal verification RTL, timing analysis, physical verification, testability analysis, test vector generation FPGA based Emulation and Validation. Resolve critical issues in signal integrity, cross-talk, power, performance, Design for test (DFT), package design and simulation. Processor subsystem design and implementation, design for manufacturability (DFM) and signal integrity (SI) techniques to eliminate any problems before you commit to silicon. Stress test, test coverage analysis, device characterization and qualification across the full range of process parameters, process tuning and yield ramp along with package, test and production support. 芯片认证相关标准及流程,如 AEC-Q100 等; 硬件设计语言 HDL Verilog Verilog HDL 语言 硬件验证语言 System Verilog SystemC 验证方法学 VMM OVM UVM 测试机 J750、V50 等 ATPG 和测试向量 Verification Techniques and Tools Testing vs. Verification – Verification and Design Reuse - Functional Verification, Timing Verification, Formal Verification, Linting Tools – Simulators – Third Party Models – Waveform Viewers – Code Coverage issue – Tracking Metrics. Verification Plan Verification plan – Levels of Verification – Verification Strategies – Specification Features – Test cases – Test Benches. Stimulus and Response Simple Stimulus – Output Verification – Self Checking Test Benches – Complex Stimulus and Response – Prediction of Output. Architecting Test benches Reusable Verification Components – VHDL and Verilog Implementation – Autonomous Generation and Monitoring – Input and Output Paths – Verifying Configurable Design. System Verilog Data types, RTL design, Interfaces, clocking, Assertion based verification, classes, Test bench automation and constraints. IC mask generation process IC mask silicon compiler mixed integer linear programming problem user defined stick diagram dimensionless topological representation of IC layout branch and bound method longest path algorithm on acyclic graphs symbolic layout methods the fixed grid method the relative grid method IC mask generation automatic IC mask generation Mask Compaction Final Checks /版图控制 Design Software EDA EDA 仿真工具 – general VCS NC NCverilog DC Synposys Modesim Verdi Cadence HSPICE SPECTRE Caliber Protel Mentor MMSIM7 Spectre/SpectreRF, ADS 等 PADS ALLEGRO VIEWDRAW 综合工具 DC, RC 或其它 Virtual Platforms in System-on-Chip Design Virtual platform tools providers Synopsys Carbon Design Systems Imperas /OVP (Open Virtual Platform) Mentor / Catapult C MathWorks /EDA Simulator Link tool CoFluent Studio design companies ARM Tensilica Qualcomm Samsung ST Microelectronics Freescale Infineon Technologies standards SystemC Transaction-level modeling (TLM) IP-XACT ASIC 的 EDA 工具 DesignCompiler、PrimeTime、Formality、Ncverilog、VCS 等 DFT 工具 MBIST, DFT COMPILER, TESTKOMPRESS 或其它 FPGA 平台 FPGA 的 EDA 工具 Synplify、QuartusII、ISE 及 Modelsim、Questasim 等 FPGA 和 CPLD 开发工具,如; Maxplus II、Quartus 等; FPGA 综合布线工具 Synplify logic synthesis tools Logic synthesis tools take the register transfer-level HDL description and convert it to an optimized gate-level netlist RTL-based synthesis is currently the most popular design method High-Level Synthesis (HLS) tools HLS tools work by taking applications written in a subset of ANSI C, and translating it into a Register Transfer Level (RTL) module for Application-Specific Integrated Circuit (ASIC) or Field Programmable Gate Arrays (FPGAs) chip design. Xilinx Virtex-5 FPGA platform Synfora Inc the HLS tool called PICO, Synopsys ynphony C Compiler AutoESL Catapult C The Research Institute for Discrete Mathematics of the University of Bonn BonnTools, are widely used in industry. More than 1500 highly complex chips have been designed by BonnTools. Chip design is a very fascinating and highly important area of application of mathematics. 数字芯片物理设计工具 Synopsys, Cadence 或 Magma 等 形式验证工具 FORMAL, CONFORMAL 或其它 物理验证工具 熟练使用 Calibre 等 时序验证工具 PT 等 静态时序分析工具(PRIMETIME, ETS 或其它) 版图设计工具软件 Virtuoso 及 laker PCB 版图绘制工具 Allegro/OrCAD,或 Protel 通用设计工艺库 TSMC/IBM/JAZZ/SMIC VLSI CAD Conferences ACM/IEEE Design Automation Conference (DAC) International Conference on Computer Aided Design (ICCAD) IEEE International Symposium on Circuits and Systems (ISCAS) International Conference on Computer Design (ICCD) IEEE Midwest Symposium on Circuits and Systems (MSCAS) IEEE Great Lakes Symposium on VLSI (GLSVLSI) European Design Automation Conference (EDAC) International Conference on VLSI Design VLSI CAD Journals IEEE Transactions on CAD of Circuits and Systems Integration Transactions on Circuits and Systems Journal of Circuits, Systems and Computers Algorithmica SIAM journal of Discrete and Applied Mathematics IEEE Transactions on Computers VLSI CAD Organizations ACM SIGDA Design Automation Technical Committee (DATC) of IEEE Computer Society Production / Fabrication Technology CAD (TCAD) Crystal Growth, Wafer Preparation, Epitaxy and Oxidation Electronic Grade Silicon, Czochralski crystal growing, Silicon Shaping, processing consideration, Vapor phase Epitaxy, Molecular Beam Epitaxy, Epitaxial Evaluation, Growth Mechanism and kinetics, Thin Oxides, Oxidation Techniques and Systems, Oxide properties, Redistribution of Dopants at interface, Oxidation of Poly Silicon, Oxidation induced Defects. Lithography and Reactive Plasma Etching Optical Lithography, Electron Lithography, X-Ray Lithography, Ion Lithography, Nano imprint Lithography, Plasma properties, Feature Size control and Anisotropic Etch mechanism, reactive Plasma Etching techniques and Deposition, Diffusion and Ion Implantation Deposition process, Polysilicon, plasma assisted Deposition, Models of Diffusion in Solids, Fick’s one dimensional Diffusion Equation - Measurement techniques - Range theory- Implant equipment – Annealing- Shallow junction, High - energy implantation. Metallization and VLSI Process Integration Physical Vapour Deposition (PVD) –Patterning- NMOS IC Technology – CMOS IC Technology – BICMOS IC Technology- MOS Memory IC technology - Bipolar IC Technology –Silicon on Insulator Technology–Noise in VLSI Technologies Packaging Analytical, Assembly Techniques and Packaging of VLSI Devices Analytical Beams – Beams Specimen interactions - Chemical methods – Package types – packaging design consideration – VLSI assembly technology – Package fabrication technology. Packaging styles WSI MCM PCB Package Physical Design ISQED’05 9 Typical Package Design Cycle Package/Substrate Architecture Exploration (start ~4/5 months before Tapeout) Package/Substrate Architecture Exploration (start ~4/5 months before Tapeout) Defining Interfaces, Signals, PLL, Power, Clock, # pins, # IOs Defining Interfaces, Signals, PLL, Power, Clock, # pins, # IOs Manufacturing and NRE Costs; Die, Substrate, Package Manufacturing and NRE Costs; Die, Substrate, Package Floorplanning of IO/Pad/Pins; Define Netlist hierarchy/manipulations Floorplanning of IO/Pad/Pins; Define Netlist hierarchy/manipulations Pad/package Iteration: P&R of IO/Pad cells, Pins; Pwr/gnd and inter-cell connections; PCB pin locations (x,y); Pad/package Iteration: P&R of IO/Pad cells, Pins; Pwr/gnd and inter-cell connections; PCB pin locations (x,y); Package/Pad/IO Rule checking (PRC): SI, timing, clocks, IO voltages, assembly rules, special regions Package/Pad/IO Rule checking (PRC): SI, timing, clocks, IO voltages, assembly rules, special regions Verify user specified requirements and rules; PCB pins, Power grid, # VSS/VDD, decoupling caps, EMI, ESD, Vias Verify user specified requirements and rules; PCB pins, Power grid, # VSS/VDD, decoupling caps, EMI, ESD, Vias Finalize IOs/Pads/Pins; Package Tapeout Package Modeling Package Simulation Testing Genetic Algorithm for VLSI Testing Global routing-FPGA technology mapping-circuit, generation-test generation in a GA frame work-test generation procedures. Simulation Postlayout simulation